导读:

7系列FPGA包含最多24个CMT块,CMT具体的分布和与其他时钟资源的关系请参考本合集(FPGA应用开发)的上一篇文章。本文主要介绍CMT内部MMCM和PLL的区别以及在实际开发中怎么使用CMT,怎么实现跨时钟区域,第一次读者最好先阅读上一篇文章——解剖时钟结构篇。

MMCM和PLL的区别

在xilinx 7系列FPGA中,时钟管理块(CMT)包括混合模式时钟管理器(MMCM)和锁相环(PLL)。MMCM和PLL可用于广泛范围频率的频率合成器,用作外部或内部时钟的抖动滤波器,并用于去斜时钟。

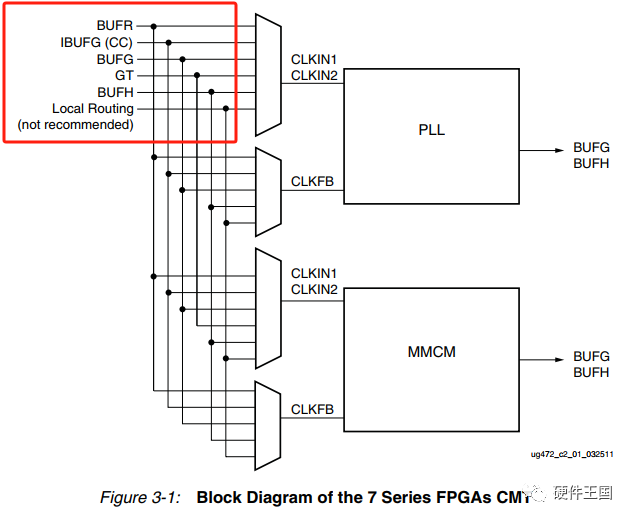

下图显示了各种时钟输入源与MMCM/PLL之间连接的高层次视图。在7系列FPGA中,时钟输入允许多个资源(如红框所示)提供参考时钟给MMCM/PLL。

PLL与MMCM的区别:

在CMT中,PLL是MMCM功能的一个子集。PLL主要用于频率合成,但不支持MMCM的一些高级功能,如直接连接到HPC(高性能时钟)或BUFIO(缓冲器输入输出)等。MMCM是7系列FPGA中用于时钟管理的核心。简单来说PLL适用于较简单的时钟管理需求,而MMCM提供了更多高级功能,适用于更复杂的时钟管理场景。其中MMCM支持的附加功能主要包括:

- 使用CLKOUT[0:3]直接连接到HPC或BUFR或BUFIO。

- 反相时钟输出(CLKOUT[0:3]B),即支持差分输出。

- CLKOUT6(相比PLL多一路输出)。

- CLKOUT4_CASCADE(级联输出,允许将一个 MMCM 的输出连接到另一个 MMCM 的输入)。

- CLKOUT0_DIVIDE_F的分数分频(用于进行时钟频率合成时的分数分频,非整数倍时钟频率的设计有用)

- CLKFBOUT_MULT_F的分数倍频(用于进行时钟频率合成时的倍频设置)

- 微调相移

- 动态相移

PLL和MMCM内部结构就不再这里详述了,大家知道怎么用就足够了,感兴趣的读者可以参考xilinx原文档。

Clock IP和原语

怎么使用CMT?工程中可以选择IP即预设计的时钟管理模块,也可以选择原语硬件描述语言(如VHDL或Verilog)中的代码自定义时钟管理。

选用IP使用简单,有图形用户界面(GUI),可以通过可视化的方式配置参数,如下图所示。

选用原语,自定义代码可以更好地控制硬件资源的利用,减小资源占用。对于经验较丰富的开发者,使用原语可能更为灵活;而对于初学者,使用IP更容易上手。

Clock IP:可选择MMCM还是PLL

MMCM和PLL 原语

注:

MMCME2_BASE原语提供了对独立MMCM的最常用功能的访问。时钟去斜、频率合成、粗略相移和占空比编程都可以与MMCME2_BASE一起使用。MMCME2_ADV原语提供对所有MMCME2_BASE功能的访问,以及用于时钟切换、访问动态重配置端口(DRP)以及动态精细相移的额外端口。PLL类似,不再细述。

实际用例

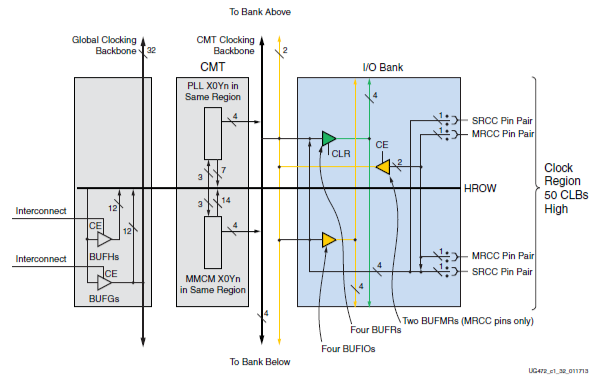

xilinx原文档有描述,在不使用其他原语的情况下,进入器件的时钟信号(通过CCIO引脚)只能驱动同一时钟区域内的BUFR或BUFIO。如果要驱动其他时钟区域的逻辑则必须使用BUFMR原语,BUFMR原语是一种多区域时钟缓冲器,允许输入访问进入器件的时钟信号所在时钟区域上方和下方的BUFR和BUFIO。BUFMR可以跨越多个时钟区域。每个时钟区域中有两个BUFMR。

然而,在某些情况下,我们可以通过经过MMCM和BUFG等元素来实现跨时钟区域的时钟分配。BUFMR主要用于驱动多个时钟区域的一种特定情况,这是一种确保最小时钟偏移和时钟抖动的方法。因为它专为跨时钟区域提供时钟信号设计。

case1:使用BUFMR跨时钟区域

外部时钟从MRCC引脚(注:通过BUFMR跨多个时钟区域时,只能从MRCC引脚,SRCC引脚为单时钟区域,不过也可以使用GT时钟)送至BUFMR原语,然后BUFMR被多个BUFR或BUFIO驱动的逻辑分组为(最多三个)子集,每个子集都有一个独立的BUFR或BUFIO。使用Vivado设计工具对设计进行布局和约束,以便将逻辑分配给各个BUFR和BUFIO。

case2:使用BUFG和MMCM跨时钟区域

外部时钟从CCIO引脚(MRCC或SRCC)送至BUFG(单端时钟)或IBUFGDS(差分时钟),经过MMCM合成消抖后再连至BUFG,此时BUFG输出时钟则是全局时钟,实现了跨时钟区域的时钟分配。

-

FPGA

+关注

关注

1628文章

21702浏览量

602636 -

锁相环

+关注

关注

35文章

583浏览量

87722 -

Xilinx

+关注

关注

71文章

2165浏览量

121150 -

pll

+关注

关注

6文章

775浏览量

135089 -

时钟

+关注

关注

10文章

1727浏览量

131422

发布评论请先 登录

相关推荐

XILINX FPGA IP之MMCM PLL DRP时钟动态重配详解

Xilinx 7系列FPGA的时钟结构解析

请问如何设置动态和实时改变Artix FPGA中MMCM时钟的相移?

Xilinx 7系列FPGA管脚是如何定义的?

Xilinx 7系列与Ultrascale系列FPGA的区别

Xilinx 7系列FPGA PCIe Gen3的应用接口及特性

Xilinx 7系列FPGA中MMCM和PLL的区别

Xilinx 7系列FPGA中MMCM和PLL的区别

评论