点击上方蓝字关注我们

第一节:fifo基础

内容:

1.掌握FPGA设计中关于数据缓存的使用

2.掌握FIFO工作原理

1.1片上存储(on-chip ram)

在实际应用中任何场合都离不开数据,只要有数据的地方就有存储器,一般存储分为了2种,一种时可以读写,一种时只读。

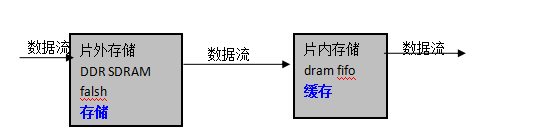

对于芯片设计而言,有的存储器时集成在芯片内部,我们称之为片内存储器,on-chip ram,如果使用芯片以外的存储器芯片,我们称之为片外存储器,从应用角度可以将存储分为片上和片外。

如果数据量较小,可采用片内存储器,因为片内存储器存储的数据量较小,如果数据量大则需要片外存储器。

根据实际情况应用,片上存储器一般作为数据缓存使用,真正用来存储数据选择片外存储器。

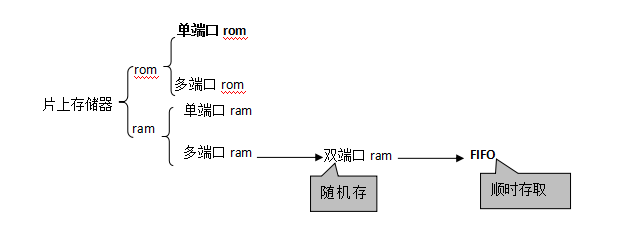

1.2片上存储器分类

1.3fifo

fifo是片上存储器的一种,它本质上是双端口ram的一种特殊结构,数据存储时顺存取。

信号名 | 描述 | 信号名 | 描述 |

wr_clk | 写时钟 | rd_clk | 读时钟 |

wr_en | 写使能 | rd | 读使能 |

wrdata[w-1:0] | 写数据 | rddata[R-1:0] | 读数据 |

full(地址) | 存储器空间操作 | empty(地址) | 存储器空间操作 |

1.随机读写

不管读写可以选择空间地址

同一地址允许覆盖(当我们往同一个地址多次写入数据的时候,后面一次操作覆盖掉前一个操作的数据)

同一地址空间无释放(当我们从同一个地址多次读出数据的时候,数据一直有效)

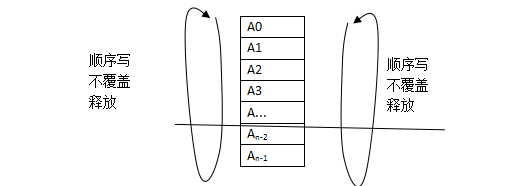

2.顺序读写

读写空间按照顺序存储器

同一地址不允许覆盖(当我们往同一个地址多次写入数据的时候,低一次写入后,后面所有的写操作都是无效)

同一地址空间释放(当我们从同一个地址多次读出数据的时候,当第一次读完数据,之后数据无有效)

1.3工作原理

根据FIFO顺序读写操作特性,我们可以看出写操作永远快于读操作,如果空间被写完,读写地址相同,空间全部被释放掉,读写地址相同

1.4空间判断

假如空间大小为dept=N,则写地址wraddr[log2N-1:0] , 读地址rdaddr[log2N-1:0]

如果我们将读写地址扩1位,则则写地址wraddr[log2N:0], 读地址rdaddr[log2N:0]

当wraddr[log2N-1:0] == rdaddr[log2N-1:0]

wraddr[[log2N] != rdaddr[log2N]说明写地址追上读地址 | rdaddr[log2N-1:0] - wraddr[log2N-1:0] | = N

wraddr[[log2N] == rdaddr[log2N]说明读地址追上写地址 | rdaddr[log2N-1:0] - wraddr[log2N-1:0] | = 0

例如depth =4

000 100

001 101

010 110

011 111

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA威廉希尔官方网站 交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:FPGA学习-异步FIFO原型设计与验证

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1628文章

21711浏览量

602735

原文标题:FPGA学习-异步FIFO原型设计与验证

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FIFO Generator的Xilinx官方手册

数字芯片设计验证经验分享文章 实际案例说明用基于FPGA的原型来测试、验证和确认IP——如何做到鱼与熊掌兼

解锁SoC “调试”挑战,开启高效原型验证之路

FPGA算法工程师、逻辑工程师、原型验证工程师有什么区别?

FPGA异步信号处理方法

大规模 SoC 原型验证面临哪些威廉希尔官方网站 挑战?

同步FIFO和异步FIFO区别介绍

FPGA学习-异步FIFO原型设计与验证

FPGA学习-异步FIFO原型设计与验证

评论