前言

本次总结为中断和定时器的相关内容。除了基本的寄存器配置,初始化,中断主要是掌握三级中断制,定时器主要关注定时器的工作原理和中断时间的设置。

时钟

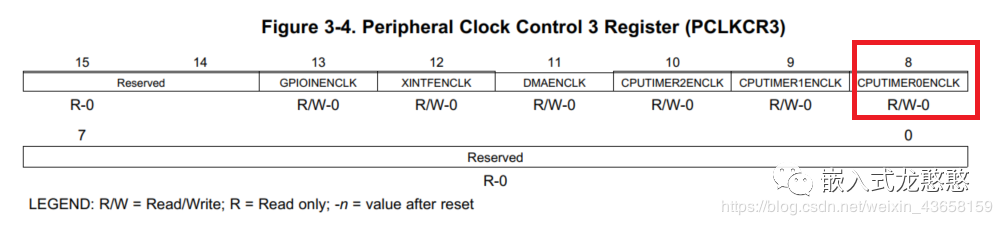

定时器时钟使能为外设时钟控制寄存器PCLKCR3的第8位。

SysCtrlRegs.PCLKCR3.bit.CPUTIMER0ENCLK = 1; // CPU Timer 0

1 中断

F28335内部有16个中断线,分别是:

1、2个不可屏蔽中断:RESET、NMI;

2、14个可屏蔽中断:INT1-INT12,外部中断和内部单元使用;INT13和INT14 预留给实时操作系统。

当前主要学习INT1-INT12这12 个中断。

CPU级中断有12个中断线(INT1-12),通过PIE控制器进行复用管理,将外设中断分成12组,每一组有8个外设级中断组成,共有96个外设级中断,分别对应相应外设接口的中断引脚,实际有效外设中断为58个,其余为保留。

1.1 三级中断制:

三级中断制:

外设级中断 ——> PIE级中断 ——> CPU级中断

使用中断时主要需要注意各级中断的标志、使能、应答寄存器,具体如下图的标号所示:

外设级: IF、IE;

PIE级: PIEIFRx、PIEIERx.y、PIEACK;

CPU级: IER、IFR、INTM。

见Figure6-6。

一般当有中断请求时,IF和IFR等寄存器是硬件自动置位,IE和IER等寄存器是软件使能。

中断的过程:

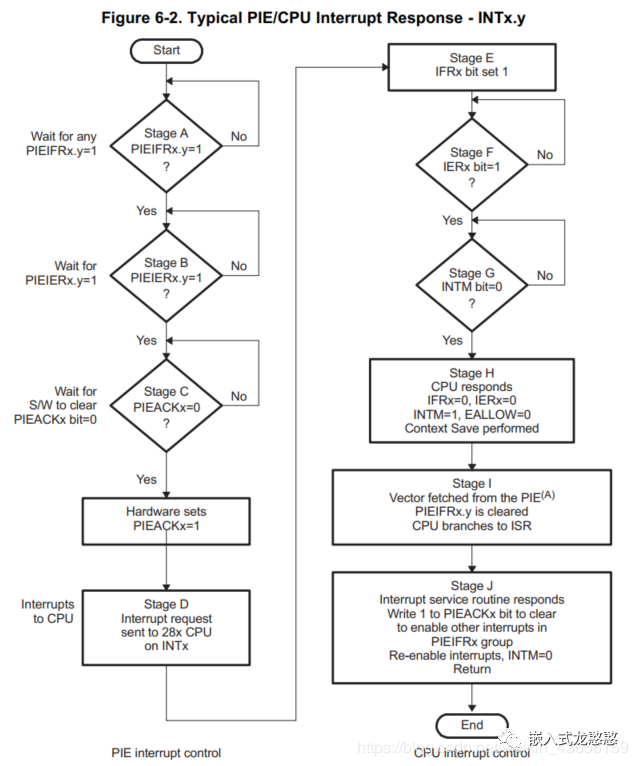

如下图,可以依据Figure6-1和Figure6-2进行理解。

外设级: 当有外设级中断产生,外设中断标志寄存器IF硬件自动置位,同时外设中断使能寄存器IE软件使能(置1)后,向PIE控制器发出中断申请;

PIE级: 有PIE中断时,PIE级中断标志位PIEIFRx硬件自动置位,使能位PIEIERx.y软件使能(置1),PIEACK为0,此时PIE可从终端组向CPU发送中断,PIEACK硬件置1,中断组的中断向量已向CPU发送了中断请求,中断到CPU。

CPU级: 有中断请求时,CPU级中断标志寄存器IFR硬件置1,CPU级中断使能寄存器IER软件使能(置1),全局中断屏蔽位INTM使能(0-使能,CPU可响应;1-失能,CPU不响应),此时CPU响应中断,清除IER,IFR=0(软件清除/自动清零),CPU从PIE获取向量(ISR地址),清除PIEIFRx(中断响应后自动清零、写0也可清零),CPU调到ISR执行中断程序,ISR程序,通过向相应中断位写1到PIEACKx让该位清零,清除PIEIFRx中使能的中断,重新使能中断,INTM=0。

2 定时器

定时器主要总结TIMER0的使用,包括定时器工作原理以及定时时间的设置。

2.1 定时器工作原理

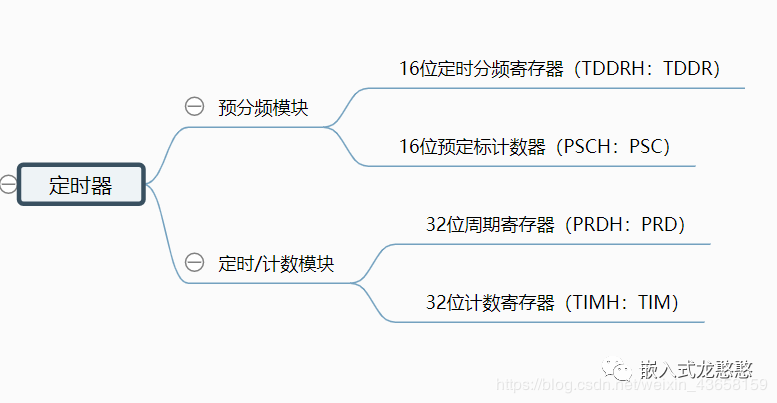

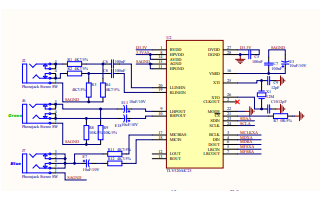

定时器组成如下图所示:

定时器工作原理如下图Figure3-19定时器功能框图以及流程图所示:

由定时器流程图可知,定时器周期寄存器(PRDH:PRD)的值为软件设置的定时器频率* 定时器周期(Freq*Period)的值,定时器周期值在每一个定时器周期开始之前会装载到计数寄存器(TIMH:TIM)中。而计数寄存器的值递减又和预分频模块有关,即和定时器分频寄存器(TDDRH:TDDR)和预定标计数器(PSCH:PSC)有关。

定时器分频寄存器(TDDRH:TDDR)和预定标计数器(PSCH:PSC)主要决定定时器源时钟周期,PSCH:PSC和TDDRH:TDDR等于0时,系统时钟即为定时器源时钟,见外设时钟框图和Figure3-19,可知即每一个定时器源时钟周期(1/150M),TIMH:TIM减1。

每隔(TDDRH:TDDR+1)个定时器源时钟周期,定时器计数寄存器减1。若PSCH:PSC和TDDRH:TDDR等于0时,一个定时器源时钟周期后,重新将TDDRH:TDDR的值装载到PSCH:PSC,TIMH:TIM减1。

2.2 定时时间计算

中断时间T:0.5s,即500ms

T = Freq * Period / 150 000000 (s)

其中Freq 为定时器频率150(MHz);Period 为定时器周期值,计算得来

Period = 150 000000 * 0.5 / 150 = 50 0000

小结

本次总结主要讲述了中断的三级中断制,包括其中断过程中相关定时器的设置;定时器讲述了定时器工作原理和中断时间的设置。这是在学习过程中需要主要了解的内容,掌握这些内容后基本可以完成定时器0的中断实验。

-

寄存器

+关注

关注

31文章

5336浏览量

120239 -

预分频器

+关注

关注

0文章

18浏览量

8131 -

中断定时器

+关注

关注

0文章

4浏览量

5591 -

时钟控制

+关注

关注

0文章

17浏览量

6820

发布评论请先 登录

相关推荐

关于tms320f28335功率保护中断引脚的问题

tms320f28335原理图库

TMS320F28335,TMS320F28334,TMS320F28332 Digital Signal Controllers (DSCs)

tms320f28335的数据手册

TMS320f28335控制AD7656的硬件电路设计

TMS320F28069和TMS320F28335的DSP处理器到底有什么区别

TMS320F28335学习之中断和定时器的相关内容

TMS320F28335学习之中断和定时器的相关内容

评论