为什么pcb走线需要等长?

可以参考这篇文章 PCB设计十大误区-绕不完的等长_等长仿真计算-CSDN博客,简单的理解就是时序是指电路系统的时间特性,即电路的状态随时间的变化情况。数字电路中的信号延迟、时钟频率。

数字电路中,每个操作都需要在正确的时间执行,因为电子元件并不是瞬间完成其功能的。例如,在时钟信号的上升沿或下降沿处将数据写入存储器,然后等待一段时间后读取数据。如果在错误的时序下执行这些操作,从机数据接收错误,导致乱码,(奇偶校验位就是防止数据乱码)

时序分析,在高速数字电路中,通过对电路的设计和interwetten与威廉的赔率体系 来确保电路操作的正确时间关系。它可以通过使用时序约束来指定电路组件之间的相对时序关系。时序分析可以帮助设计人员避免电路中的冒险现象、稳态和暂态时序故障等问题。

时序匹配:在高速数字电路中,信号的到达时间对于确保数据的正确传输非常重要。如果信号经过的路径长度不同,就会导致信号间的时延差异,可能导致时序错误。通过保持信号路径等长,可以最大程度上减小时延差异,使信号到达终点的时间保持一致。

信号完整性:信号在传输过程中可能会受到噪声、互相干扰和反射等影响。等长走线可以帮助降低这些问题的发生概率。当信号经过不等长的走线时,由于信号的传播速度是有限的,不等长的走线可能导致信号波形的失真和不完整。通过保持信号路径等长,可以减小这些问题的风险,提升信号的完整性。

信号匹配:在差分信号传输中,等长走线也可以实现差分信号的匹配。差分信号是指同时传输正负两个相位相反的信号,通过比较这两个信号的差异来恢复原始信号。等长走线可以确保正负两个信号的传播时间一致,从而保持差分信号的匹配性能。

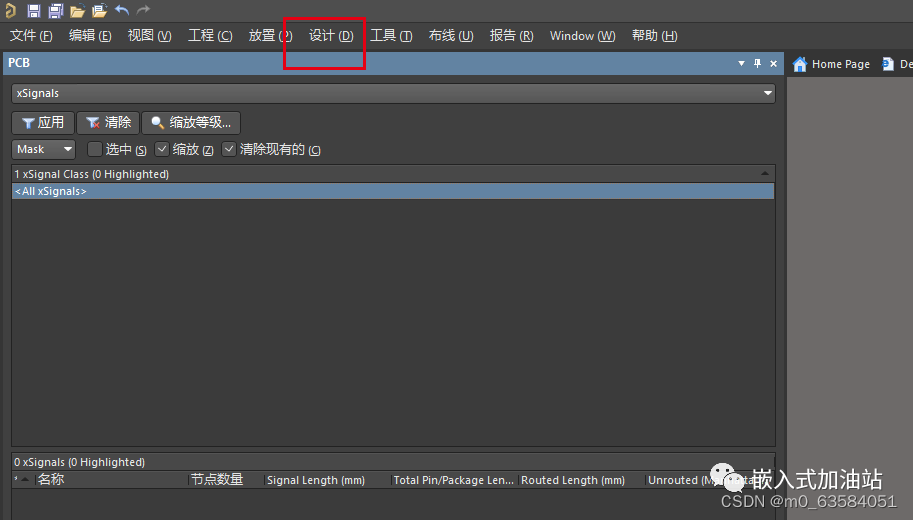

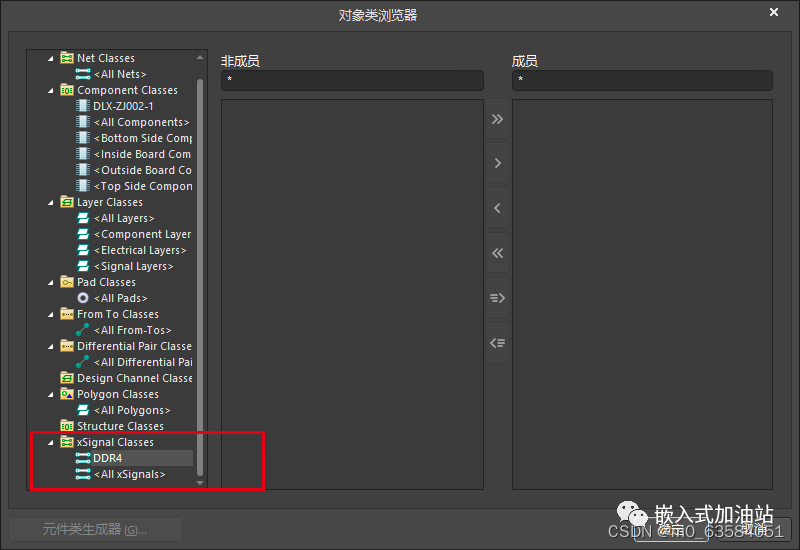

1.添加xSignal,class

编辑

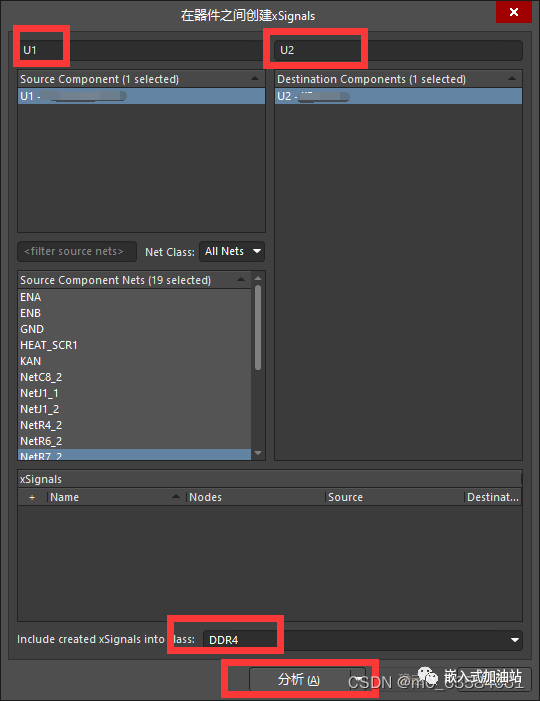

编辑2.再点击设置-创建xsignal,选择两个器件需要等长的网络

编辑

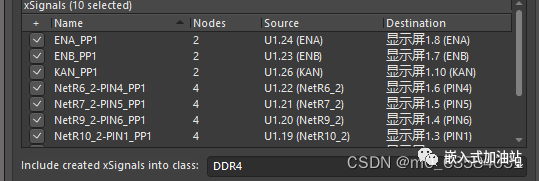

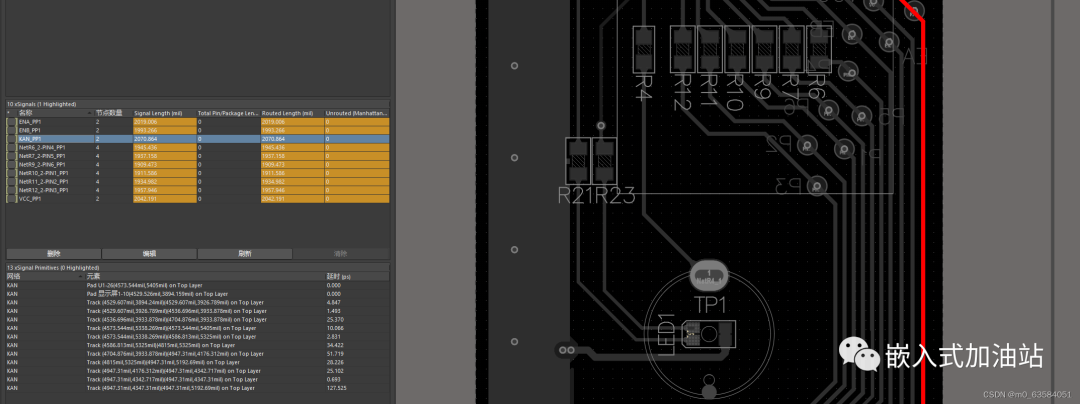

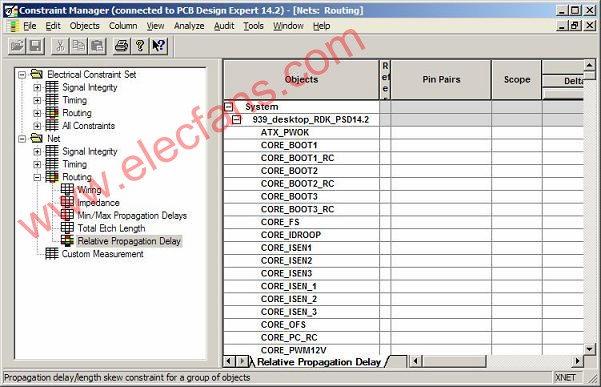

点击分析可以选择要等长的网络

编辑

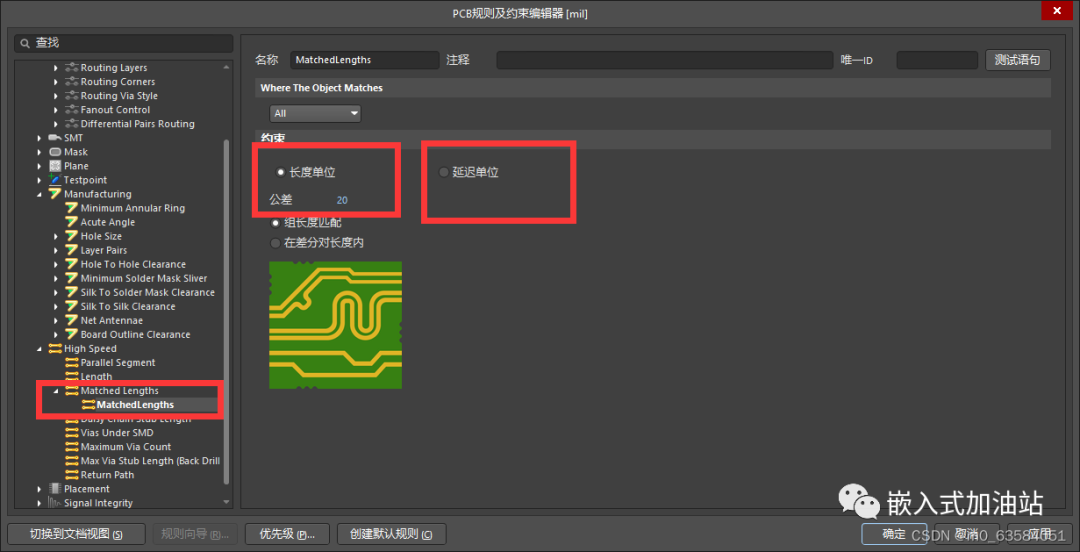

规则中设置长度公差

编辑

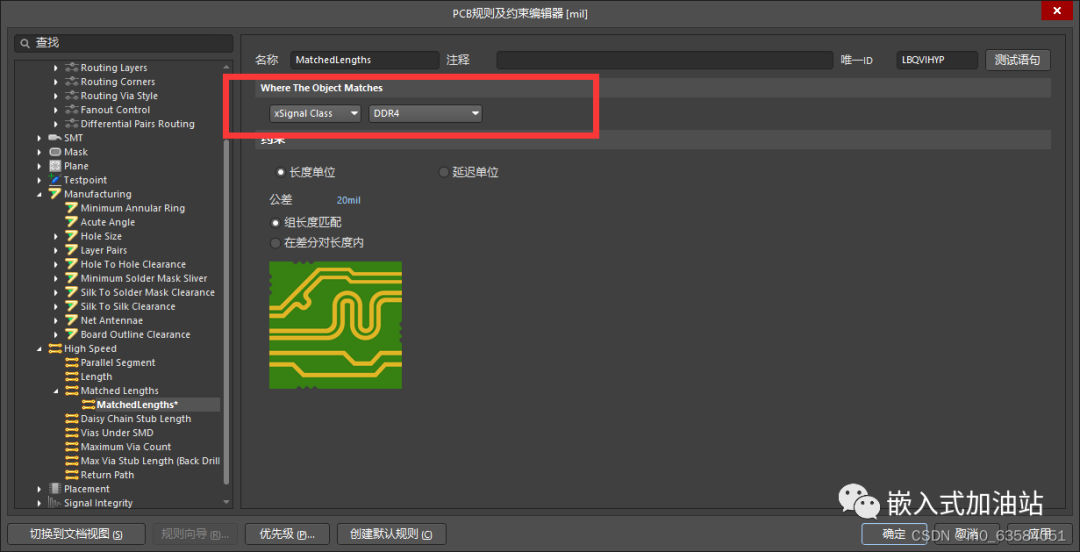

选择创建的类

编辑

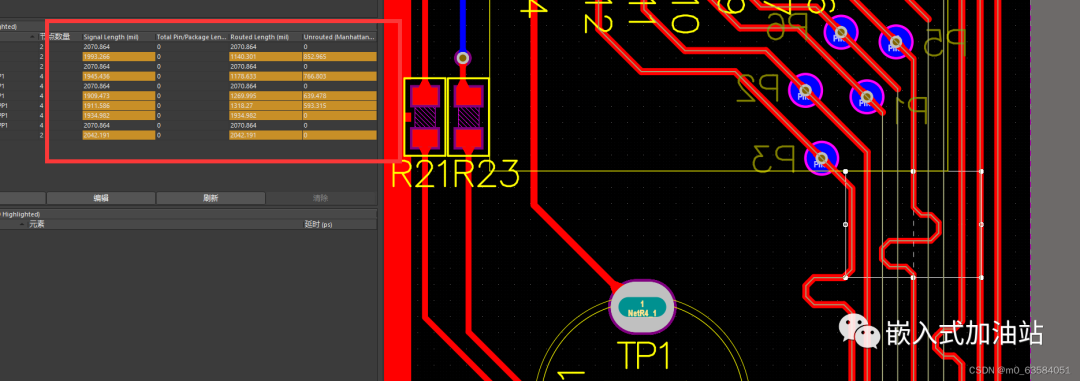

此时黄色表示警告,以黑色线为标准

编辑

编辑

黑色表示公差<=20mil

-

pcb

+关注

关注

4318文章

23053浏览量

396807 -

altium

+关注

关注

47文章

944浏览量

118084 -

数字电路

+关注

关注

193文章

1604浏览量

80554 -

Designer

+关注

关注

0文章

121浏览量

35765

原文标题:Altium Designer 21 xSignal等长设置

文章出处:【微信号:嵌入式加油站,微信公众号:嵌入式加油站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

请教,SIM卡PCB走线,这个CKL时钟线和数据线DATA要等长嘛,一条走顶层一条走底层如图这样可以嘛

请问地址线需不需要等长走线?

AD9446 LVDS信号线的PCB走线的差分对间等长有没有要求?

教您在Allegro中设置走线等长进阶

PCB设计做等长走线的目的是什么

PCB设计中如何实现等长走线

DDR 高速PCB 设计走线绕等长资料下载

为什么pcb走线需要等长?

为什么pcb走线需要等长?

评论