FIFO为什么不能正常工作?复位信号有效长度不够,接口时序不匹配,可看下面这篇文章。

本文将介绍:

非DFX工程如何确保异步FIFO自带的set_max_delay生效?

DFX工程如何确保异步FIFO自带的set_max_delay生效?

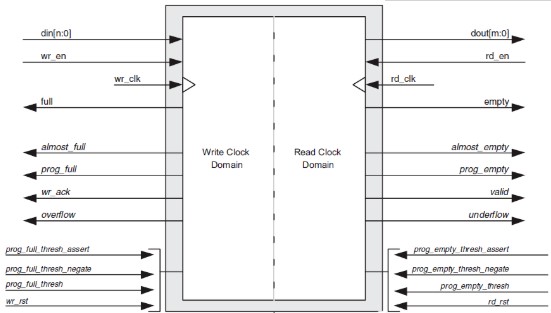

对于异步FIFO,复位信号的使用要特别注意,如下图所示。复位信号必须和wr_clk同步,如果异步,要在wr_clk时钟下同步释放,否则会出现数据无法写入FIFO的情形。

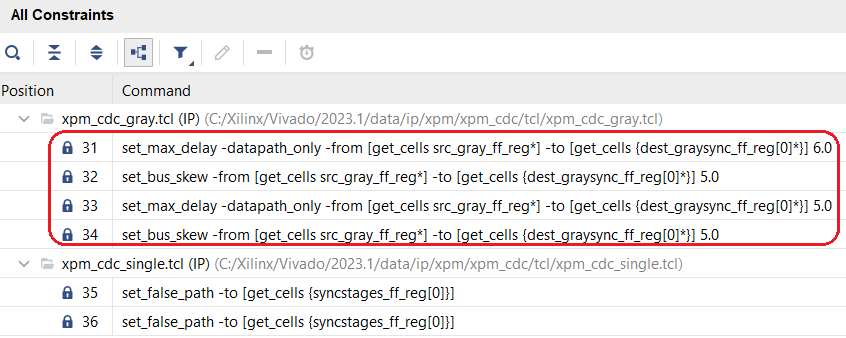

在FPGA设计中,我们会经常用到异步FIFO进行跨时钟域隔离。作为已经非常成熟的设计,AMD提供了两种使用方式:一种是使用IP,一种是使用XPM_FIFO。无论是使用哪种方式,都会生成自带的约束,如下图所示。可以看到使用了set_max_delay和set_bus_skew,这是因为异步FIFO的控制逻辑涉及到二进制码和隔离码的转换,本质上是读/写指针的跨时钟域传递,这两个约束正是针对这部分逻辑电路。

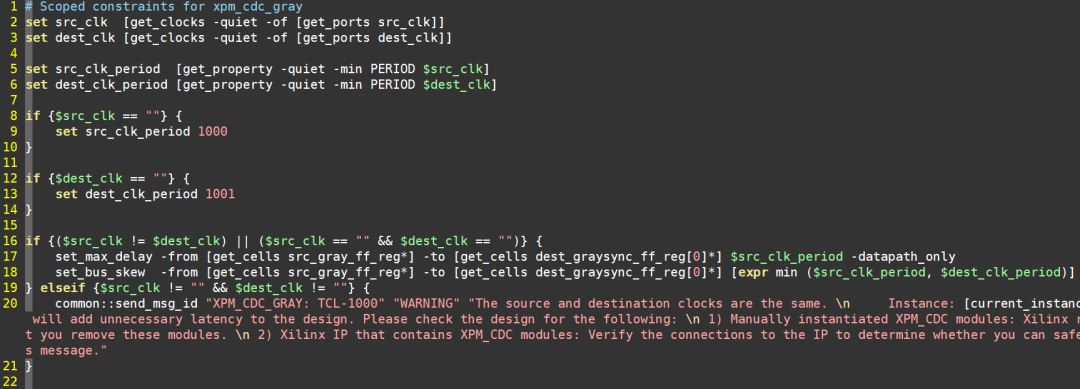

从上图中还可以看到,图中红色方框标记的约束来自于xpm_cdc_gray.tcl文件。该文件可在Vivado安装目录下找到,这里我们给出该文件的部分内容,如下图所示。从图中代码第2行和第3行可以看到,该约束文件在执行前需要获取两个时钟src_clk和dest_clk,第5行和第6行则会分别获取这两个时钟的时钟周期。从这里我们可以判断该文件是在用户约束文件之后编译的。

我们可以打开综合后的设计,通过命令report_compile_order -constraints查看约束文件的编译顺序,会生成如下图所示的报告,在其中的Processing_Order列可以看到用户约束文件的值为NORMAL,而FIFO自带约束文件的值为LATE,这就表明FIFO自带约束文件是在用户约束文件之后进行编译的。原因就是FIFO自带的约束文件依赖于用户约束文件提供的时钟周期。

-

FPGA

+关注

关注

1629文章

21729浏览量

603054 -

FPGA设计

+关注

关注

9文章

428浏览量

26513 -

fifo

+关注

关注

3文章

387浏览量

43655 -

时序

+关注

关注

5文章

387浏览量

37320 -

异步FIFO

+关注

关注

0文章

20浏览量

8354

原文标题:你的FIFO为什么不能正常工作?

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA威廉希尔官方网站 驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

VIPM不能正常工作

不能从FIFO引脚获得输出数据

BurnRead函数不能正常工作

Slave fifo无法正常工作

ASCII不能正常工作

如何处理电脑不能正常关机故障

为什么有时候FIF不能正常工作?

IAR 的 Go to Definition of不能正常使用

同步FIFO和异步FIFO区别介绍

FIFO为什么不能正常工作?

FIFO为什么不能正常工作?

评论