**1 **威廉希尔官方网站 背景

讲负压之前先介绍两个威廉希尔官方网站 背景,以便更好地理解芯片中为什么需要负压。

**1.1 **高速缓存

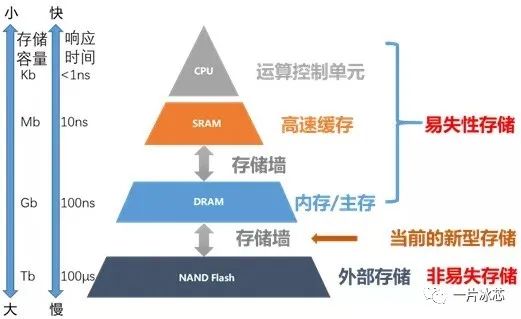

SRAM是目前最成熟的易失性高速存储器,通常由6管(6T)实现数据的读写,可以用做CPU和内存(DRAM)之间的高速缓存。NAND Flash是一种非易失性存储,你电脑、手机中的照片或文件就存储在Flash中。

DRAM速度介于SRAM和Flash之间,也是一种易失性存储器。常见存储架构呈金字塔型,如图1所示。近年以美国公司Everspin和Crossbar为代表的MRAM和RRAM逐渐走向产品化。

MRAM和RRAM特点是速度快、非易失、与CMOS工艺兼容。现代存储架构之所以采用图1所示,是因为设备中有的地方要高速,有的地方要大容量、非易失,说白了就是需求不同。MRAM和RRAM具有SRAM的高速和Flash的非易失,但Everspin和Crossbar产品目录中最大容量只有1GB,未来如果能把容量做大、成本做低,大有改变现代存储架构之势。

为了进一步提高6T SRAM的写入速度,在写入数据时在bit line引入负压,以加快1到0的放电速度。

Fig1. 常见存储架构

1.2****阈值电压调整

调整FDSOI工艺中RBB器件背栅电位可实现阈值电压可调,进而实现低功耗。其中PMOS和NMOS背栅电位从0→+2V和0→-2V变化时阈值电压逐渐增大,这就是负压在IC中的另一个应用。

2 高速SRAM****读写电路

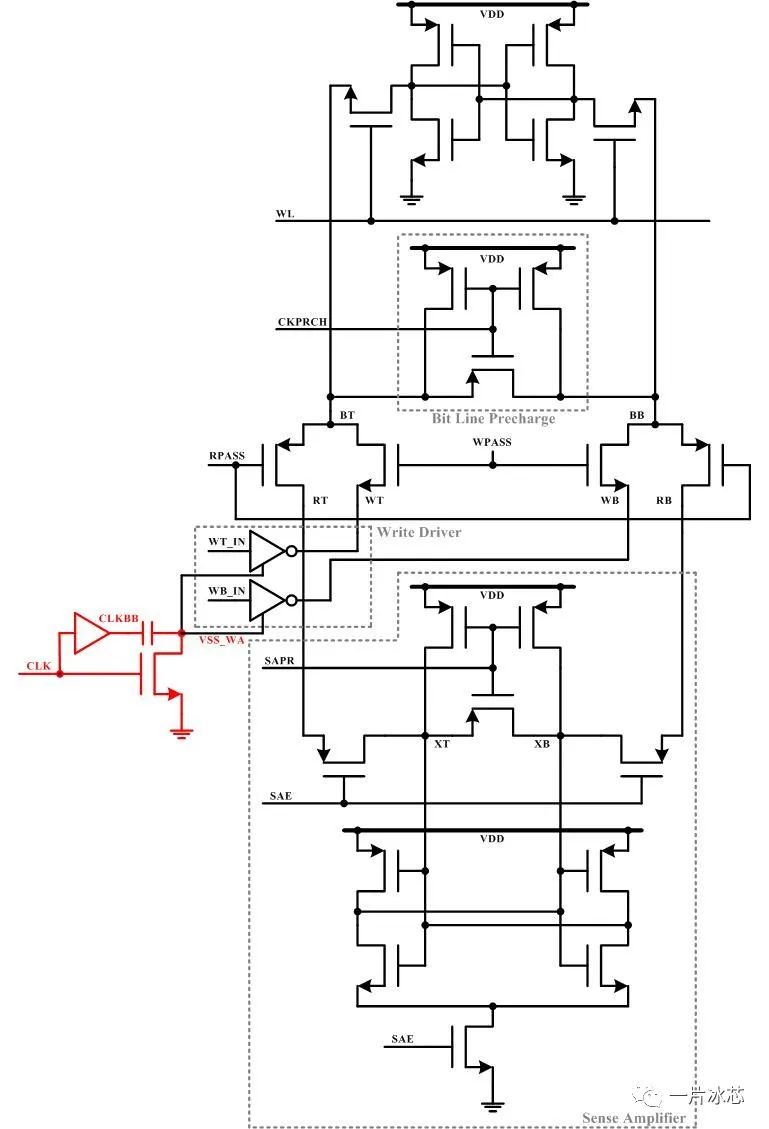

图2给出了1 bit高速SRAM的读写电路 ,其中最上面的6个管子为前边提到的6T存储单元,最下边的灵敏放大器(Sense Amplifier)用于数据的读取,中间包含写驱动(Write Driver)电路、预充电路以及WPASS和RPASS通路。为提高速度,数据写入和读出6T memory cell之前都要进行预充,即把BT、BB、XT和XB预充到高电平。

数据写入时WPASS和RPASS都置高,通过WT_IN和WB_IN对6T memory cell写入数据。数据读出时WPASS和RPASS都置低,通过灵敏放大器读出6T memory cell中存储的数据。写入和读出时WL都要打开,预充时WL都要关闭。

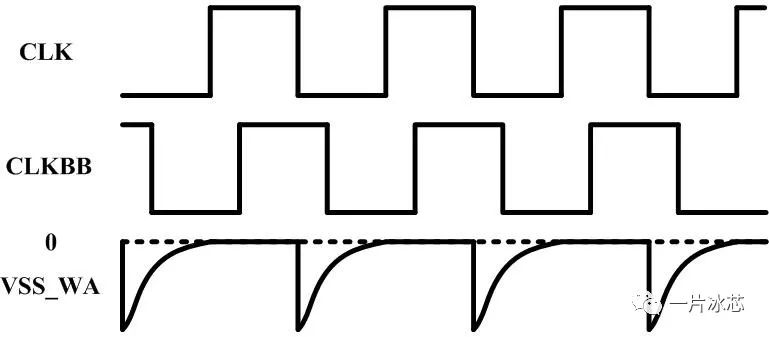

图2左侧红色部分为负脉冲产生电路,利用电容两端电压不能突变这一特性产生的负脉冲VSS_WA作为Write Driver的GND,在WL开启瞬间给6T memory cell提供一条快速放电通路,以提高写入速度,时序图如图3所示。

Fig2. 高速SRAM读写电路

Fig3. 负脉冲产生时序图

**3 **背栅电位调整电路

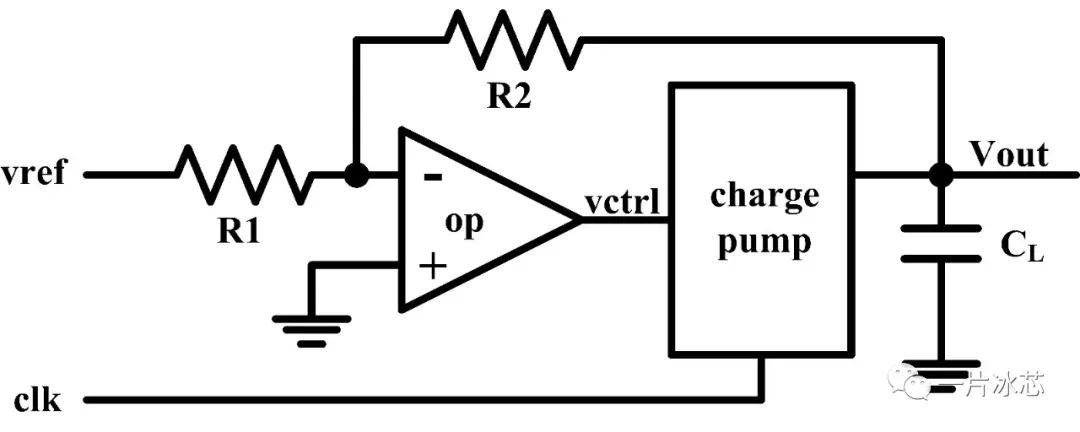

图4给出了带负反馈的电荷泵电路,用于产生精确的负电压。调整vref大小即可改变Vout值。

Fig4. 背栅电位调整电路

根据负反馈原理,运放负端为虚地点,有如下表达式成立:

(vref-0)/R1=(0-Vout)/R2

Vout=-(R2/R1)*vref

假设vref为0.8V,R2/R1为2.5,Vout为-2V。Vout可用于调整FDSOI工艺RBB器件N管的背栅电位。图4中的电荷泵需要多级级联,以解决器件耐压问题。

**4 **思考与讨论

① 图2 SRAM读写操作之前把BT、BB、XT、XB预充到VDD为什么可以提高读写速度?

② 图2 灵敏放大器中的SAE与WL同时开启可以吗?

③ 如何提高读取速度?

④ WPASS通路为什么用N管?RPASS通路为什么用P管?

⑤ 读的时候为什么需要用灵敏放大器?

⑥ 图4电荷泵如何实现?

⑦ 参考图4你能否设计一个电路得到+2V电压?

⑧ 图4能否改成自适应结构?自适应调整器件背栅电位,以监测PVT变化,进而平衡速度和功耗。

-

放大器

+关注

关注

143文章

13586浏览量

213375 -

NAND

+关注

关注

16文章

1681浏览量

136125 -

CMOS工艺

+关注

关注

1文章

58浏览量

15672 -

电容电压

+关注

关注

0文章

74浏览量

11207 -

SRAM存储器

+关注

关注

0文章

88浏览量

13290

发布评论请先 登录

相关推荐

高频变压器中传导EMI产生机理

电子产品中的电磁发射和磁场干扰的产生机理分析

电源扰动及地弹噪声的产生机理

转子磁场的产生机理及在空间的分布

分析开关电源电磁干扰的各种产生机理

电磁干扰的产生机理资料下载

枕头缺陷的产生机理和原因分析

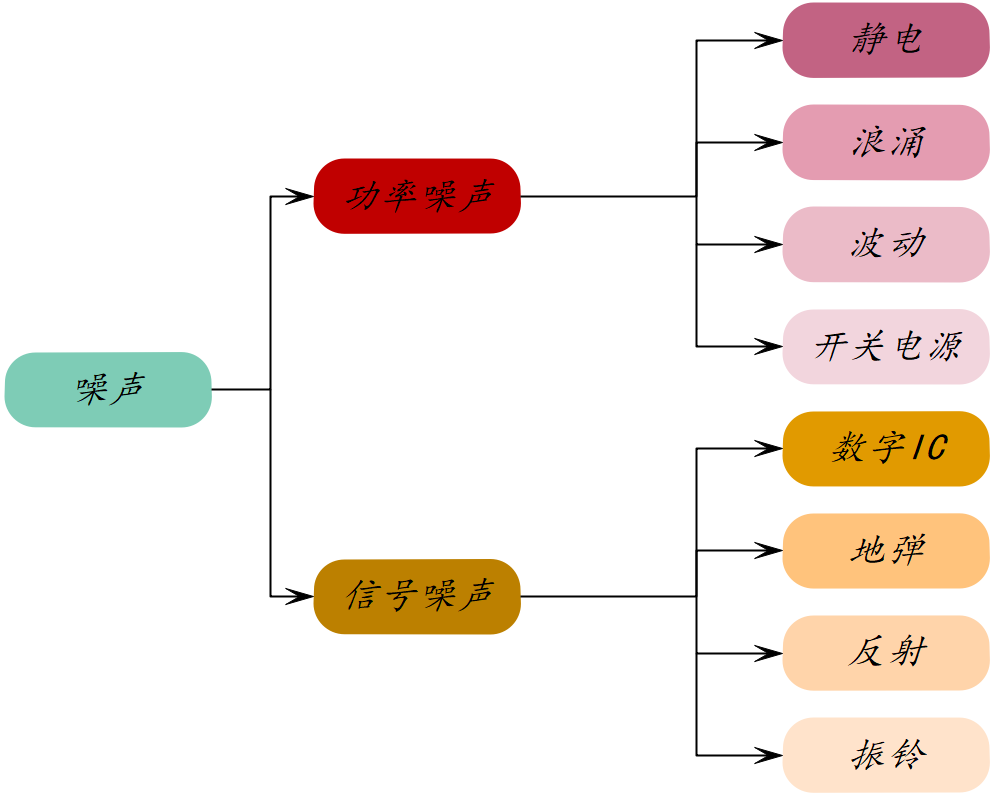

简述噪声的产生机理和来源

聊聊芯片中的负压产生机理及其应用

聊聊芯片中的负压产生机理及其应用

评论