**1 **ESD Scheme

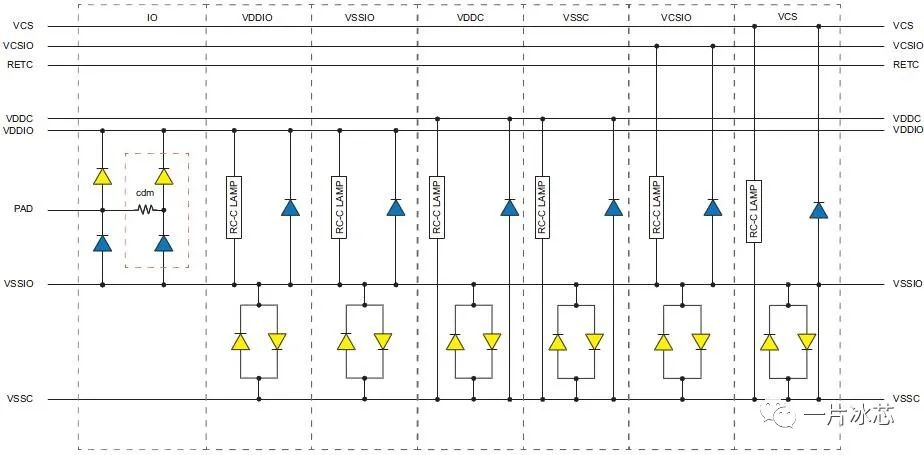

一般多电源轨的ESD方案如图1所示。最左侧两个diode用于HBM(Human Body Model)保护,与其相邻的电阻(250Ω)及diode用于CDM(Charge Device Model)保护,PAD和VDDIO之间的P-diode用于正向ESD放电,PAD和VSSIO之间的N-diode用于负向ESD放电,当正向ESD发生时电源地之间的RC-CLAMP触发,当负向ESD发生时电源地之间的N-diode触发,VSSIO和VSSC之间的背靠背diode提供双向ESD放电通路。

Fig1. ESD Scheme

再跟大家啰嗦两句,你有没有好奇过图2所示,我们手中的micro-SD card,为什么会有两个脚突出来呢?其实这两个脚就是芯片的电源和地,当芯片插入卡槽过程中突出的引脚会率先与卡槽接触,实现预放电,达到ESD保护的目的,哈哈,是不是很有意思。

无规矩不成方圆,ESD当然也有专门的标准,如HBM的ANSI/ESDA/JEDECJS-001-2017标准,CDM的ANSI/ESDA/JEDECJS-002-2014标准以及MM(Machine Model)的ANSI/ESDSTM5.2-2012标准等。工业、军品、汽车(HBM一般要达到8000V)、宇航ESD标准不一,你的芯片对应哪个市场就follow哪个啦。

图1所示的RC-CLAMP要满足以下条件:

① DC状态各PVT下有较小的leakage;

② HBM、CDM、MM下各晶体管不得出现耐压问题;

③ 各电源上下电时保证RC-CLAMP的功率管关断。

我似乎跑题了,ESD内容太多了,以后有机会再跟大家聊吧,下面书归正传。

**2 **Latch up

2.1 bulk工艺中的latch up

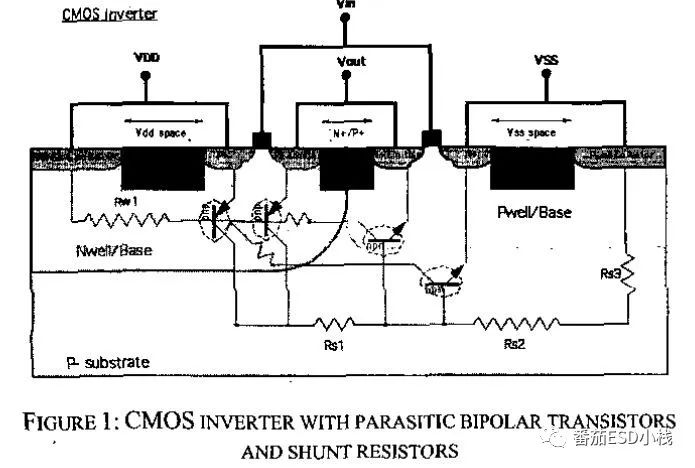

bulk工艺中的latch up原理及触发机理就不啰嗦了,请自行找度娘学习,我这边只贴一张图。

Fig3. inverter的剖面图及寄生模型

可见bulk工艺中的latch up跟寄生电阻密切相关,layout时要特别注意有源区到阱边界距离,不同电位阱之间的距离(通常要求1.5倍以上最小线宽),过孔和通孔数量等问题。

2.2 SOI工艺中的latch up

SOI(Silicon-on-Insulator),在摩尔定律的延续一讲中给大家介绍过,没接触这个工艺的先自己学习一下。SOI中的耗尽层夹在两层氧化层之间,类似于三明治,图4给出了SOI和bulk工艺的剖面图,图中左面的埋藏氧化层厚度只有20nm左右而且平整度要求非常高,能提供这种晶圆的寥寥无几,价格也相对较高。

Fig4. SOI和bulk工艺CMOS晶体管的剖面图

SOI工艺通过超薄埋氧实现了器件隔离,因此寄生BJT也不存在,从而实现latch up immune。那么本章为什么还要提SOI工艺中的latch up呢?在SOI工艺中并不是所有器件都做在超薄埋氧中,如diode、varactor电容、ldmos等,因此也会有latchup薄弱点。

下面以Invecas公司在22nm FDSOI中遇到的问题 ^[1]^ 为例进行latch up分析。

据我了解,Globalfoundries 22nm FDSOI工艺一次full mask的价格现在的价格约1000万RMB,因此这个latch up问题可能让Invecas公司损失1000万RMB甚至更多。

论文中的3.3V RC-CLAMP,正如图1中VDDIO和VSSIO之间的RC-CLAMP,Invecas设计的第一版3.3V RC-CLAMP电路如图5所示。其中VDD3V3为3.3V电源,EGNCAP为体硅器件,内部所有器件(电阻除外)任意两端电压(背栅除外)不得超过1.8V,因此这是一种用1.8V device设计的耐压结构RC-CLAMP。

Fig5. 第一版3.3V RC-CLAMP

latch up测试出现问题是在图1中的PAD抽负电流时引起GPIO相邻位置的RC-CLAMP的N2和N3管(图5)导通,芯片热点分析如图6所示。

Fig6. 芯片热点分析

该latch up不同于传统体硅中npnp(图3),它是由GPIO PAD(图1和图6)上的负电流latch up测试引起的寄生npn导通(为了与传统npnp latch up区分,这里叫pseudo latch up),如图7所示。主要原因是图5中的大电容采用了EGNCAP,EGNCAP是做在Hybrid region,是一种varactor电容,有源区做在了N阱中,剖面图如图8所示。

正常工作时P_BIAS处于中间电位(VDD3V3/2),当负latch up电流注入IO PAD时P_BIAS中的N阱会收集电子,导致P_BIAS电位降低,进而开启N2和N3管,导致电源和地之间出现大电流,即使移除负向latchup测试电流,N2和N3管仍会保持开启。

Fig7. Trigger path from IO PAD to neighboring nwell of EGNCAP from supply cell

Fig8. EGNCAP剖面图

针对以上问题,对Invecas对RC-CLAMP电路进行了修改,修改后的电路如图9所示。最明显的一个特征就是用EGNFET替换了EGNCAP电容,EGNFET是SOI器件,彻底消除了前边提到的中间电位N阱(P_BIAS)收集电子的问题。还有其他小的修改,限于篇幅请自行阅读论文。

Fig9. 第二版3.3V RC-CLAMP

3 Consideration anddiscussion

RC-CLAMP中的RC常数及管子尺寸该如何选取?这里提到的EGNCAP是一种varactor电容,不同于传统MOS电容,其C-V曲线呈单调变化,什么地方会用到它呢?

-

ESD保护

+关注

关注

0文章

433浏览量

27025 -

CDM

+关注

关注

0文章

30浏览量

12237 -

CMOS晶体管

+关注

关注

0文章

11浏览量

10208 -

GPIO

+关注

关注

16文章

1204浏览量

52082 -

寄生电阻

+关注

关注

1文章

20浏览量

2280

发布评论请先 登录

相关推荐

聊一聊FDSOI工艺中的latch up(pseudo)

聊一聊FDSOI工艺中的latch up(pseudo)

评论