**1 **应用背景

板卡上的芯片需要相互通信,IO接口电平越丰富,芯片通用性越强。以28 nm工艺为例,IO device最高可耐1.98V,core device最高可耐1.0V,而IO电平需要同时满足1.2V, 1.5V, 1.8V, 2.5V, 3.3V,这就需要设计一款宽输入电压范围耐压结构的IO模块。

**2 **Widerange voltage translation

该专利介绍的是一种宽输入范围(1.2V~3.3V)的level-shift,为满足如此宽的电压输入,将电路分成了两种工作模式,一种是高压模式(>1.8V),一种是低压工作模式(≤1.8V),两种模式的切换是由BIAS GENERATION SEGMENT控制,下面我们分别介绍这两种工作模式。

2.1 高压模式(2.5V, 3.3V)

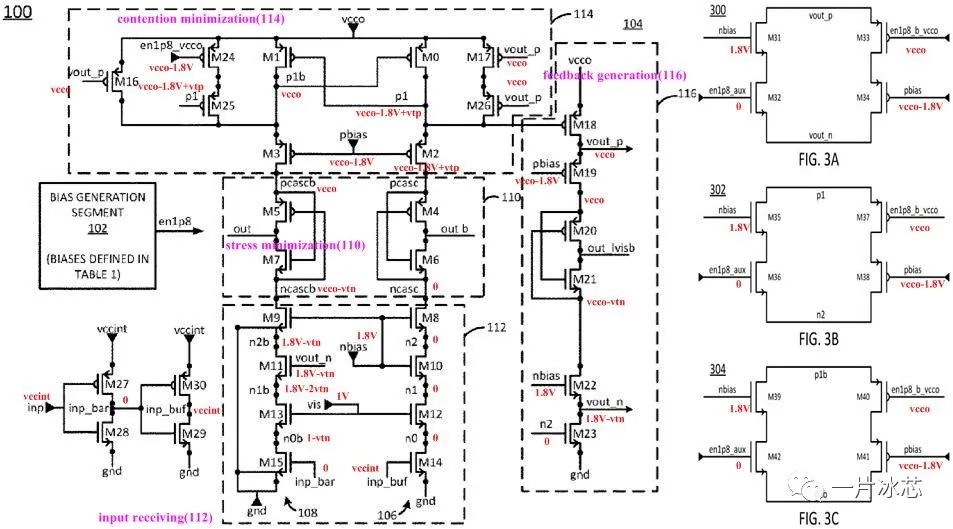

图1给出了宽输入level-shift高压模式(2.5V, 3.3V)电路,图中M14M15和M27M30为core device,最高工作电压为0.925V,其他器件均为高压管(IO device),最高工作电压为1.89V,vtn和vtp分别为IO device n管和p管的阈值电压,vcco为IO电源(1.2V3.3V), vccint(0.65V0.925V)为芯片内部数字逻辑电源,BIAS GENERATION SEGMENT中还有一个辅助(auxiliary)电源vccaux(本讲不涉及此电源)。

整体电路(100)分为input receiving(112), stress minimization(110), contention minimization(114), feedback generation(116)以及BIAS GENERATION SEGMENT(102)。

其中BIAS GENERATION SEGMENT没有给出具体电路,只给出了不同模式下的输出电压,如表1所示。高压模式下pbias = vcco-1.8V, nbias = 1.8V, en1p8_vcco = vcco-1.8V, en1p8_aux = 0V,en1p8_b_vcco = vcco, vis = 1V,这些电位是用于保护IO device和core device。

图1(a)标注了初始时刻inp为高电平(vccint,≤0.925V,如图2 T1时刻)时关键节点的电平(红色字体),可见初始时刻所有device不存在耐压问题。其中inp为low voltage domain(vccint)level-shift输入,vout_p为high voltage domain(vcco)level-shift输出,初始时刻inp为vccint,vout_p为vcco,完成了不同电压domain高(inp)到高(vout_p)的转换。

该结构引入了input receiving(112), stress minimization(110), contention minimization(114)和feedback generation(116)等威廉希尔官方网站 用于解决耐压、速度、竞争等问题,专利中已经描述的非常详细,有兴趣的可以仔细阅读。其中M0和M1的尺寸比为5:1(即M1较weak)且M17和M26也较M0 weak,这样可以解决电平转换时的高低电平竞争问题,使0→1或1→0的转换更准更快。

(a)inp为高电平(vccint)工作原理

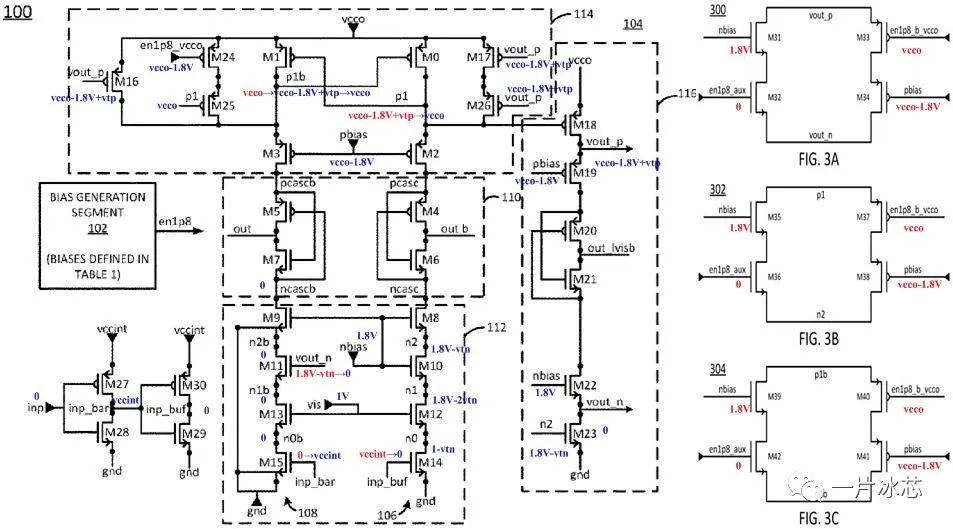

图1(b)标注了初始时刻inp由高到低跳变(vccint, ≤0.925V,如图2 T2~T3时刻)时关键节点的电平(红 & 蓝字体),inp由高到低跳变时所有device也不存在耐压问题。low voltage domain的低电平为0V,high voltage domain的低电平为vcco-1.8V+vtp,完成了不同电压domain高到低(inp)to高到低(vout_p)的转换。

(b)inp由高(vccint)到低(0)跳变工作原理

Fig1. 宽输入level-shift高压模式(2.5V, 3.3V)电路

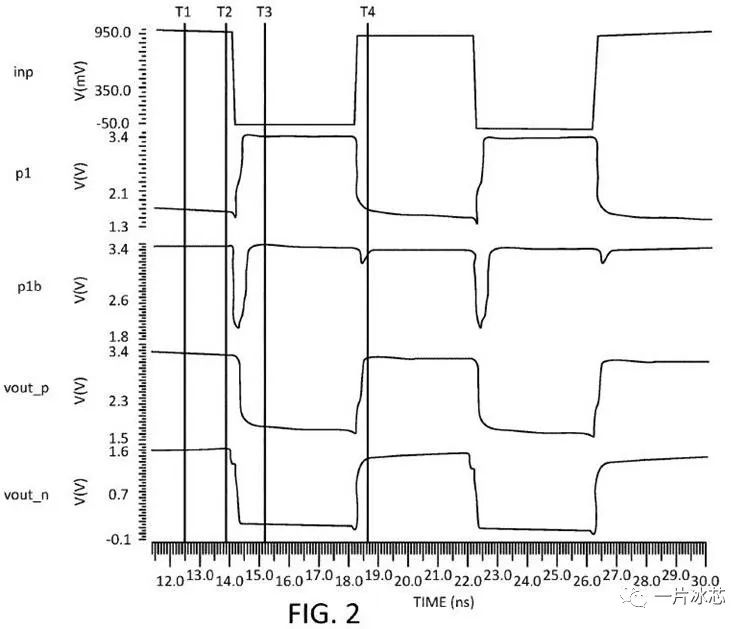

图2给出了高压模式下level-shift inp, p1, p1b, vout_p, vout_n的波形,其中T3T4的分析与T1T2类似,这里不再赘述。

Fig2. 宽输入level-shift高压模式(2.5V, 3.3V)波形

2.2 低压模式(1.2V, 1.5V, 1.8V)

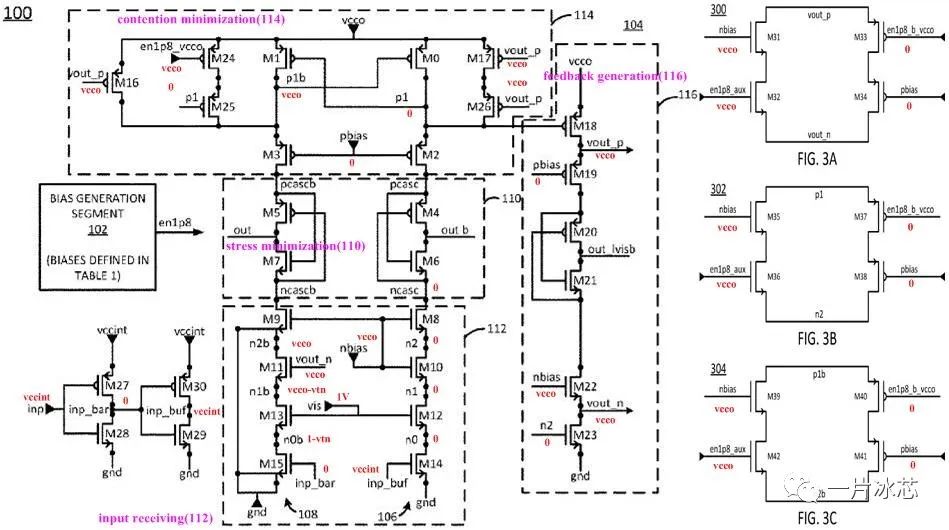

为节约芯片面积,低压模式与高压模式共用一套电路,如图3所示。低压模式下pbias = 0V, nbias = vcco, en1p8_vcco = vcco, en1p8_aux = vcco, en1p8_b_vcco = 0, vis = 1V,如表1所示。低压模式出于电压裕度和速度考虑,不再需要钳位电压和钳位电路。低压模式下可通过图3右侧电路将vout_p和vout_n,p1和n2,p1b和n2b短接以旁路掉中间钳位电路。

其中inp为low voltage domain (vccint,≤0.925V) level-shift输入,vout_p为high voltage domain(vcco,≤1.8V)level-shift输出,初始时刻inp为vccint,vout_p和vout_n为vcco,完成了不同电压domain高(inp)到高(vout_p)的转换。inp由高跳低再跳高的转换过程与之前高压模式类似,这里不再赘述。

Fig3. 宽输入level-shift低压模式(1.2V, 1.5V, 1.8V)电路

3 Voltage-resistantbuffer

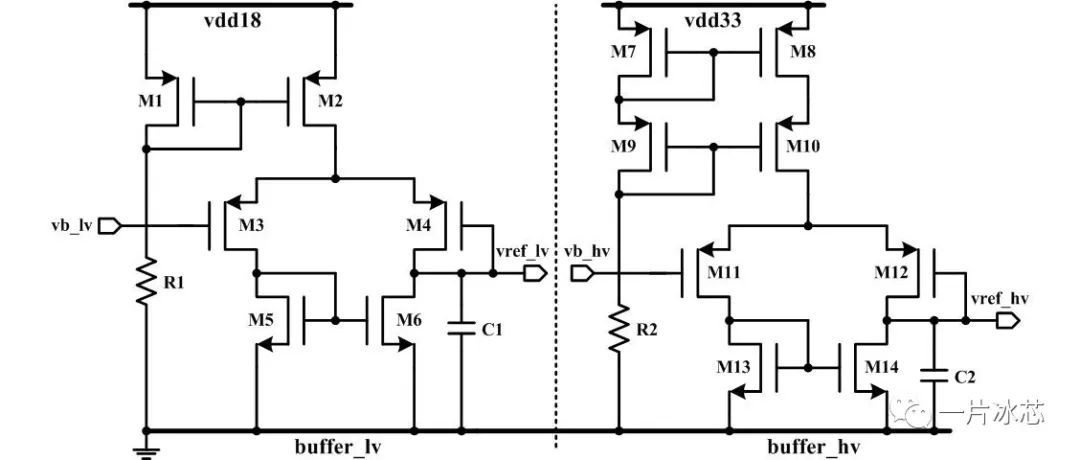

根据第2章分析我们举一反三,介绍如何实现耐压结构的buffer,如图4所示。图4所有device(电阻除外)任意两端电压(bulk除外)在任意工作模式下不得超过1.98V。左侧(buffer_lv)电路电源电压(vdd18)为1.8V,因为没有耐压风险,很容易实现。

当左面电路电源电压(vdd18)提升到3.3V时,所有device均会出现耐压问题,不加以处理会严重影响芯片寿命。我们在左侧电路M1,M2漏端插入一组cascode晶体管(如图4右侧M9, M10所示)即可实现耐压结构的buffer,如图4右侧F。

由此可推广到更加复杂的电路系统,基本思想就是通过叠管子、钳位来保护有耐压风险的晶体管。

Fig4. 低压和高压buffer原理图

**4 **思考与讨论

① 专利中的BIAS GENERATION SEGMENT如何实现?整体IO Block又如何实现?一个IO Block又如何同时兼容LVDS、LVCMOS、LVTTL等电平标准?

② 根据以上分析如何举一反三,设计一款耐压结构的bandgap、mux等电路?

③ power down时如何不存在耐压问题?应该加何种电路以辅助实现power down。

④ 当电路规模庞大时,如何check网表中所有device是否存在耐压问题(正常工作、power down以及上下电过程中都不要有耐压风险)?

-

电平转换器

+关注

关注

1文章

175浏览量

19569 -

晶体管

+关注

关注

77文章

9687浏览量

138129 -

钳位电压

+关注

关注

0文章

38浏览量

12090 -

IO接口

+关注

关注

0文章

31浏览量

13403 -

LVDS电路

+关注

关注

0文章

3浏览量

1224

发布评论请先 登录

相关推荐

宽电压输入稳压电源模块 E48_UHFCS-3W系列

LTC3588耐压范围如何提高?

LT6372-1: Precision Instrumentation Amplifier with Level Shift and Output Clamping Data Sheet

LT6372-0.2: Precision, Funneling Instrumentation Amplifier with Level Shift and Output Clamping Data Sheet

IO模块中的宽输入范围耐压结构level-shift

IO模块中的宽输入范围耐压结构level-shift

评论