在整个传输事务过程中,主机首先将接下来 burst 传输的控制信息以及数据首个字节的地址传输给从机,这个地址被称为起始地址。

在本次 burst 后续传输期间,从机将根据控制信息计算后续数据的地址。

控制信息以及起始地址在读/写地址通道(AWC/ARC)传输。

注意:单次 burst 传输中的数据,其地址不能跨越 4KB 边界。 关于这点在笔者参考的一个来源这样表示,目前笔者觉得看上去很有道理:协议中之所以规定一个burst不能跨越4K边界是为了避免一笔burst交易访问两个slave (每个slave的地址空间是4K/1K对齐的)4K对齐最大原因是系统中定义一个page大小是4K, 而所谓的4K边界是指低12bit为0的地址。

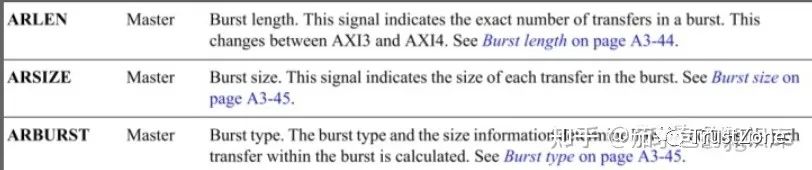

地址通道中传输的控制信息中包括三项突发传输相关的信号(AR/AW 均一致,下图为以 AR 为例):

(1)突发传输长度(burst length)

指一次突发传输中包含的数据传输(transfer)数量,在协议中使用 AxLen 信号控制。

突发传输长度在不同的模式(burst type ,将在后文中讨论)下有一些限制,包括:

•对于 WRAP 模式,突发传输长度仅能为2,4,8,16

•在一次突发传输中,地址不能跨越一个 4KB 分区

•一次突发传输不能在完成所有数据传输前提前结束(early termination)

协议中多次强调,通信双方都不能在传输事务的所有 Transfer 完成前提前结束。哪怕发生错误,也得含泪走完整个传输事务的流程。

(2)突发传输宽度(burst size)

指传输中的数据位宽,具体地,是每周期传输数据的字节(Byte)数量,在协议中使用 AXSIZE 信号控制。

突发传输数据宽度不能超过数据总线本身的位宽。而当数据总线位宽大于突发传输宽度时,将根据协议的相关规定,将数据在部分数据线上传输。

传输宽度 = 2 ^ AXSIZE

(3)突发传输类型(AxBURST)

类型共有 3 种,分别为 FIXED,INCR 以及 WRAP。使用 2 位二进制表示。

FIXED 类型中, burst 中所有数据都使用起始地址。该模式适合对某个固定地址进行多次数据更新,比如读写一个 fifo时,读写地址就是固定的。

INCR 类型最为常用,后续数据的地址在初始地址的基础上进行递增,递增幅度与传输宽度相同。适合对于 RAM 等通过地址映射(mapped memory)的存储介质进行读写操作。

WRAP 类型比较特殊,首先根据起始地址得到绕回边界地址(wrap boundary)与最高地址。当前地址小于最高地址时,WRAP 与 INCR类型完全相同,地址递增。但到递增后的地址到达最高地址后,地址直接回到绕回边界地址,再进行递增,就这样循环往复。

-

数据

+关注

关注

8文章

7006浏览量

88958 -

结构

+关注

关注

1文章

117浏览量

21593 -

总线

+关注

关注

10文章

2878浏览量

88056 -

AXI

+关注

关注

1文章

127浏览量

16625

发布评论请先 登录

相关推荐

ARM+FPGA开发:基于AXI总线的GPIO IP创建

使用AXI-Full接口的IP进行DDR的读写测试

玩转Zynq连载37——[ex56] 基于Zynq的AXI HP总线读写实例

如何避免AXI_hp总线锁死?

AXI4协议的读写通道结构

看看在SpinalHDL中AXI4总线互联IP的设计

AXI 总线和引脚的介绍

AXI总线:读写地址结构

AXI总线:读写地址结构

评论