一、读写平衡训练

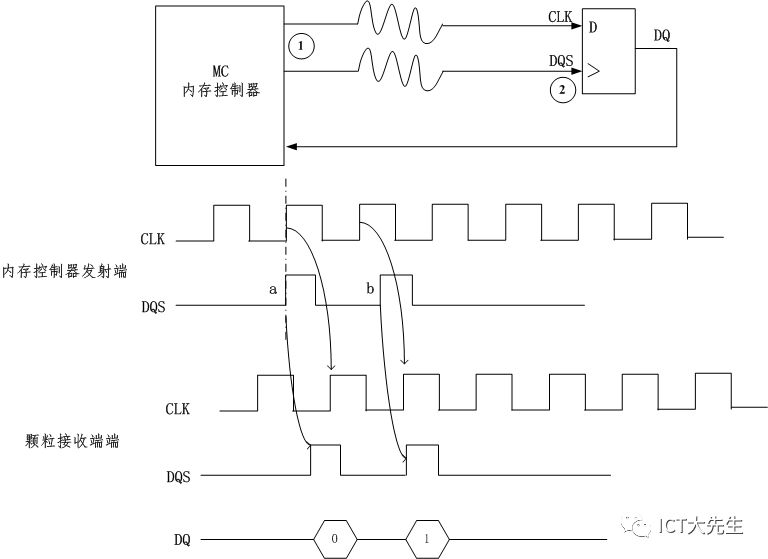

如图所示,内存控制器与颗粒相连接,并通过DQ(数据线)反馈。在发射端(图中1点)的第a次信号发射,CLK与DQS同相位,但是因为电路板上连线的长度差异,飞行时间不同,在颗粒的接收端(图中2点)产生了相位差。在第a次发射,D触发器输出结果是0,内存控制器得到DQ反馈为0。

内存控制器接着在第b次发射,调整CLK与DQS的相位,此次D触发器在时钟高电平触发,得到反馈即为1。

经过多次不同相位关系的训练,内存控制器得到了CLK与DQS的线长关系。

二、GDDR5时钟训练

GDDR5专用于显存,本篇不展开阐述,具体内容可以参考(JEDEC规范JESD212C),它和DDR在电路接口有差异,数据线中没有DQS,采用WCK/WCK#同步数据(即WCK与数据线组内等长),而地址、命令由CK/CK#同步(即地址、命令与CK组内等长)。

在GDDR5规范中,初始化其中一个步骤是WCK2CK alignment training(即WCK to CK的相位对齐)

两时钟的相位关系反馈于控制器,记录于MR(模式寄存器)中。

三、锁相威廉希尔官方网站

锁相威廉希尔官方网站 对数字芯片的时钟设计极其重要。

锁相环主要的三个组成部分(很多材料上讲前向通道、反馈通道上分频、倍频之类,那些不是锁相威廉希尔官方网站 的本质元素)

1、 PD或PFD(鉴相器或鉴频鉴相器)

2、 LF(环路滤波器)

3、 VCO(压控振荡器)

鉴相器的实现方式很多,在此列举一种比较简单的“异或门”,进而阐述锁相原理。

输入时钟和反馈时钟,存在相位差,经过异或门,输出PWM,此波形经过环路滤波器,输出直流电压,输入压控振荡器,压控振荡器输出一定频率时钟。

这里的反馈关系在于:如果输入和反馈时钟相位变化,调整了PWM占空比,进而输入VCO的电压也会变化,采用负反馈调整输出时钟频率。

-

DDR3

+关注

关注

2文章

276浏览量

42245 -

锁相威廉希尔官方网站

+关注

关注

0文章

6浏览量

7008 -

数字芯片

+关注

关注

1文章

110浏览量

18384 -

内存控制器

+关注

关注

0文章

40浏览量

8884 -

GDDR

+关注

关注

0文章

27浏览量

4659

发布评论请先 登录

相关推荐

基于FPGA的DDR3多端口读写存储管理系统设计

【紫光同创国产FPGA教程】【第十章】DDR3读写测试实验

基于FPGA的DDR3多端口读写存储管理设计

DDR3不是GDDR3 细说GDDR3显存认识误区

cyclone V控制DDR3的读写,quartusII配置DDR3 ip核后,如何调用实现DDR3的读写呢,谢谢

基于Xilinx MIS IP的DDR3读写User Interface解析

请问ddr3的输入时钟稳定度需要多少ppm?

基于FPGA的DDR3多端口读写存储管理的设计与实现

基于FPGA的DDR3协议解析逻辑设计

DDR3读写平衡、GDDR时钟训练与锁相威廉希尔官方网站

阐述

DDR3读写平衡、GDDR时钟训练与锁相威廉希尔官方网站

阐述

评论