运算放大器的Data sheet一般分为两大类:直流参数和交流参数。DC参数决定了输出与理想运算放大器匹配的精确程度。因此,运算放大器的精度取决于直流误差的大小。

我们在使用运放时,经常会看到一个参数,输入失调电压,输入失调电压 (VOS) 是运算放大器 (op amp) 规格中的常见直流参数。但是这个值是干嘛的?今天我们主要分为如下两方面进行讲解一下。

①失调电压的理解

②失调电压的产生

01

失调电压的理解

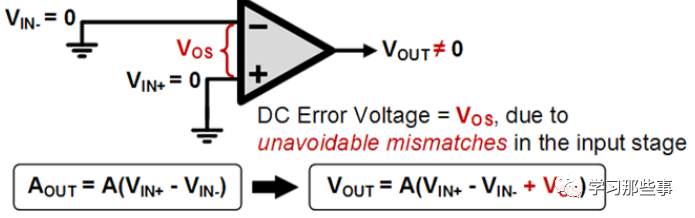

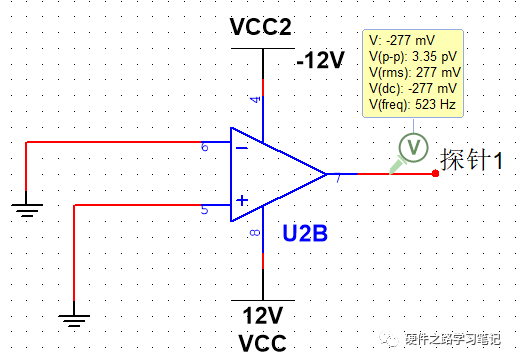

理想情况下,如果运算放大器的两个输入电压完全相同,则输出应为0V。但运放内部两输入支路无法做到完全平衡,导致输出永远不会是0,具体见图1所示。此时保持放大器负输入端不变,而在正输入端施加一个可调的直流电压,调节它直到输出直流电压变为0V,此时正输入端施加的电压的负值即为输入失调电压,用VOS表示。

但是,多数情况下,输入失调电压不分正负, 生产厂家会以绝对值表示。输入失调电压乘以增益,表现为输出电压与理想值的偏差。当运用在传感器时,运算放大器的输入失调电压会导致传感器检测灵敏度出现误差。为了将检测误差保持在指定的容限水平以下,有必要选择具有低输入失调电压的运算放大器。

因此,可以知道对于一些要求高的产品会选择输入失调电压较小的运放,失调电压为1uV以下,属于极优秀的。100uV以下的属于较好的。

例如:当一个放大器被设计成A倍闭环电压增益时,如果放大器的失调电压为VOS,则放大电路0输入时,输出存在一个等于A*VOS的直流电平,此输出被称为输出失调电压。闭环增益越大,则输出失调电压也越大。对我们想要的输出偏差就越大。

图1 对VOS的图解

理论来说Vout=A(VIN+-VIN-),但实际是Vout=A(VIN+-VIN-+VOS),意味着Vout会受VOS干扰。我们来看图2加深印象,可以看见实线是我们想要的输出波形,虚线为实际的输出波形,当V0S越小时,虚线越接近实线。

图 2 输出波形

02

失调电压产生原因

①芯片制造工艺导致

输入失调电压的产生,主要是因为输入级对称晶体管的不匹配所导致,而这种情况在工艺上很难避免,就好比同样加工的产品尺寸总会有一定的误差,不可能完全一样,只是看你衡量的尺度,比如只精确小数点后两位时值可能一样,但是精确到小数点后十位、后百位时,就会出现差异了,这是工艺上无法避免的,所以导致任何运放都会有失调电压。

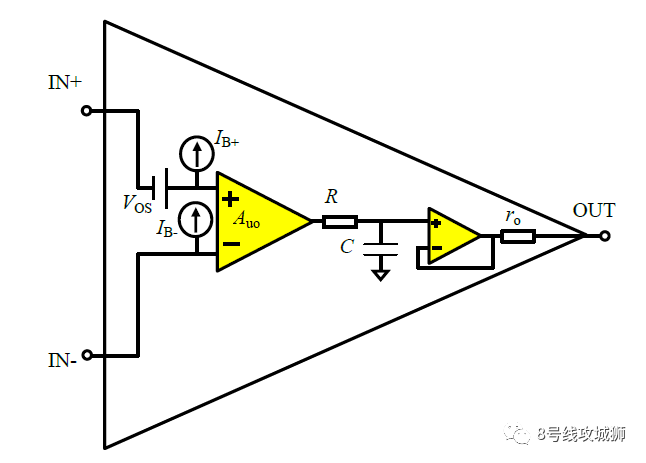

大多数运放的输入级由差分放大器组成。如图3所示,其中Q1(+或同相输入端)和Q2(-或反相输入端)可以是BJT、FET或MOS晶体管。运算放大器的输入端是这些晶体管的基极(BJT)或栅极(FET、MOS)。

理想情况下,电路的每个支路都是平衡的,这样一半的电流流过每个晶体管(IQ1=IQ2=IREF/2),并且反相和同相输入处于相同的电位。而实际中R、Q1和Q2中的不匹配会使该电流失衡,造成晶体管的基极(栅极)电压变得不相等,从而产生小的差分电压VOS。

图3 放大器输入级电路

②芯片封装工艺导致

大多数芯片封装过程不会影响失调电压。但是少数情况下封装过程会影响运放的失调电压,比如封装过程中芯片受到微小的应力影响。

③对策

常用的处理方法是在运放生产后进行测试与校准,或者在输出级使用斩波等威廉希尔官方网站 改善运放的失调电压。

产品使用上直接选择VOS远小于被测直流量的放大器,或者通过运放的调零措施消除这个影响。如果我们只关心被测信号中的交变成分,直接可以在输入端和输出端增加交流耦合电路,将其消除。

调零方法:有些运放有两个调零端,一般数据手册会有讲如何进行调零,我们只需要根据要求接电位器调零即可。对没有调零端的运放,可采用外部的输出调零或者输入调零。

03

总结

当然上面的内容其实我们只需要了解即可,重点知道输入失调电压越小越好,但是实际使用中有时候并不需要太小的,根据实际情况进行选择即可,因为越小意味着价格越贵。

产生VOS的原因主要是由于硅芯片制造过程中输入晶体管和元件不匹配,以及封装过程中施加在芯片上的应力影响。这些影响共同导致流经输入电路的偏置电流失配,导致运算放大器输入端出现电压差。通过增加匹配、改进封装材料和工艺,可降低VOS。

-

模拟电路

+关注

关注

125文章

1556浏览量

102721 -

运算放大器

+关注

关注

215文章

4931浏览量

172850 -

MOS晶体管

+关注

关注

0文章

18浏览量

7689 -

失调电压

+关注

关注

0文章

123浏览量

13842 -

差分电压

+关注

关注

0文章

15浏览量

9579

发布评论请先 登录

相关推荐

【模拟电路设计】输入失调电压

【模拟电路设计】输入失调电压

评论