《Vivado Design Suite 用户指南:编程和调试》

文档涵盖了以下设计进程:

硬件、IP 和平台开发:为硬件平台创建 PL IP 块、创建 PL 内核、功能仿真以及评估 AMD Vivado 时序收敛、资源使用情况和功耗收敛。还涉及为系统集成开发硬件平台。本文档中适用于此设计进程的主题包括:

-

第 9 章:设计调试

-

第 10 章:系统内逻辑设计调试流程

-

第 11 章:在硬件中调试逻辑设计

-

第 12 章:在波形查看器中查看 ILA 探针数据

-

第 13 章:实现后的设计调试

开发板系统设计:通过原理图和开发板布局设计 PCB。还包含功耗、散热以及信号完整性注意事项。本文档中适用于此设计进程的主题包括:

-

第 4 章:器件编程

-

第 5 章:在 Vivado 中执行远程调试

-

第 6 章:配置存储器器件编程

-

第 7 章:高级编程功能

-

第 8 章:串行矢量格式 (SVF) 文件编程

-

第 14 章:串行 I/O 硬件调试流程

-

第 16 章:在硬件中调试串行 I/O 设计

本文选取了“第3章:生成比特流或器件镜像”部分进行分享。如果您希望获取完整版用户指南,请至文末扫描二维码进行下载。

生成比特流或器件镜像

在生成比特流或器件镜像之前,请复查其设置,确保这些设置对于您的设计都正确无误,这一点至关重要。

AMD Vivado IDE 中的比特流和器件镜像设置分为 2 种类型:

-

比特流或器件镜像文件格式设置。

-

器件配置设置。

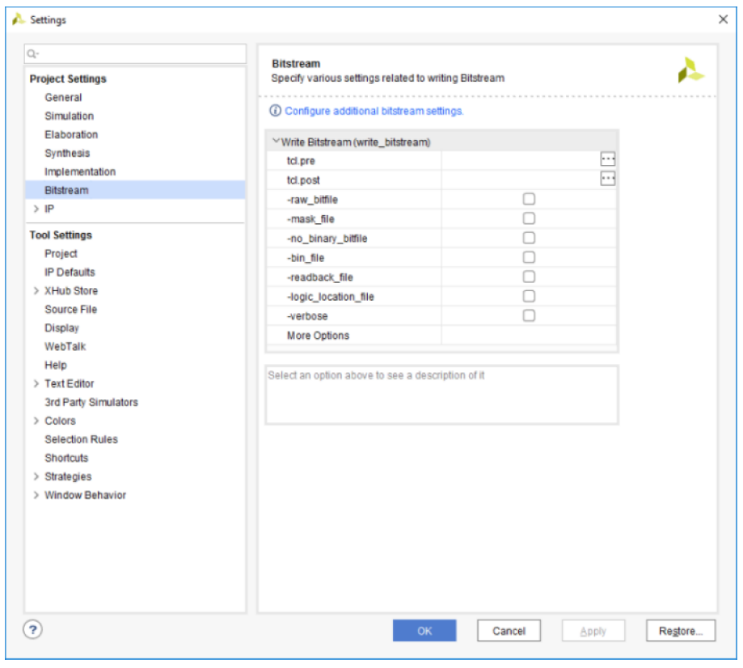

在 Vivado Flow Navigator 中依次选择“Settings ” → “Bitstream”(设置 > 比特流),或者选择“Flow” → “Settings” → “Bitstream Settings”(流程 > 设置 > 比特流设置)菜单选项以打开“Bitstream Settings”(比特流设置)弹出窗口(如下图所示)。只要设置正确,即可使用 write_bistream Tcl 命令或者使用 Vivado Flow Navigator 中的“Generate Bitstream”(生成比特流)按钮来生成比特流数据文件。

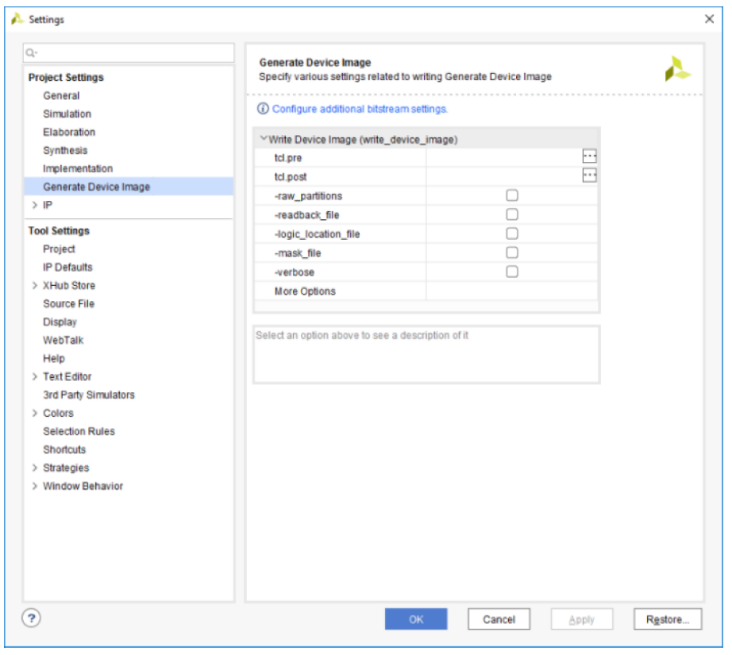

如果以 AMD Versal 器件为目标,则会生成可编程器件镜像 (.pdi),而不是比特流文件。更改器件镜像设置的过程与先前架构类似,但菜单选项、Tcl 命令和可用设置会有所不同。

要访问器件镜像设置,请依次选中 Vivado Flow Navigator 中的“Settings” → “Generate Device Image”(设置 > 生成器件镜像),或者选中“Flow” → “Settings” → “Generate Device Image Settings...”(流程 > 设置 > 生成器件镜像设置)菜单选项,这样即可在“Settings”(设置)弹出窗口中打开“Device Image”(器件镜像)部分(请参阅下图)。要生成器件镜像数据文件,可使用 write_device_image Tcl 命令,或者使用 Vivado Flow Navigator 中的“Write Device Image”(写入器件镜像)按钮。

图:比特流设置面板

图:生成器件镜像设置面板

更改比特流文件格式设置

默认情况下,write_bitstream Tcl 命令仅生成二进制比特流 (.bit)文件。(可选)您可通过使用以下命令开关来更改 write_bitstream Tcl 命令写出的文件格式:

-

-raw_bitfile:(可选)此开关会导致 write_bitstream 编写原始比特文件 (.rbt),其中所含信息与二进制比特流文件中所含信息相同,但格式为 ASCII。输出文件名为

.rbt。 -

-mask_file:(可选)编写掩码文件 (.msk),其中包含有关比特流文件中配置数据所在位置的掩码数据。此文件可用于判定比特流中哪些位应与回读数据进行比较和验证。如果掩码位为 0,那么应根据比特流数据验证该位。如果掩码位为 1,那么不应验证该位。输出文件名为

.msk。 -

-no_binary_bitfile:(可选)不编写二进制比特流文件 (.bit)。如果要生成 ASCII 比特流文件或掩码文件或者要生成比特流报告(而不生成二进制比特流文件),请使用此命令。

-

-logic_location_file:(可选)创建 ASCII 逻辑位置文件 (.ll),以显示锁存器、触发器、LUT、块 RAM 和 I/O 块输入输出的比特流位置。这些位元可供位置文件中的帧和位编号引用,以帮助您观察 FPGA 寄存器的内容。

-

-bin_file:(可选)创建二进制文件 (.bin),其中仅包含器件编程数据,不含标准比特流文件 (.bit) 中找到的报头信息。

-

-reference_bitfile

:(可选)读取引用比特流文件,并输出增量比特流文件,其中仅含不同于指定引用文件的内容。此部分比特流文件可用于对含更新设计的现有器件进行增量编程。

向下滑动查看

更改器件镜像 (PDI) 文件格式设置

默认情况下,write_device_image Tcl 命令仅生成 1 个 .pdi 文件。(可选)您可通过使用以下命令开关来更改write_device_image Tcl 命令写出的文件格式:

-

-force(可选):覆盖现有文件。

-

-verbose(可选):打印 write_device_image 选项。

-

-raw_partitions(可选):写入原始 CFI 和 NPI 分区文件(.rnpi 和 .rcdo)

-

-mask_file(可选):写入掩码文件 (.msk)

-

-logic_location_file(可选):写入逻辑位置文件 (.ll)

-

-cell

(可选):仅为指定单元创建部分器件镜像。 -

-no_pdi:不生成 pdi 文件。仅生成原始分区文件后即停止操作。

-

-no_partial_pdifile(可选):不为 Dynamic Function eXchange 设计写入部分 pdi 文件。

-

-quiet(可选):忽略命令错误。

-

(必需):要写入的 .pdi 文件名。

向下滑动查看

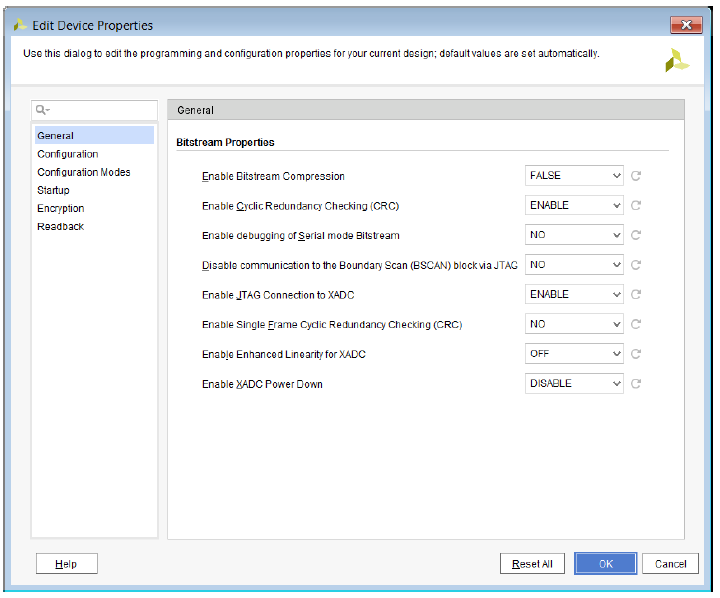

更改器件配置比特流设置

您可更改的最常见的配置设置归为器件配置设置类别。这些设置是器件模型的属性,您可使用“Edit Device Properties”(编辑器件属性)对话框来为选定的已综合或已实现的设计网表更改这些设置。以下步骤描述了如何使用此方法来设置各种比特流属性:

1.选择“Tools” → “Edit Device Properties”(工具 > 编辑器件属性)。

2.在“Edit Device Properties”对话框中,选择左侧列中的类别之一(请参阅下图)。

3.将属性设为期望的值,然后单击“OK”(确定)。

4.依次选择“File” → “Constraints” → “Save”(文件 > 约束 > 保存)以将更新后的属性保存到目标 XDC 文件中。

您也可以在 XDC 文件中使用 set_property 命令来设置比特流属性。例如,以下提供了如何更改 start-up DONE cycle 属性的示例:

set_property BITSTREAM.STARTUP.DONE_CYCLE 4 [current_design]

在 Vivado 模板中提供了更多示例和模板。“器件配置比特流设置”描述了所有器件配置设置。

获取完整版用户指南,请扫描二维码进行下载

原文标题:Vivado Design Suite 用户指南:编程和调试

文章出处:【微信公众号:Xilinx赛灵思官微】欢迎添加关注!文章转载请注明出处。

-

赛灵思

+关注

关注

32文章

1794浏览量

131216 -

Xilinx

+关注

关注

71文章

2165浏览量

121161

原文标题:Vivado Design Suite 用户指南:编程和调试

文章出处:【微信号:赛灵思,微信公众号:Xilinx赛灵思官微】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Vivado之实现布局布线流程介绍

AMD Vivado Design Suite 2024.2全新推出

U50的AMD Vivado Design Tool flow设置

MicroBlaze V软核处理器的功能特性

PLC远程编程调试平台是什么

Vivado Design Suite 用户指南:编程和调试

Vivado Design Suite 用户指南:编程和调试

评论