Zynq系列处理器包含了ARM和FPGA,与ARM处理器+FPGA这种两个处理器相比最大的特点就是两种结构的数据交互在芯片内部进行。既节约了接口,有提升了交互速度。

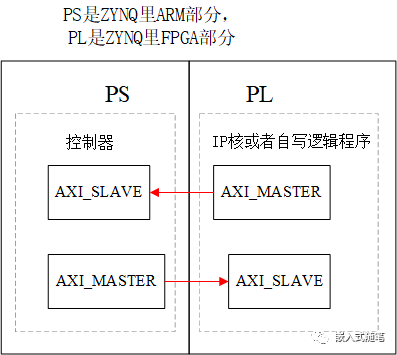

内部交互主要是使用AXI接口。AXI是一种主从接口。虽然看起来很复杂,但也是主机发送地址然后读写数据。PS端通过芯片内控制器来发送或者接收AXI接口信号,和SPI之类的主从接口一样。

PL端通过IP核或者自写的逻辑程序收发AXI接口程序。

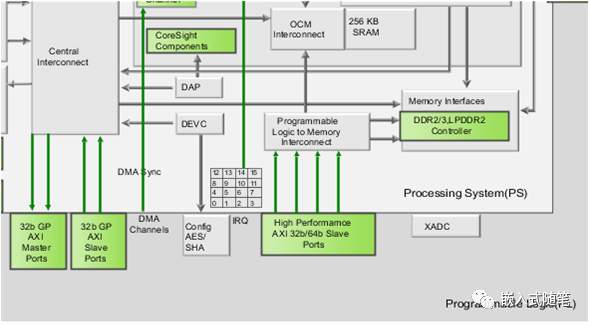

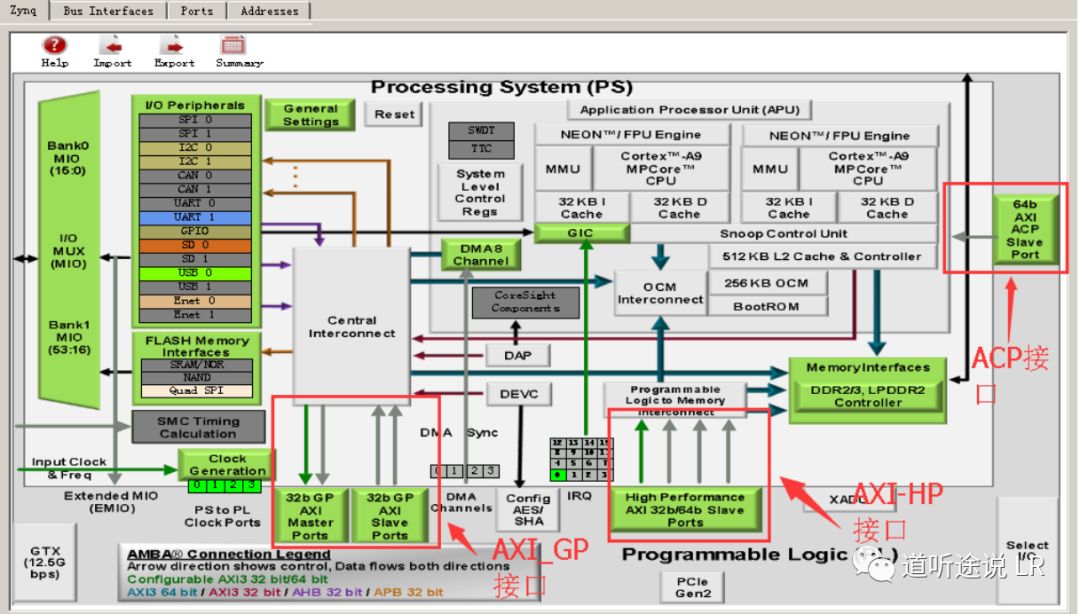

通过如下的图(ZYNQ7000系列的)可以看出PS端的GP AXI连接一个控制器,HP AXI连接一个控制器。

如上图所示,这个型号的GP AXI可以作为主机也可以作为从机,来与PL端交互数据。HP AXI的传输速度快,通过Programmable Logic to Memory Interconnect可以连接到DDR控制器,可以访问DDR数据。流程是:PL端的逻辑程序发出AXI接口的时序信号,Programmable Logic to Memory Interconnect接收到后转化成可以访问DDR控制器的信号来读写数据。

-

处理器

+关注

关注

68文章

19265浏览量

229670 -

FPGA

+关注

关注

1629文章

21729浏览量

603034 -

接口

+关注

关注

33文章

8580浏览量

151030 -

Zynq

+关注

关注

10文章

609浏览量

47176 -

AXI

+关注

关注

1文章

127浏览量

16625

发布评论请先 登录

相关推荐

Xilinx zynq AXI总线全面解读

玩转Zynq连载34——[ex54] 基于Zynq的AXI GP总线的从机接口设计

玩转Zynq连载37——[ex56] 基于Zynq的AXI HP总线读写实例

关于Zynq的理论部分

为Xilinx® Zynq®UltraScale™系列多处理器中的VCCINT_VCU轨供电

Zynq系列处理器中AXI接口的使用

Zynq系列处理器中AXI接口的使用

评论