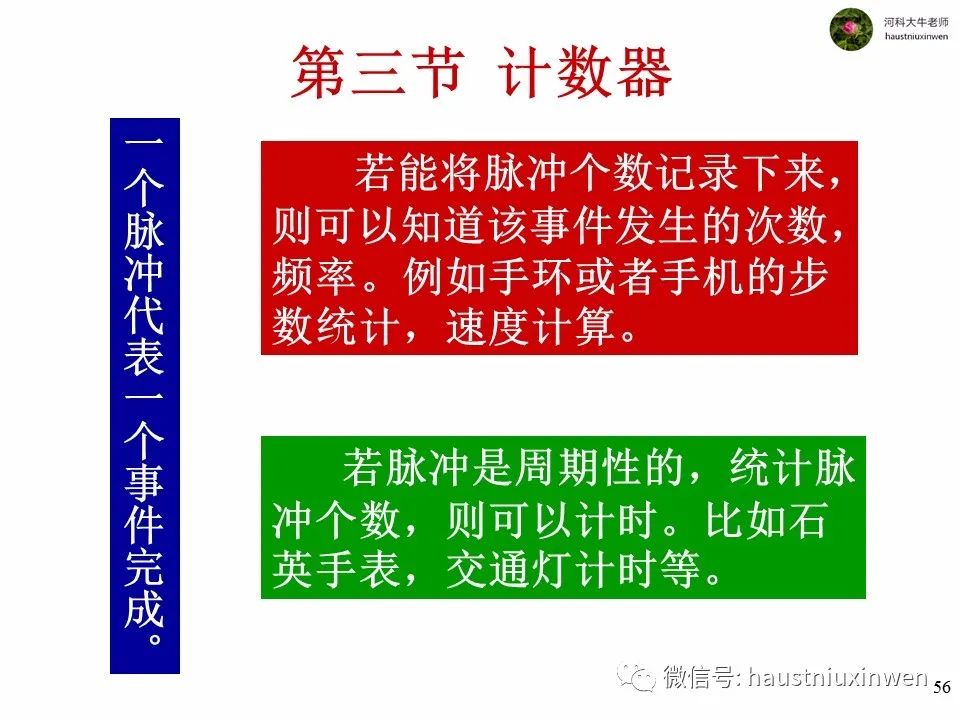

在数字系统中,使用得最多的时序电路差不多就是计数器了。计数器不仅能够用于对时钟脉冲计数,还可以用于分频、定时、产生节拍脉冲、产生脉冲序列以及进行数字运算等等。

其实,计数也是一种最简单最基本的运算,就像我们心里默念的计数一样。不过不同的是,计数器是有一定频率的计数,具有一定的时间间隔,而我们心里默念的计数的时间间隔不一样罢了(也就是不够准确的啦),而计数器就是实现这种运算的逻辑电路,主要是通过对时钟(上升)脉冲的个数进行计数的。

计数器在我们身边也很普遍,比如手机中自带的跑步的计时器、电脑定时关机等等;所以,熟悉掌握计数器,不仅对于学习 Verilog 非常有用,而且,还能锻炼我们的逻辑能力和更深刻地理解数字电路的工作原理,从而对科技更加感兴趣!

一、计数器的 Verilog 代码实现和 RTL 电路实现

下面是计数器的 Verilog 代码实现:

module Counters(

input Clk,

input Up, // 可增可减(可逆)计数器

output reg [7:0] Cout = 8'b0000_0000 // 8 位计数器

);

always @(posedge Clk)

if (Up)

Cout <= Cout + 1'b1;

else

Cout <= Cout - 1'b1;

endmodule

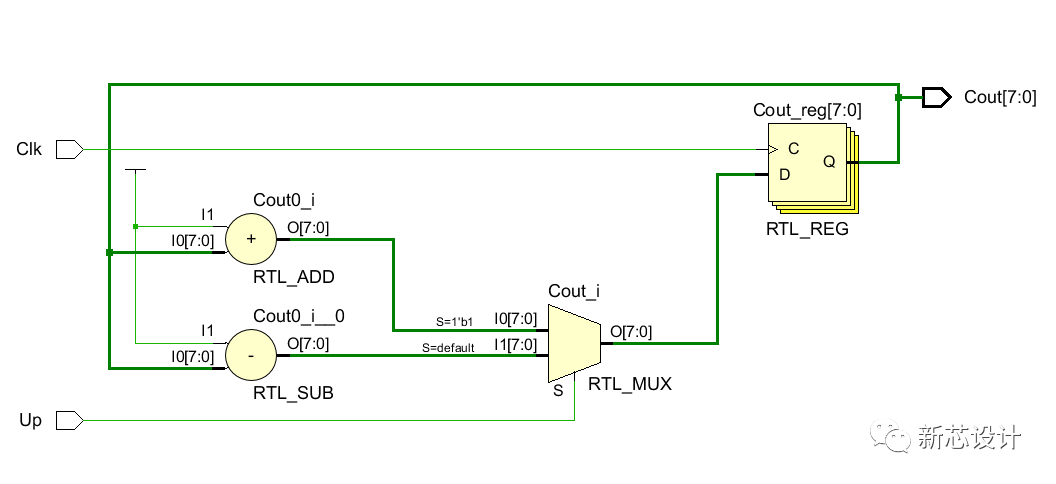

下面是计数器的 RTL 电路实现:

计数器的 RTL 电路图

时钟信号:Clk(时钟信号,就是电路的“心脏”,不可或缺);

复位信号:rst_n(复位信号,也是一个合格的电路不应该缺少的一个输入信号,当复位信号为低电平时,输出全部置零,这就是所谓的低电平有效)当复位信号为高电平时,开始计数,每一个时钟信号的上升沿到来就计一次数,每计数满 256 个时钟周期为一个输出循环,输出置零,然后重新计数;当然,这里为了更好地读懂代码,并没有加入复位信号啊哈哈哈嗝。

计数值信号:Cout(显示计数值,根据自己设计的需要,可以对位数进行设置,比如最大计数值为 6,那么位数就可以设置为 3 bits)

其实,这个既是计数器,又能当分频器,而且还能当计时器哟(再者还可以当闹钟功能)这三者其实都是息息相关的,但是博主并没有把分频器和定时器的功能加上去,其实只需要增加一两个信号即可,小伙伴们能否想到怎么添加,从而使得这个程序既有计数器的功能,也有分频器的功能和定时器的功能呢?

-

计数器

+关注

关注

32文章

2255浏览量

94433 -

时序电路

+关注

关注

1文章

114浏览量

21691 -

RTL

+关注

关注

1文章

385浏览量

59746 -

计时器

+关注

关注

1文章

420浏览量

32671 -

Verilog设计

+关注

关注

0文章

20浏览量

6516

发布评论请先 登录

相关推荐

招聘:数字电路设计师

数字电路设计的基本方法有哪些

基于LabVIEW的数字电路设计和仿真

数字电路组成的计数器原理电路

基于Verilog的经典数字电路设计—计数器

基于Verilog的经典数字电路设计—计数器

评论