先简单介绍下超导体的几个重要物理效应,

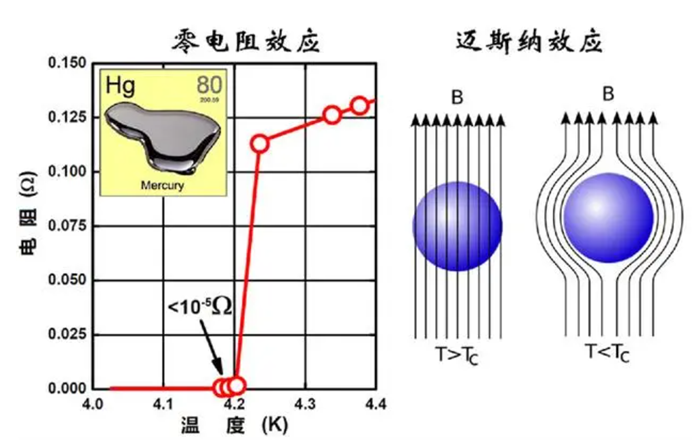

1)零电阻效应

在超导体的临界温度以下,其电阻值降为零。铜的电阻率为1.7x10^-8 Oh*m, 虽然其数值较小,但是在芯片设计中要考虑metal routing的电阻影响,过长的金属走线会带来一定的电压降,可能引起IR drop的问题,使得电路中实际的电源电压不满足要求,超导体则不会存在该问题。基于超导体的零电阻效应,电流流经超导体时,不会发生衰减,有望应用于长距离直流传电和强磁体。

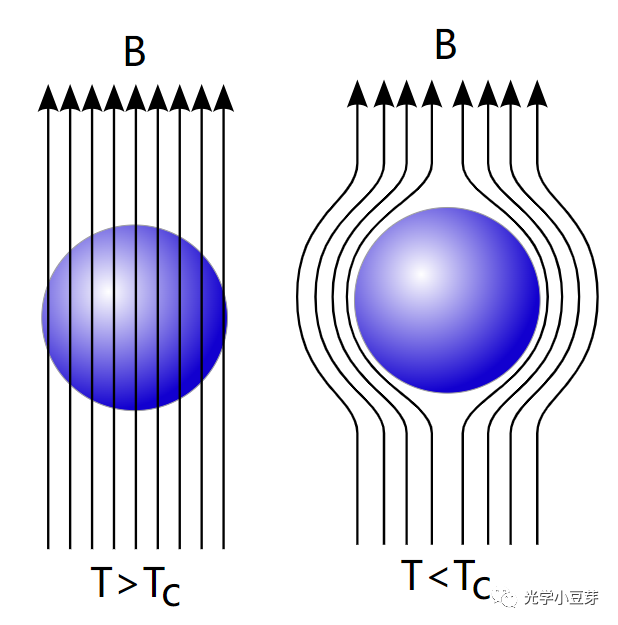

2)迈斯纳效应

所谓迈斯纳效应(Meissner Effect), 即完全抗磁性,在临界温度以下,磁力线无法穿过超导体,如下图所示。微观的解释是,超导体内的库珀对在表面形成电流,表面电流产生的磁场与外加磁场在超导体内完全抵消。我们在一些视频中看到的超导体悬浮在磁场的现象,即对应迈斯纳效应。磁悬浮列车正是迈斯纳效应的一个重要应用。

3)约瑟夫森效应

所谓约瑟夫森效应(Josephson Effect),是指在超导体-绝缘体-超导体形成的三明治结构中(也称为约瑟夫森结),无外加电压时,电子库珀对可以通过量子隧穿越过中间的绝缘体,形成超导电流,如下图所示。当施加直流电压时,则会产生随时间变化的交变电流。超导量子计算正是通过基于约瑟夫森效应构建的超导电路来实现。

在一些公众号文章中,鼓吹室温超导可以大大降低芯片功耗。我们常说的芯片,其实是半导体芯片的简称。而芯片的底层元器件是CMOS晶体管,通过在半导体中进行掺杂,形成P区和N区,进而形成不同功能的器件。不同元器件之间通过金属互联,如果使用超导体取代这些金属互连线,则可以有效降低IR drop的风险。除此之外,室温超导体无法插足现有的半导体芯片大厦。

对于芯片功耗,可以主要分为以下几部分,

1)翻转功耗(switching power)

翻转功耗,即电路对负载电容充放电所消耗的功率,计算公式为,

2)短路功耗(short-circuit power)

在晶体管翻转的过程中,对应波形上升沿和下降沿的过程中,会存在P管和N管都处于导通的状态,此时电流从VDD流向GND, 产生功耗,如下图所示。短路功耗和翻转功耗都属于动态功耗(dynamic power)。

3)漏电功耗(leakage power)

漏电功耗,即电路在静态时由于一些寄生的漏电引起的功耗,对应晶体管不同掺杂区域形成PN结通电后的微弱电流流动。CMOS管的漏电主要包括:a)亚阈值漏电流Isub, b)栅极感应漏电流Igidl和Igisl,c)栅极漏电流Igate, d)晶体管反偏电流,如下图所示。

随着工艺节点的提升,相同面积中的晶体管数目增加,漏电功耗在芯片整体功耗所占的比例越来越高,超过50%,如下图所示。

对于高速光模块,功耗大体分为三部分,即DSP、激光器和interwetten与威廉的赔率体系 电路相关。下图为400G ZR的功耗分解图,其中DSP几乎占总功耗的半壁江山,driver和TIA占27%,可调谐激光器占12%。这也是Linear drive概念受到青睐的原因,干掉功耗大户DSP。400G光模块的典型功耗是8-10W。

需要注意的是,对于硅光方案,其外部DFB光源的功率都比较大, 典型值为16-18dBm,考虑到DFB激光器本身的转换效率(wall-plug efficiency),对应的功耗较大。这也是CPO模块中光源外置的主要原因之一,可以降低激光器散热对硅光芯片的影响。对于像Intel的异质集成光源方案,其光功率一般不会太高。

最后再简单聊一下,如果室温超导得以实现,量子计算是否会大范围应用,取代经典计算机?一方面,室温超导如果实现,整个量子系统不再需要维持在低温状态下,但是仍然需要解决环境温度扰动对量子态的影响。另一方面,室温超导的实现将带来量子系统的简化,量子比特的数目将得以大幅度增加(IBM目前实现了433个量子比特的量子处理器),量子计算的商业应用将会大大加速,有望从实验室真正走向大众。但是从材料的研发成功,到应用到计算芯片中,还有很长的路要走,道阻且长,行则将至。

对于芯片从业人员,没有必要恐慌,保持关注即可。目前的芯片基础是半导体,不是超导体。即便室温超导真的得以实现,半导体芯片依然会是主流,室温超导中短期不会对芯片行业产生影响。如何有效降低芯片功耗,才是芯片工程师们更需要关注的问题。

-

芯片设计

+关注

关注

15文章

1017浏览量

54886 -

电源电压

+关注

关注

2文章

989浏览量

23975 -

CMOS晶体管

+关注

关注

0文章

11浏览量

10208 -

电容充放电

+关注

关注

0文章

94浏览量

5842 -

室温超导

+关注

关注

1文章

11浏览量

90

发布评论请先 登录

相关推荐

高温超导滤波器的组成

深度解析室温超导实验

室温超导新材料发现者回应质疑

室温超导威廉希尔官方网站 为何颠覆物理学

常温超导最新进展 韩国室温超导体“LK-99”撤回论文

若室温超导实现世界会发生啥改变

十余家上市公司辟谣室温超导

“室温超导”真的来了吗?韩国团队称发现全球首个室温常压超导体

什么是室温超导?室温超导被发现会给人类带来多大的改变?

室温超导材料,真的假的?

室温超导:无价之宝!

室温超导是否可以帮助降低芯片功耗呢?

室温超导是否可以帮助降低芯片功耗呢?

评论