相关阅读:

RA2快速设计指南 [2] MCU工作模式和选项设置存储器

5. 时钟电路

RA2 MCU具有六个振荡源。其中有五个可以用作主系统时钟源。剩下的一个专用于独立看门狗定时器。在典型系统中,主时钟由外部晶体或时钟驱动。将此输入指向内部选择器和分频器,在此进一步指向主系统时钟(ICLK)、闪存时钟、CPU时钟和外设模块时钟。此外,时钟分配也包括ADC和USB的外设时钟。有关时钟生成电路框图的信息,请参见《硬件手册》中的“时钟生成电路”一章。

每个时钟都有特定的容差和时序值。有关频率和时钟时序规范的信息,请参见《硬件手册》中“电气特性”一章的“交流特性”部分。有关各种时钟频率之间关系的信息,请参见《硬件手册》中的“时钟生成电路”一章。

表5. RA2振荡源

2. 仅RA2A1产品支持USB时钟。

3. RA2A1产品的闪存时钟(FCLK)是独立于MOSC存在的,也可以通过MOSC、SOSC、HOCO、MOCO或LOCO生成。

4. RA2E2产品不支持。

一些产品如RA2E2不支持选择外部振荡器或外部时钟。此种情况下,主时钟的振荡源仅限于片上振荡器。

5.1 复位条件

复位后,RA2 MCU开始以中速片上振荡器(MOCO)作为主时钟源运行。复位时,默认情况下主振荡器处于关闭状态。HOCO和IWDT可能处于打开或关闭状态,具体取决于选项设置存储器中的设置(请参见后文第4节)。

5.2 时钟频率要求

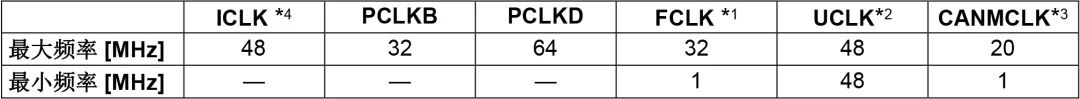

最小和最大频率如下表所示。有关详细信息,请参见《硬件手册》中“时钟生成电路”一章的“概述”部分,其中包括外部和内部时钟源规范。更多详细信息,请参见《硬件手册》中“电气特性”一章的“交流特性”部分。

表6. RA2 MCU内部时钟的频率范围

注1. 仅限RA2A1产品。对ROM或数据闪存进行编程或擦除操作时,FCLK的运行频率必须至少为1 MHz。

2. 仅限支持USB外设功能的产品。

3. 仅限支持CAN外设功能的产品。

4. RA2E1、RA2E2 和 RA2L1对 ROM 或数据闪存进行编程或擦除操作时,ICLK 的运行频率必须至少为1 MHz。

5.2.1 USB通信要求

全速USB 2.0模块(USBFS)需要48 MHz 的 USB 时钟信号(UCLK)。

对于支持USBFS模块的RA2产品,HOCO为UCLK的时钟源。因此当使用USBFS模块时,HOCO必须配置为48 MHz。

5.2.2 ROM或数据闪存的编程和擦除要求

RA2A1产品的FCLK必须至少为1 MHz才能在内部ROM和数据闪存上执行编程和擦除。

其他RA2产品的ICLK必须至少为1 MHz才能在内部ROM和数据闪存上执行编程和擦除。

5.3 降低时钟生成电路(CGC)的功耗

为了帮助节省功耗,请尽可能将所有未使用的时钟的分频器设置为最大可能值。另外,如果不使用时钟,请通过设置适当的寄存器来确保时钟已停止。下表显示了用于控制每个时钟源的寄存器。

表7. 时钟源配置寄存器

注1:RA2E2产品不支持。

5.4 写入系统时钟控制寄存器

写入系统时钟分频控制寄存器(SCKDIVCR)和系统时钟源控制寄存器(SCKSCR)中的各个位域时,应格外小心。

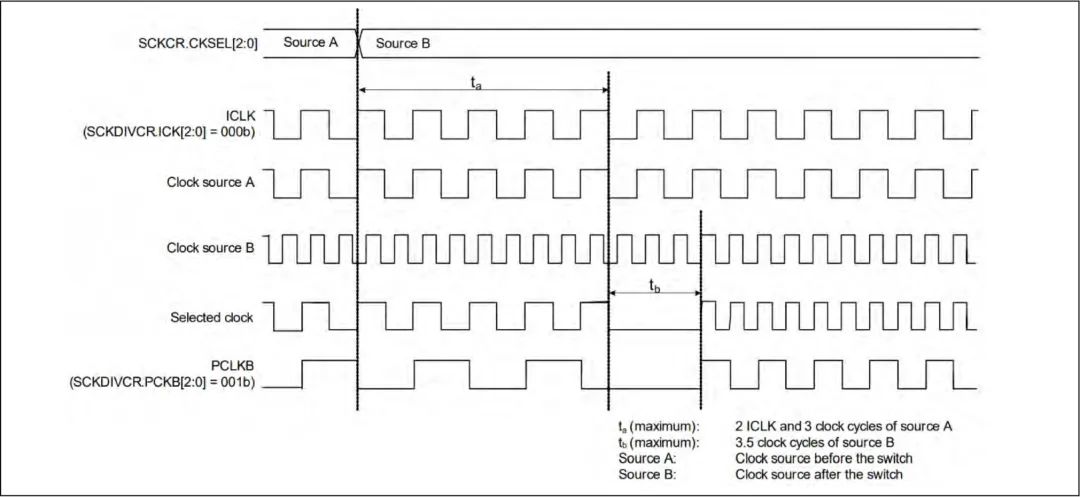

当外围模块时钟的时钟源更改为其他时钟源时,在时钟源切换期间,外围模块时钟周期会变长。详见图8。因此,必须在指令处理中增加延迟,以确保时钟在切换时钟源时仍保持稳定。

为保证时钟频率改变后的处理准确无误,首先写入相关的时钟控制寄存器改变频率,再从寄存器中读取值,最后进行后续处理。

图8. 切换时钟源的时序

5.5 时钟设置示例

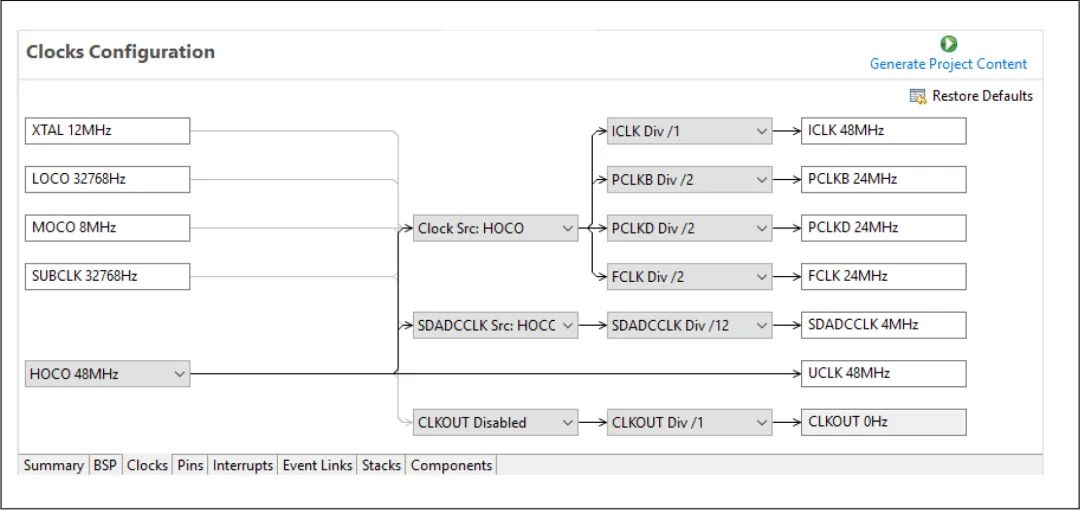

Renesas FSP为RA2A1 MCU提供了一个简单的可视化时钟配置工具,如下所示。此配置器可配置板级支持包中的代码,以根据用户的选择初始化时钟生成电路,并按照MCU硬件手册中的说明进行适当的配置。

图9. 使用 Renesas FSP配置器进行时钟设置

5.6 HOCO精度

RA2 MCU内部高速片上振荡器(HOCO)的运行频率为24 MHz、32 MHz、48 MHz,精度为+/-2%或更高。HOCO的精度规格适用于各种环境工作温度(Ta)范围。有关详细信息,请参见《硬件手册》中“电气特性”章节的内容。

HOCO可以用作时钟生成电路的输入。当以这种方式使用HOCO时,不需要外部振荡器。当因空间限制或其他限制而需要减少PCB设计中的元件数量时,这可能是一个优势。不过,此时会因时钟精确度问题而产生性能影响和限制,因此应针对您的应用进行评估。

RA2E2产品没有外部晶振和外部时钟输入,必须选择其内部时钟(HOCO、MOCO、LOCO)作为主系统时钟。

5.7 闪存接口时钟

RA2A1产品对内部闪存(ROM和DF)进行编程和擦除操作以及从数据闪存读取数据时,闪存接口时钟(FCLK)用作运行时钟。而其他RA2产品进行编程和擦除操作时,ICLK用作运行时钟。

因此,相关时钟的频率设置会直接影响从数据闪存读取数据所需的时间。如果用户的程序正在从数据闪存中读取数据,或者正在对内部闪存执行编程或擦除操作,则建议使用最大FCLK/ICLK频率。

当写入或擦除代码闪存(ROM)或数据闪存时,时钟必须以至少1 MHz的频率运行。请注意,时钟频率对从ROM读取数据或对RAM进行读写操作没有任何影响。

5.8 电路板设计

有关使用CGC的更多信息和电路板设计建议,请参见《硬件手册》中“时钟生成电路(CGC)”一章的“使用注意事项”部分。

通常,晶体谐振器及其负载电容应尽可能靠近MCU时钟引脚(XTAL/EXTAL、XCIN/XCOUT)放置。避免在晶体谐振器和MCU之间连接任何其他信号走线。尽量减少每条走线上使用的连接通孔数量。

5.9 外部晶体谐振器选择

大多数RA2产品的外部晶体谐振器可以用作主时钟源。外部晶体谐振器可跨MCU的EXTAL和XTAL引脚连接。外部晶体谐振器的频率必须处于主时钟振荡器的频率范围内。

晶体谐振器的选择在很大程度上取决于各个独特的电路板设计。由于适合与RA2 MCU产品配合使用的可用晶体谐振器的选择可能很多,因此请仔细评估所选晶体谐振器的电气特性,以确定具体的实现要求。

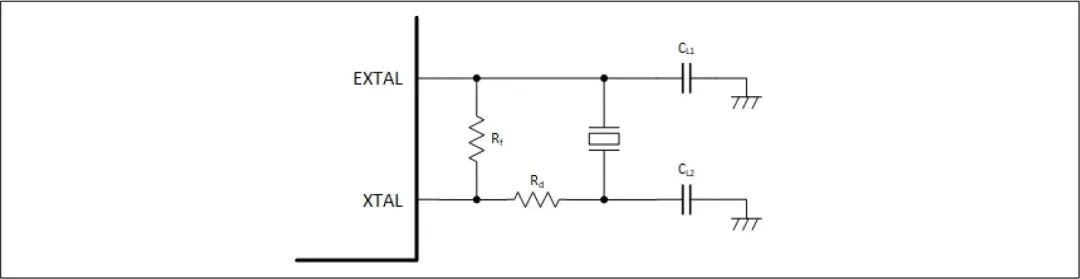

下图给出了典型的晶体谐振器连接示例。

图10. 晶体谐振器连接示例

选择晶体谐振器和相关电容时,必须仔细评估。如果晶体谐振器制造商有相关建议,可以添加外部反馈电阻(Rf)和阻尼电阻(Rd)。

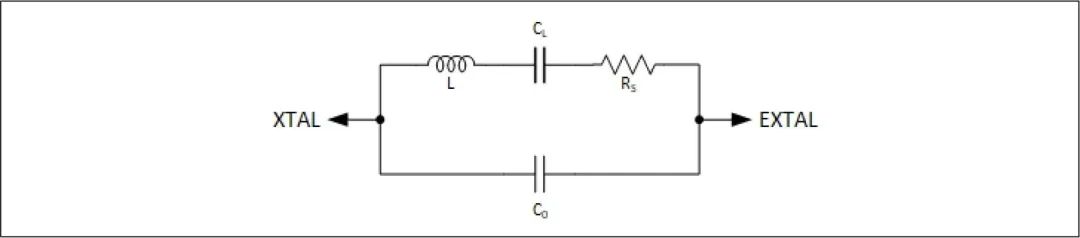

图11. 晶体谐振器的等效电路

CL1和CL2的电容值选择会影响内部时钟的精确度。要了解CL1和CL2值的影响,应使用上图中晶体谐振器的等效电路来interwetten与威廉的赔率体系 该电路。为了获得更准确的结果,还应考虑与晶体谐振器元件之间的布线相关的杂散电容。

5.10 外部时钟输入

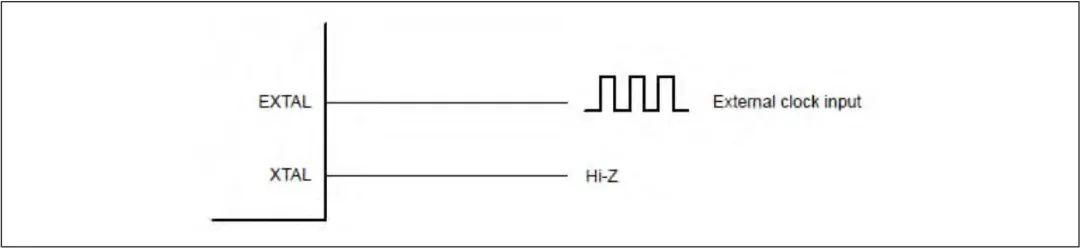

大多数RA2产品的数字时钟输入可以用作主时钟源。图12给出了连接外部时钟输入的示例。若使用外部时钟信号运行振荡器,请将MOMCR.MOSEL位设为1。XTAL引脚变为高阻抗。

图12. 晶体谐振器的等效电路

注:外部时钟频率的输入操作只能在主时钟振荡器停止时运行。请不要在主时钟振荡器停止位(MOSCCR.MOSTP位)为0时更改外部时钟频率的输入。

来源:RA2快速设计指南 [3] 时钟电路(上)、RA2快速设计指南 [4] 时钟电路(下)

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理

审核编辑 黄宇

-

时钟电路

+关注

关注

10文章

236浏览量

50721

发布评论请先 登录

相关推荐

RA2快速设计指南 [3] 时钟电路

RA2快速设计指南 [3] 时钟电路

![<b class='flag-5'>RA2</b><b class='flag-5'>快速</b>设计<b class='flag-5'>指南</b> [9] 一般布线实践与参考资料(完结)](https://file1.elecfans.com/web2/M00/A3/1F/wKgZomUDyFSAT6fEAABMTVrCfpI979.png)

![<b class='flag-5'>RA2</b><b class='flag-5'>快速</b>设计<b class='flag-5'>指南</b> [7] 模块停止功能,中断控制单元与低功耗](https://file1.elecfans.com/web2/M00/A4/8C/wKgaomUDyOyAOoMAAAI-ZvuSIMY086.jpg)

![<b class='flag-5'>RA2</b><b class='flag-5'>快速</b>设计<b class='flag-5'>指南</b> [6] 寄存器写保护和I/O端口配置](https://file1.elecfans.com/web2/M00/A4/8C/wKgaomUDyRmANKEWAABPNEaw3Rg626.jpg)

![<b class='flag-5'>RA2</b><b class='flag-5'>快速</b>设计<b class='flag-5'>指南</b> [5] 存储器](https://file1.elecfans.com/web2/M00/A3/21/wKgZomUDyXWAV5qfAAEgG1i2Pgo328.jpg)

![<b class='flag-5'>RA2</b><b class='flag-5'>快速</b>设计<b class='flag-5'>指南</b> [4] 复位要求和复位<b class='flag-5'>电路</b>](https://file1.elecfans.com/web2/M00/A3/21/wKgZomUDyc2AAMHWAAF8yDw8WIc920.jpg)

评论