随着现代集成电路工艺的发展,芯片制成越来越来精密,出现缺陷的可能性也越来越高,有时候一个微不足道的影响就可能导致芯片报废,为了能有效的检测出生产中出现的废片,就需要用到扫描链测试(scan chain),DFT可测试性设计中的扫描链测试发展至今,已经有了成熟的设计和制造流程。本文就对扫描链测试过程做简单介绍。

扫描链测试原理

scan chain的基本原理是将设计中所有触发器连成一条链,用统一的scan clk驱动,这样可以将预先设计好的scan pattern送入芯片中,然后开启capture使能,这样每个触发器Q端输出传入它们所驱动的组合电路,scan chain中的下一级触发器D端就会捕获这个组合电路的输出,然后capture失效,这组向量与工具预先计算好的预期相比较,以此为依据来判断芯片中是否有制造错误

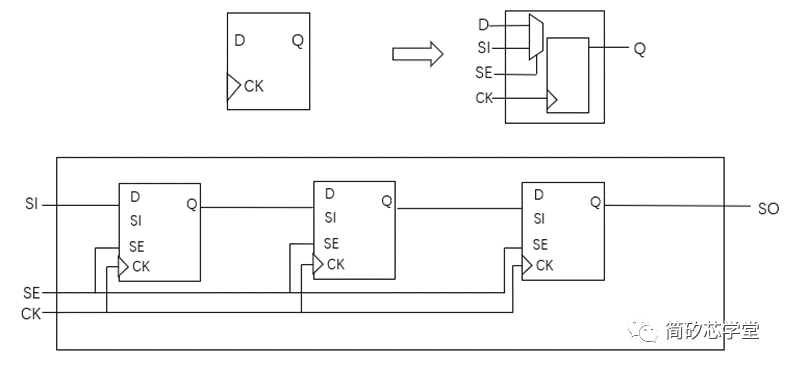

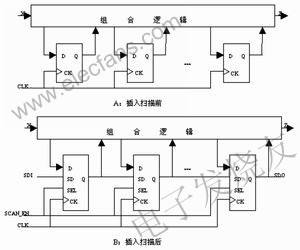

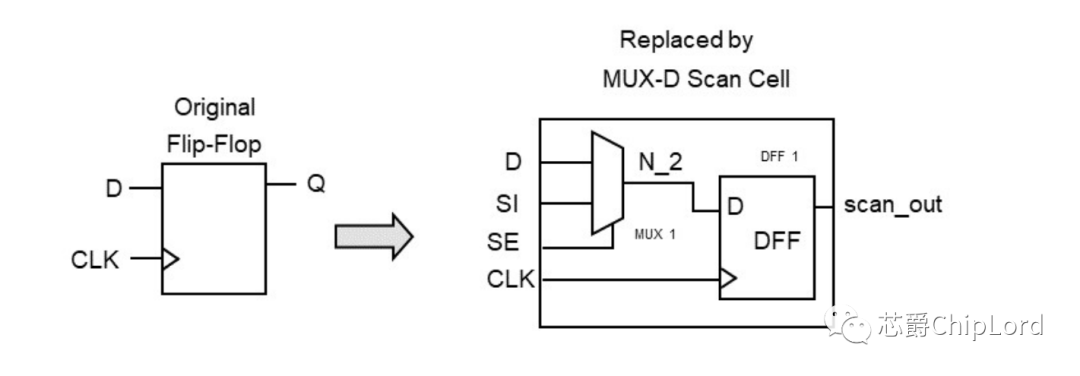

下图即为scan前和scan后的DFF,这是一个简单的示意图,含有三个扫描寄存器。其实就是替换成带有scan逻辑的DFF,当scan_en有效时,scan逻辑就会从scan-in穿过DFF到达scan-out,多个scan DFF链接在一起就成了scan chain,链上有多少个scan DFF表示这条链的长度。

作为结构性测试(structural test)的主要手段,DFT工程师需要注意的是电路的可测性,也就是可观测点和可控制点。在运用scan 测试方法的时候,整个芯片被看做是大量的寄存器和寄存器直接连接的组合逻辑。这也就是scan test开发的基本原理。

为了侦测生产过程中的制造缺陷,常用的方法并不是对芯片功能进行测试,而是从元器件最基本的电路反应入手,测试其中的异常,从而侦测到制造缺陷。当然上述是scan chain的基本思想,scan的具体过程在电路中的应用也是相对复杂的,因其横跨了芯片设计的整个周期,各个角落,在设计scan test的时候需要综合考虑到芯片设计的方方面面,包括时钟设计,电源设计,芯片结构,PAD资源,逻辑综合规划等。

DFT中的Scan Chain Flow

Scan的工作流程大概分为以下过程:

1、首先是scan insertion(扫描链的插入),在芯片功能设计完成后,即为将整个网表由一堆普通寄存器替换为扫描寄存器的过程,这样新加入的寄存器和原有寄存器一同构成scan chain并参与对芯片的测试;

2、接下来是Test Pattern Generation(测试向量生成过程),测试向量的产生是基于ATPG算法与故障模型以及电路结构生成的,依靠扫描链的插入结构生成测试向量,得到测试向量后;

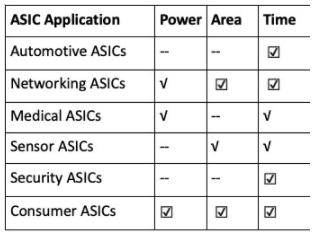

3、即对电路进行门级仿真,类似于验证芯片功能,当然最后测试向量需要在ATE机台上针对有限的芯片输入输出端口进行测试,尽管上述流程描述相对简单,但如前文所言在实际应用中要考虑对芯片主线的影响,功耗,面积开销等问题,这使得该过程变得相对复杂,所以在DFT的工作中,需要对各个因素全面考虑,做到覆盖率高,功耗低。

Scan Reorder

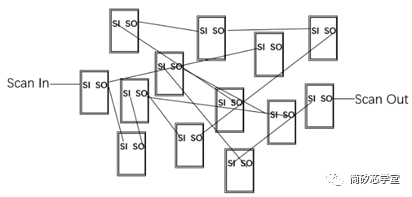

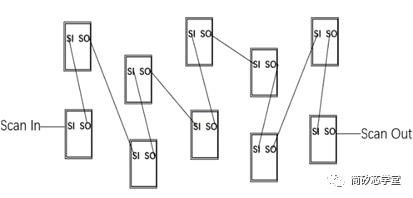

在做完Coarse Placement后,Scan Cell大部分是按照连接的顺序随机的乱放的。这样其实会极大地占用绕线资源,因此,在后续步骤开始之前,我们需要对扫描链的布局布线进行处理,在不影响逻辑功能的前提下,重新进行连接,从而减少走线长度。那这个重组的过程,我们就称之为扫描链重组(Scan Reorder),这个过程可以用下面两张图来形象地说明:

在scan插入后会生成后缀为.def文件,后端工程师通过获取.def文件对scan chain进行Reorder

Scan Reorder之前可以看到每个scan cell的连接是繁琐杂乱的,被称为detour,这就需要scan Reorder,在不影响功能逻辑的前提下整理布局布线,得到清晰合理的scan cell连接。

总结

大多数测试生成方案都会将一个被测电路视为一个黑盒子,而对测试机而言,唯一可利用控制端的就是主要输入端,唯一可用的观测点就是主要输出端,因此这就限制了电路的可控性和可观测性,扫描链的机制很好解决这一问题,随着该威廉希尔官方网站 的发展,测试生成算法,以及其他测试方案也会随着改进和发展。

-

电源设计

+关注

关注

31文章

1535浏览量

66393 -

寄存器

+关注

关注

31文章

5342浏览量

120277 -

触发器

+关注

关注

14文章

2000浏览量

61139 -

DFT算法

+关注

关注

0文章

27浏览量

7535 -

ATPG

+关注

关注

1文章

6浏览量

7559

发布评论请先 登录

相关推荐

DFT和BIST在SoC设计中的应用

让你彻底理解DFT

帮你理解DFT中的scan technology

DS26522 JTAG Scan Chain Mappin

DFT扫描设计在控制芯片的测试中的应用

一文读懂DC/AC SCAN测试威廉希尔官方网站

DFT分步法原理分析

用全扫描结构(FULL SCAN METHOD)来实现数字电路

怎么配置DFT中常见的MBIST以及SCAN CHAIN

是否需要补插scan chain的isolation cell?怎么插呢?

芯片设计测试中scan和bist的区别

DFT中的Scan Chain扫描链测试过程

DFT中的Scan Chain扫描链测试过程

评论