背景

AD9144是一款支持jesd204b协议高速DAC芯片。AD9144-FMC-EBZ是基于AD9144的评估板(Evaluation Board),它是主要由AD9144,AD9516,与PIC16F单片机组成的系统。工程上使用AD9144具有时钟时序要求很高和寄存器配置复杂的难点。

配置AD9144-FMC-EBZ,有两种途径:

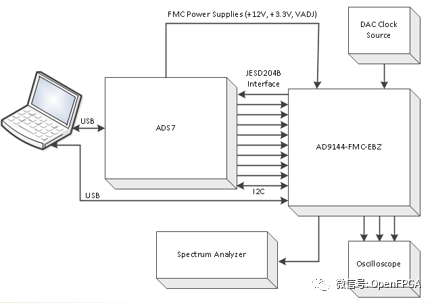

2、通过ADI提供的软件工具,配合母板(ADS7)来配置寄存器,如图所示:

遇到问题:

我们在尝试第一种方法的时候,遇到了SPI寄存器写不进的情况和读写不一致的情况。而第二种方法则需要ADS7用作母板。

调试

完成了以KC705作为母板,正确配置AD9144,并输出62.5MHz正弦波。

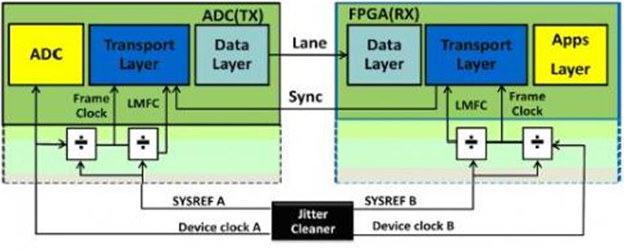

整个流程需要先在KC705上运行提供的HDL工程,随后进入软件工具配置流程。这里的HDL工程主要完成的是:Jesd204发送端的配置与正弦余弦信号的输出。另外,这里的软件工具配置流程既使用ADI官方提供的工具对AD9144和AD9516分别进行配置。

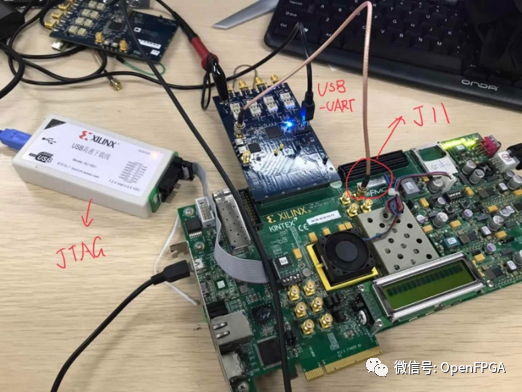

在调试开始前,硬件链接如下图所示:

1、AD9516寄存器配置获得

AD9516的作用是对输入时钟分频,为AD9144分别提供:sysref(3.91M),和refclk(125M)。

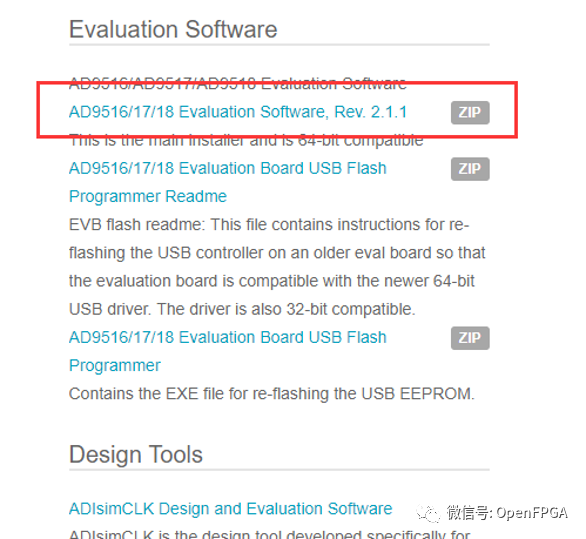

这里使用了AD9516-Evaluation-Software完成配置。

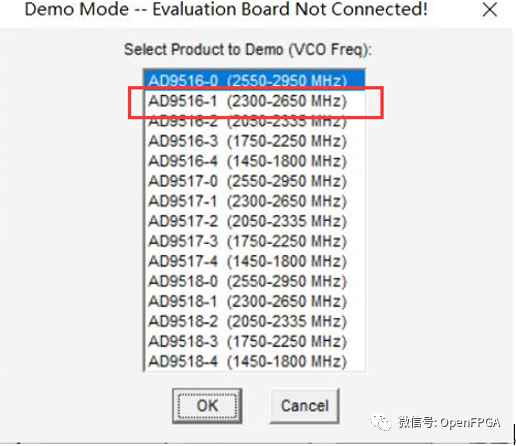

在安装结束后,打开软件并选择正确的型号,这里选AD9516-1

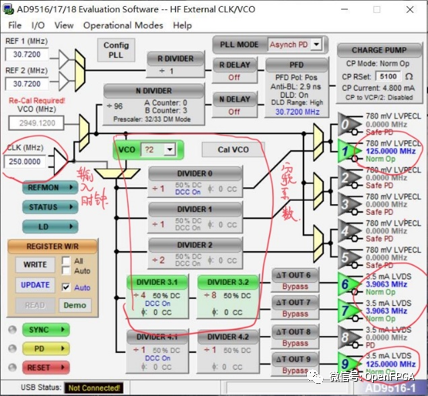

分别按下图所示进行配置:输入时钟(来自KC705)设置为2500;分频系数如图设置:最后得到两组频率为120M和3.9063M的时钟;点击左下角的橙色框(RGISTER W/R)中的WRITE。

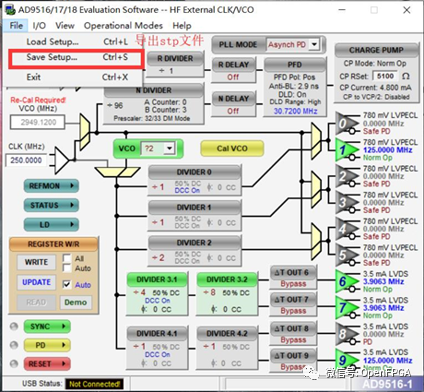

点击“file”,点击“Save Setup”,导出“stp”文件,如下图所示。

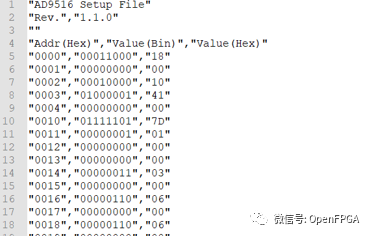

打开导出的.stp文件,如图:这个文件记录了寄存器地址与对应的值,将于后续步骤导入。

2、AD9144&AD9516寄存器配置:

A、首先到AD公司官网搜索DAC Software Suite和Analysis Control Evaluation软件,下载并安装;

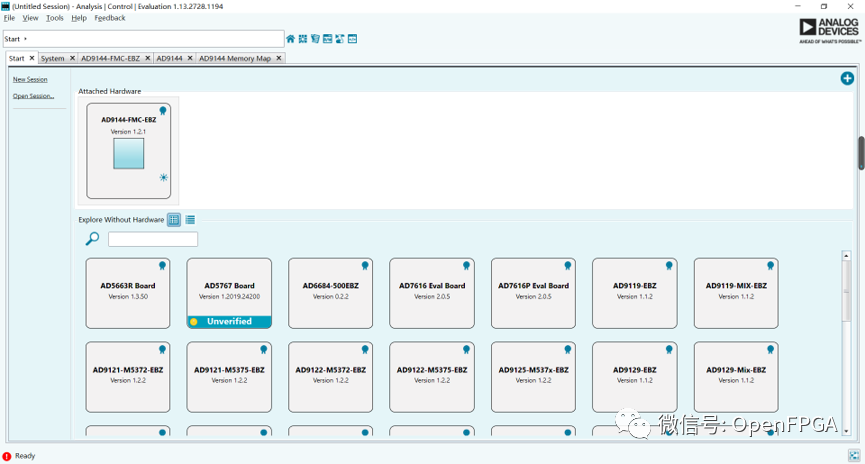

B、打开已经安装好的ACE软件,界面如下图所示。在硬件连接正确的情况下,图中红圈会检测到所连接的硬件板卡,点击图中绿圈的LED状按钮,AD9144-FMC-EBZ板卡上的蓝色LED灯会随之闪烁,说明连接成功。

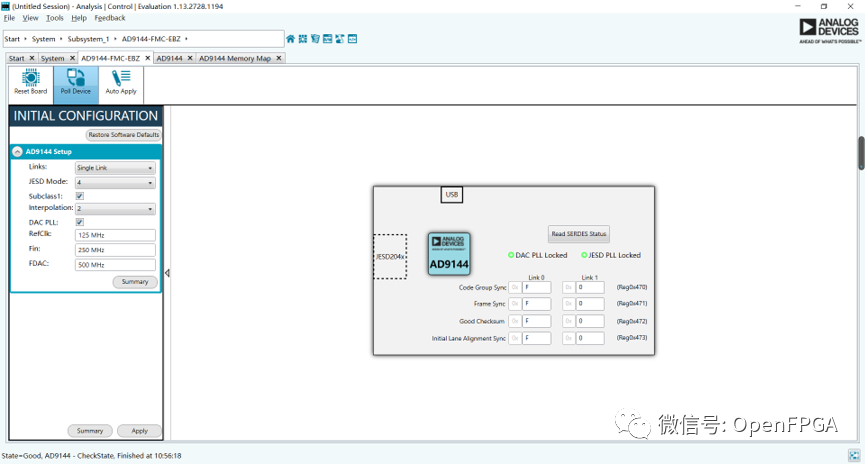

C、双击打开“AD9144-FMC-EBZ”板卡。在“initial configuration”界面中按如图所示进行设置,点击“summary”并“apply”,双击右侧红色图框中的AD9144芯片。

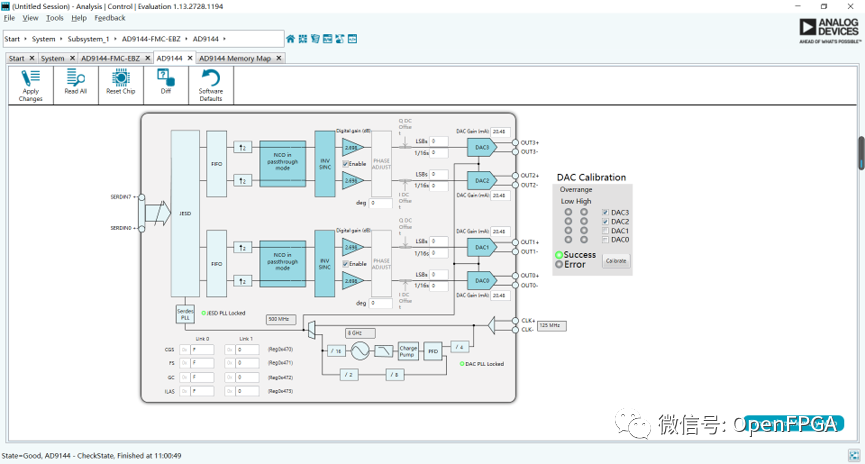

D、在打开的界面中按图中配置设置DAC calibration,选择“DAC3 DAC2”并点击“calibrate”。

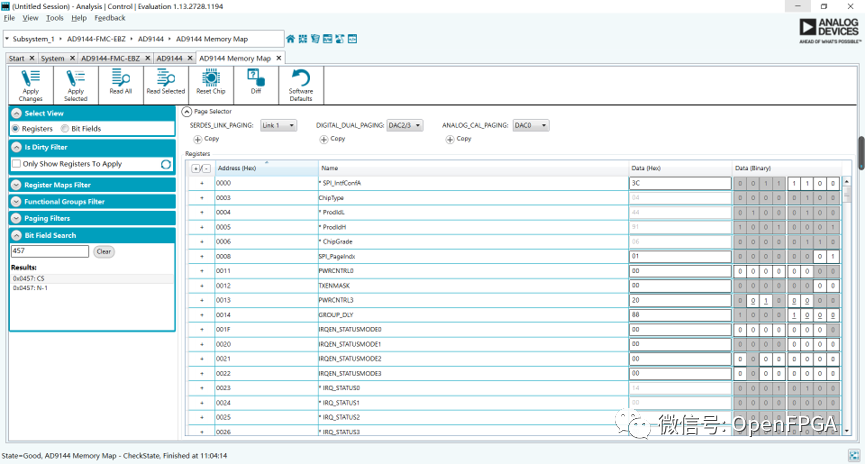

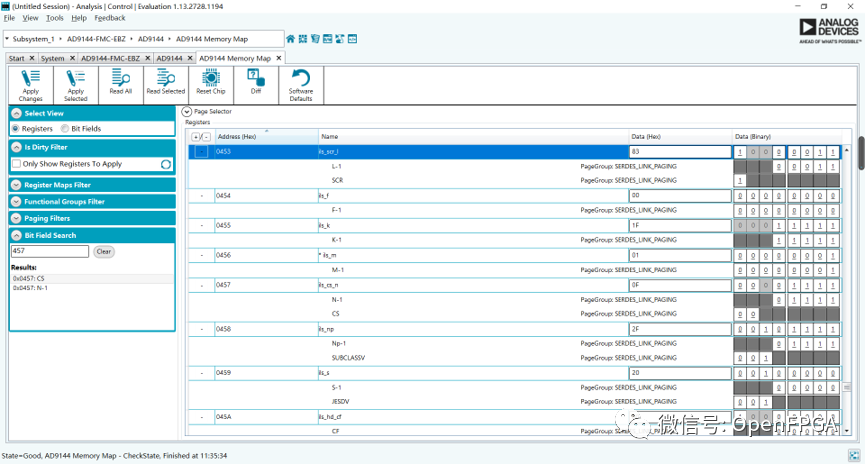

E、点击上图右下角的“Proceed to memory map”,按照项目所需配置好AD9144相关的寄存器表的值,点击右上apply selected将对应的寄存器值写入AD9144芯片。

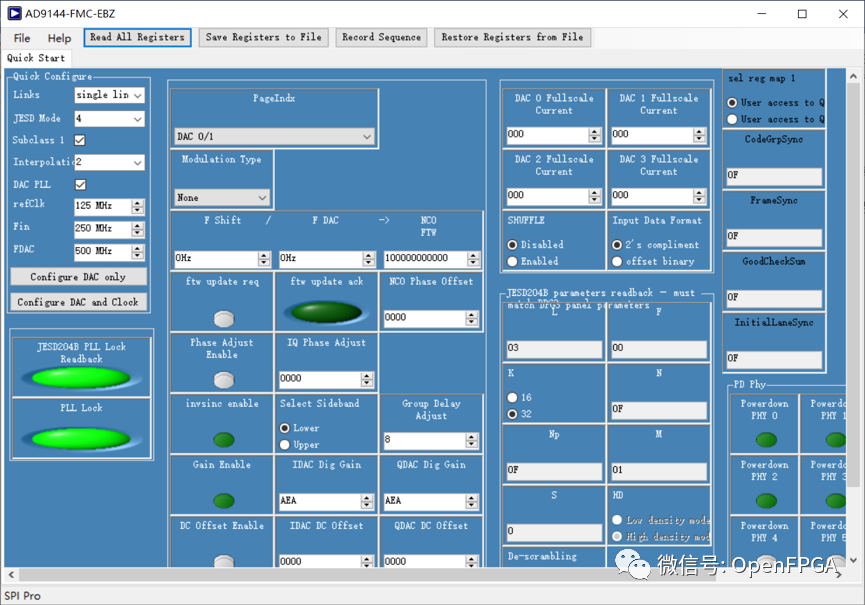

F、在电脑开始菜单>Analog Devices寻找“AD9144&AD9135&AD9136 SPI”并打开,软件界面如图所示:

G、在上方框中点击“read all registers”,然后点击“save registers to file”得到“.csv”文件,右键将其用记事本打开,如图所示,找到AD9516芯片开头的寄存器区域,将之前通过AD9516 Evaluation Software得到的stp文件中的寄存器值添加进.csv文件中并保存。

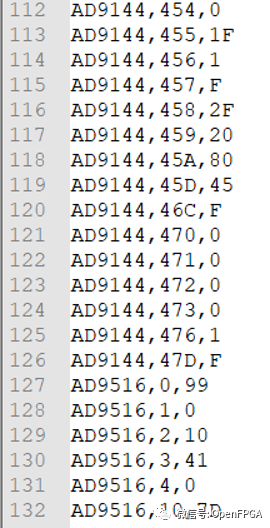

如图所示,第一列是AD9144/AD9516的芯片,第二列是对应芯片的寄存器地址,第三列是寄存器对应的值,将AD9516所有寄存器的值添加进来并保存。

H、打开“AD9144&AD9135&AD9136 SPI”软件并选择“restore registers from file”,将上一步中修改保存好的.csv文件导入。

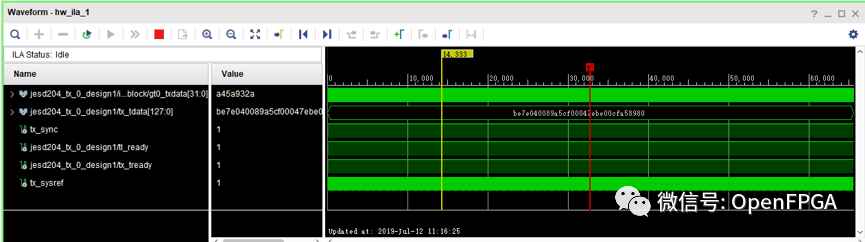

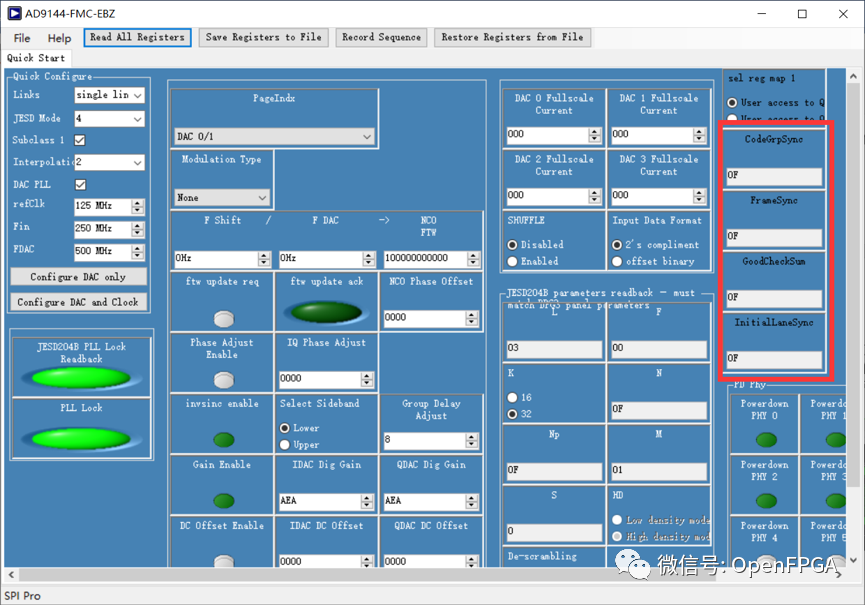

I、将vivado中的工程bit流文件烧录到板子上,通过ila抓取并观察tx_sync信号,发现信号持续拉高,返回AD9144&AD9135&AD9136 SPI软件read all registers,观察如图区域,如果图中所示四个寄存器值都为0F,vivado tx_sync持续拉高,并且txdata有数值输出,则说明AD9144与JESD204B同步成功,此时用示波器测量AD9144板卡输出可观测到波形输出。

调试过程中遭遇问题

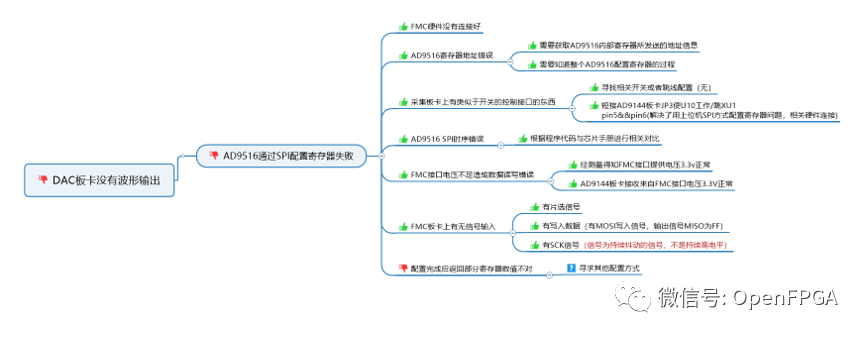

1.SPI配置失败问题?

2.AXI-Lite的参数设置?

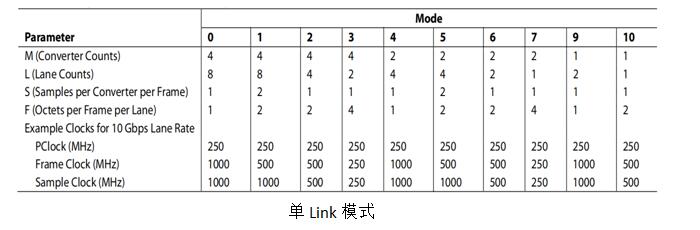

通过在Analysis Control Evaluation软件中读取AD9144寄存器表值,查询0x453-0x45A寄存器值,得到关键参数L,SCR,F,K,M,N,N’,S,CF,HD等的值。

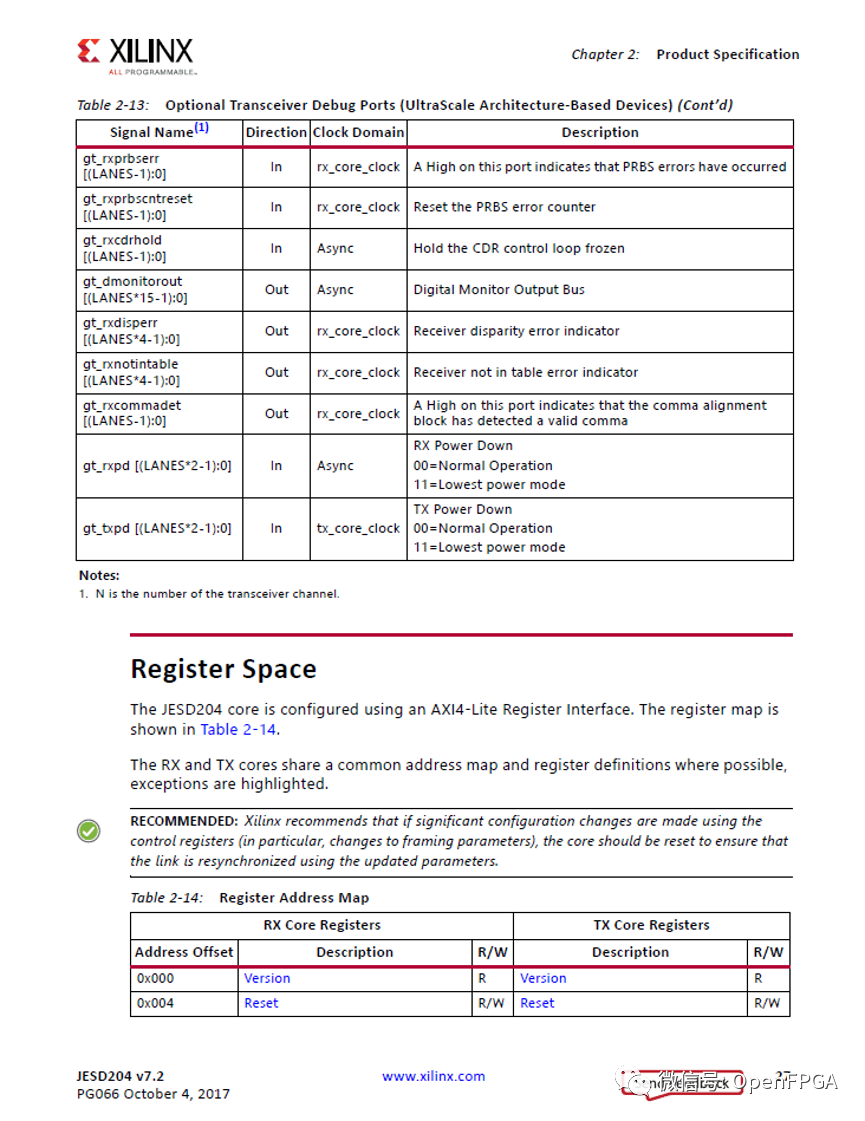

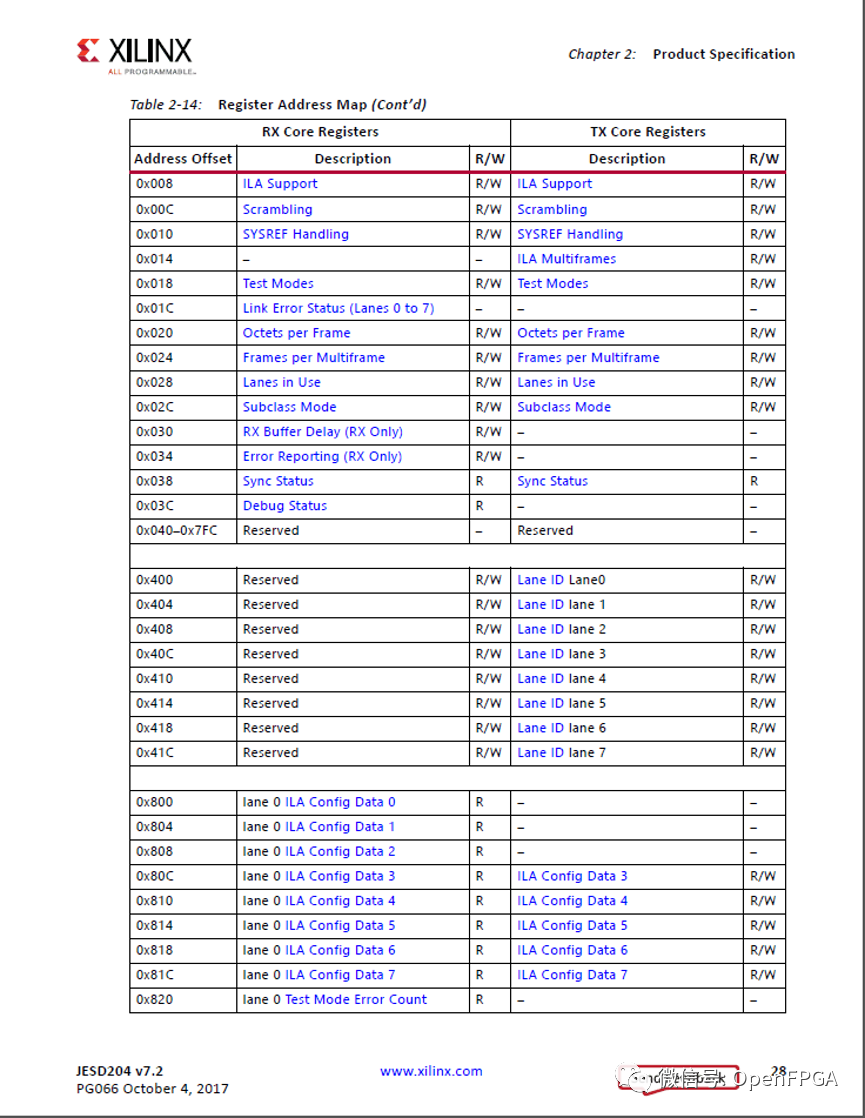

通过文档PG066 P27-P28中所示的值,计算出AXI协议所需要的每个寄存器地址的值。填入到vivado工程模块中的AXI协议部分。

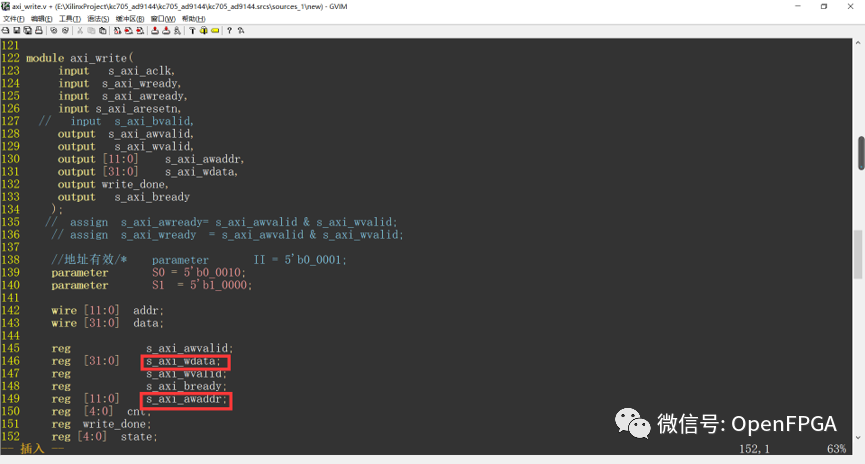

Vivado工程中的AXI协议部分:地址填入PG066 P27-P28中的寄存器地址,值填入更据关键参数算出来的值。

审核编辑:刘清

-

FPGA

+关注

关注

1629文章

21729浏览量

603029 -

芯片

+关注

关注

455文章

50731浏览量

423195 -

单片机

+关注

关注

6035文章

44553浏览量

634718 -

寄存器

+关注

关注

31文章

5336浏览量

120238 -

PIC单片机

+关注

关注

64文章

691浏览量

101924 -

dac

+关注

关注

43文章

2291浏览量

190983 -

DAC芯片

+关注

关注

1文章

32浏览量

14615 -

ad9144

+关注

关注

0文章

8浏览量

1907

原文标题:支持jesd204b协议高速DAC芯片AD9144-FMC-EBZ配置笔记

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

JESD204B的系统级优势

FPGA高速数据采集设计之JESD204B接口应用场景

FPGA高速数据采集设计之JESD204B接口应用场景

支持jesd204b协议高速DAC芯片AD9144-FMC-EBZ配置笔记

如何让JESD204B在FPGA上工作?FPGA对于JESD204B需要多少速度?

JESD204B协议有什么特点?

JESD204B协议介绍

JESD204B协议概述

基于NI PXI模块化测试平台对采用JESD204B协议进行测试

JESD204B时钟网络原理概述

使用JESD204B接口的AD9144高速DA转换模块参数设定(私人总结版)

JESD204B使用说明

支持jesd204b协议高速DAC芯片AD9144-FMC-EBZ

支持jesd204b协议高速DAC芯片AD9144-FMC-EBZ

评论