模块虽小但是要有新意,首先写一个同步FIFO,这是一个烂大街的入门级项目,但是我肯定不会写的那么简单,需求如下:

和大多数文章所写描述的同步FIFO的需求不一样的地方在于最后一个需求,内部例化的sram的读取动作不是读及读出的操作。因此基于这种sram,又要兼顾FIFO的标准协议,以及需要FIFO逻辑速度到达最优,需要对设计进行一些小的处理

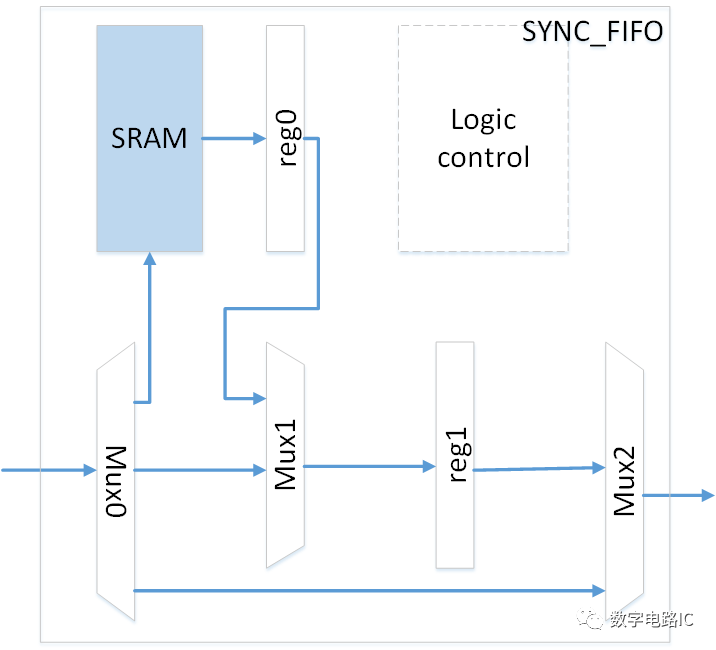

下图为本次同步FIFO设计的框图:

设计分析:

- 使用reg0的原因

由于sram延时一拍读出,因此就需要有reg0处理延时,既只要reg0为空,寄存器就向sram读数,达到提前取数,消除延时的效果。(一般sram有几拍延时就有几个reg0) - 使用reg1的原因

reg1用于处理边界条件,在sram和reg0为空时,没有读使能的情况下写入第一个数,此时第一个数如果存入sram,则读取流程将变成sram-reg0-output,中间延迟过长,但是假如使用reg1用于存储第一个数据,则可以把这一拍数据延时解决掉。(且同上述,一般有几个reg0就有几个reg1) - 使用mux2的原因

mux2也是用于处理边界条件,在sram和所有寄存器都为空时,写使能和读使能同时来到,则数据bypass通过SYNC_FIFO模块。 - mux0和mux1则用于处理上述逻辑关于数据通道切换的处理。

- 关于sram存取、各种空满信号的判断,就不再一一叙述,想了解这方面设计可以参见网上各种同步FIFO设计。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

寄存器

+关注

关注

31文章

5342浏览量

120278 -

sram

+关注

关注

6文章

767浏览量

114682 -

fifo

+关注

关注

3文章

388浏览量

43662 -

同步FIFO

+关注

关注

0文章

5浏览量

5347 -

FIFO设计

+关注

关注

0文章

7浏览量

4963

发布评论请先 登录

相关推荐

同步FIFO设计详解及代码分享

FIFO (先入先出, First In First Out )存储器,在 FPGA 和数字 IC 设计中非常常用。 根据接入的时钟信号,可以分为同步 FIFO 和异步 FIFO 。

发表于 06-27 10:24

•2092次阅读

可靠性设计分析系统

要求,需要按照可靠性工作要求开展各种各样的可靠性设计分析工作。其实,这些可靠性工作,目的解决产品可靠性工程问题,严格控制和降低产品质量风险。最近,看到有一个可靠性设计分析系统PosVim,功能还比较

发表于 12-08 10:47

异步FIFO的设计分析及详细代码

本文首先对异步 FIFO 设计的重点难点进行分析,最后给出详细代码。 一、FIFO简单讲解 FIFO的本质是RAM, 先进先出 重要参数:fifo

发表于 11-15 12:52

•8626次阅读

FIFO设计—同步FIFO

FIFO是异步数据传输时常用的存储器,多bit数据异步传输时,无论是从快时钟域到慢时钟域,还是从慢时钟域到快时钟域,都可以使用FIFO处理。

发表于 05-26 16:12

•1513次阅读

一个简单的RTL同步FIFO设计

FIFO 是FPGA设计中最有用的模块之一。FIFO 在模块之间提供简单的握手和同步机制,是设计人员将数据从一个模块传输到另一个模块的常用选择。

发表于 06-14 08:59

•452次阅读

基于寄存器的同步FIFO

FIFO 是FPGA设计中最有用的模块之一。FIFO 在模块之间提供简单的握手和同步机制,是设计人员将数据从一个模块传输到另一个模块的常用选择。 在这篇文章中,展示了一个简单的 RTL 同

为什么异步fifo中读地址同步在写时钟域时序分析不通过?

为什么异步fifo中读地址同步在写时钟域时序分析不通过? 异步FIFO中读地址同步在写时钟域时序分析

同步FIFO和异步FIFO的区别 同步FIFO和异步FIFO各在什么情况下应用

同步FIFO和异步FIFO的区别 同步FIFO和异步FIFO各在什么情况下应用? 1.

同步FIFO和异步FIFO区别介绍

1. FIFO简介 FIFO是一种先进先出数据缓存器,它与普通存储器的区别是没有外部读写地址线,使用起来非常简单,缺点是只能顺序读写,而不能随机读写。 2. 使用场景 数据缓冲:也就是数据写入过快

同步FIFO设计分析

同步FIFO设计分析

评论