FIFO在设计是一个非常常见并且非常重要的模块,很多公司有成熟的IP,所以一部分人并没有人真正研究写过FIFO,本文仅简述FIFO中部分值得保留的设计思路。

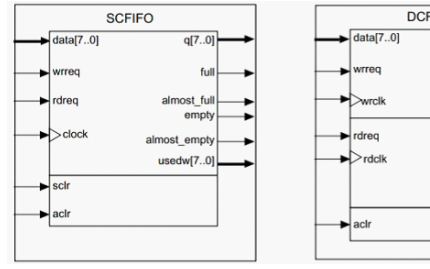

FIFO可以分为2大类:有直接使用寄存器搭的FIFO(多用于小型FIFO、和异步FIFO),也有使用SRAM搭的FIFO(多用于大型存储)。

因为SRAM比寄存器面积小。其他更细划分如单口,双口等等不做详细介绍。

本文将简述以下两个方向:

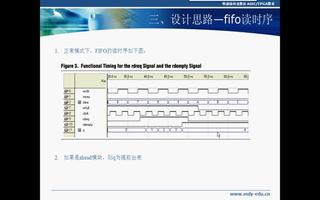

lSRAM出口通常不是当拍可以读出数据,因此需要逻辑对这部分做逻辑,实现和寄存器相同时序。

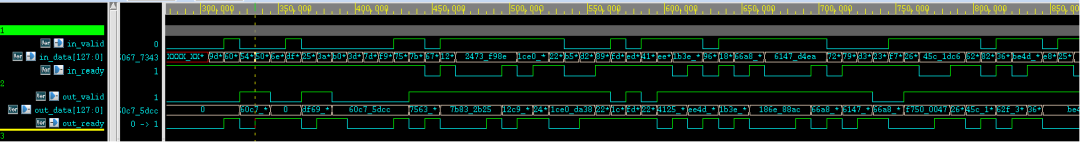

l由于第一条逻辑造成,当用户读取SRAM数据时会有几拍延迟,因此为消除延迟将会增加数据输出开关功能(见本公众号文章模块端口握手设计模块多对多端口握手设计-总结)以及数据输入切换功能。

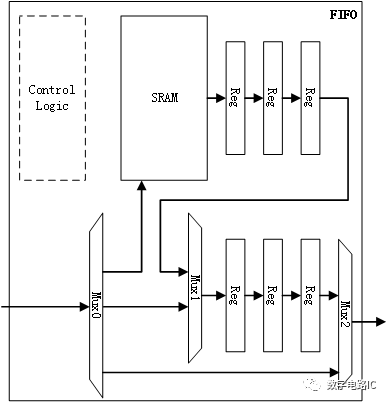

本文设计FIFO如下图所示:

第一条中SRAM出口无法做到当怕出数的原因是由SRAM的知道工艺造成(可以在存储器芯片手册里看到),例如在TSMC 5nm工艺下,读使能有效到数据稳定输出大概需要500ps,而且如果位宽过大,在ECC时又需要几百ps延迟,因此可能一拍数据无法收敛,因此需要几级寄存器缓存,一般是3拍(控制信号缓存+读数据延迟+ECC延迟)。

第二条中输出开关功能,参见本文相应文章,功能主要保证当FIFO有数据时会传递至最后一级输出寄存器中。

第二条中的输入切换功能,是指2个mux模块,功能主要保证输出reg优先被填满,当输出reg被填满之后,新数据才会被存入SRAM中。输出寄存器数量和SRAM延时寄存器数量相同,保证当输出寄存器中数据在3拍读出之后SRAM数据经过延时之后恰好可以继续被读出,而不会中间出现间隔。

对于mux2的功能是在FIFO数据为空,且同时又读写使能,可以直接把输入数据输出。

上述内容仅用于同步FIFO设计,而异步大型FIFO经常采用同步SRAM缓存+异步寄存器FIFO的设计模式,有时间待续异步FIFO设计。

-

寄存器

+关注

关注

31文章

5336浏览量

120260 -

sram

+关注

关注

6文章

767浏览量

114677 -

fifo

+关注

关注

3文章

387浏览量

43655 -

FIFO设计

+关注

关注

0文章

7浏览量

4963

发布评论请先 登录

相关推荐

FIFO队列原理简述

求助verilog编写实现AXIStream-FIFO功能思路

高速异步FIFO的设计与实现

一种异步FIFO的设计方法

什么是fifo fifo什么意思 GPIF和FIFO的区别

如何配置自己需要的FIFO?FIFO配置全攻略

FPGA之FIFO练习1:设计思路

FPGA之FIFO练习3:设计思路

FPGA之FIFO练习2:设计思路

FIFO设计—同步FIFO

浅谈FIFO设计思路

浅谈FIFO设计思路

评论