1, 原理图模块自动连线

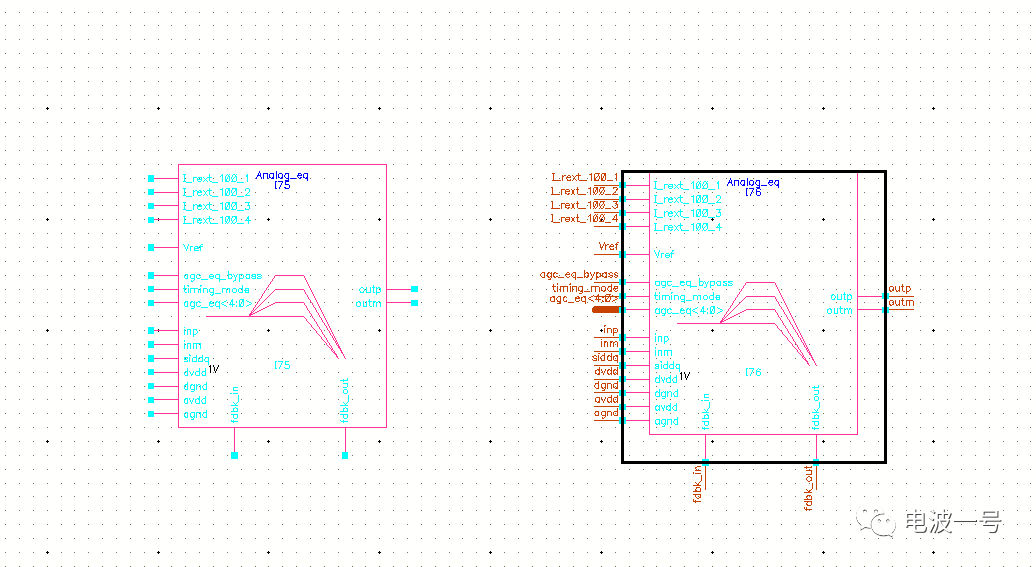

对一个比较具有较多端口的instance, 特别是带寄存器控制接口的模块,如果把所有的端口连线接好是一件非常繁琐的事情。这里有一个小技巧,就是选择器件,器件高亮之后按Space 空格键,所有的端口就自动生成label了。如果对个别端口有特殊的前缀后缀之类的,也可以在Add Instance 属性菜单(I --> F3)中勾选 register terminals only, 添加完之后再按空格。

2, 临时删除器件

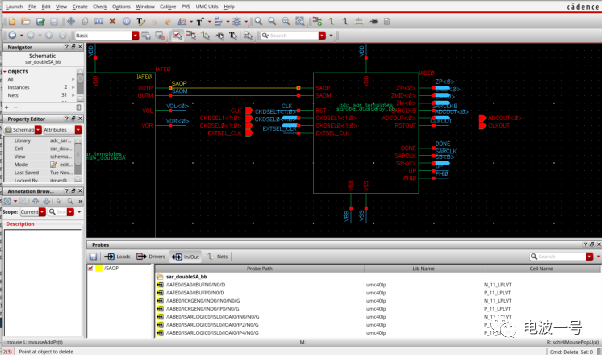

在调试电路仿真的时候,经常需要临时删除个别器件,如果直接删除又得重新从库中引用繁琐。新版本的CDS,选中器件shift+del 就可以出现一个X标识在器件上。这样netlisting的时候,被X的器件就不会出现在网表中了。如果要取消再按一次shift+del即可。

3, 器件网线高亮和动态显示

在审阅电路的时候经常用到一个技能就是用数字9,把选中的net 变成彩色的,但是当用于非常大规模的原理图分析的时候可视效果就不怎么理想了。那么开启net-highlight 功能,是不是有点爽?

4,器件的快速串联和并联, 这应该是常用技巧了吧,通过将Instance Name写成总线形式再通过net 命名可以快速实现串联和并列。值得注意的是修改属性的时候要选中Apply to -->all selected.

5, 多个library引用变成单个library

在多人项目中,如果缺乏项目管理工具,库之间的引用对项目管理者来说经常是个头疼的问题,在备份和拷贝的过程中经常容易缺失某个引用库。用library release的方法可以有效的解决这个问题。右键选中top 文件,copy--> 点上 copy Hierarchical (skip pdk analoglib这些基础库)到一个新的lib中,点上update instance of Entry library, 这样新的library里就有所有reference的cell了,把这个library提交给项目管理者,他就再也不会找你麻烦了。

还有哪些小技巧呢?

-

寄存器

+关注

关注

31文章

5342浏览量

120277 -

仿真

+关注

关注

50文章

4079浏览量

133570 -

Library

+关注

关注

0文章

13浏览量

10072 -

Virtuoso

+关注

关注

4文章

17浏览量

25073

发布评论请先 登录

相关推荐

高效率通信电源威廉希尔官方网站

高效率开关电源设计与制作

高效率汽车同步降压参考设计包括BOM及原理图

高效率高线性的功放怎么实现?

高效率电源的设计

高效率开关电源的设计及应用

何为高效率电机

Virtuoso高效率使用技巧(2)

提高效率的DC电源模块设计技巧

Virtuoso高效率使用技巧(1)

Virtuoso高效率使用技巧(1)

评论