关于硅材料杂质浓度测试,经研究,参考肖特基二极管杂质浓度测试方案,两者几乎一致,因此,针对硅材料杂质浓度测试亦采用CV法测量,方案如下:

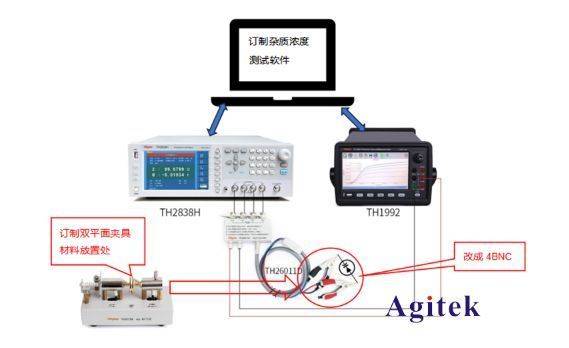

一、 方案配置

1、 TH2838系列LCR数字电桥(必选)

可选频率20Hz-1MHz/2MHz,用于测试CV特性

2、 TH199X系列精密源/测量单元(SMU)(必选)

可选单/双通道,电压±63V/210V,6 1/2输出/测量分辨率,最小输出电压分辨率100nV、电流10fA

3、 TH26011D直流隔离开尔文测试夹具(必选)

用于隔离直流电压与LCR测试,如果测试片状材料,需要改装成4个BNC,以保证精度,直接用夹子测试材料电容误差较大。

4、 TH26008A或TH26007型SMD测试夹具(可选)

若用于测试片状材料,需用此夹具接触材料,可选针状测试端或订制圆形测试端。

5、 订制上位机软件(可选)

此软件主要用于采集CV数据,采集不同电压下电容值,并根据下列参考资料部分公式直接计算出对应杂质浓度。

若不定制此上位机软件,可自行采集数据并计算浓度。

方案结构示意图

一、 参考资料:肖特基二极管杂质浓度相关知识

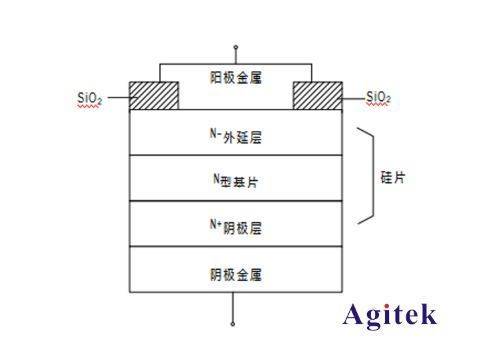

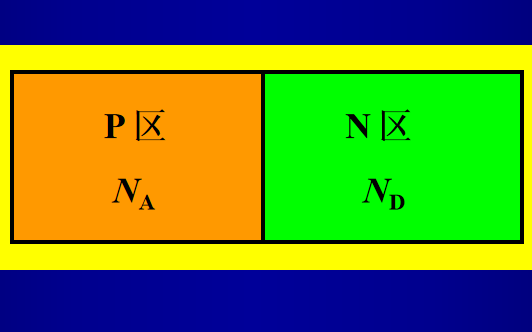

1、 肖特基二极管的构造

肖特基二极管是贵金属(金、银、铝、铂等)作为正极,以N型半导体为负极,利用两者接触面上形成的势垒具有整流特性而制成的金属-半导体器件。

构造:以重掺杂的N+为衬底,厚度为几十微米,外延生长零点几微米厚的N 型本征半导体作为工作层,在其上面再形成零点几微米的二氧化硅绝缘层,光刻并腐蚀直径为零点几或几十微米的小洞,再用金属点接触压接一根金属丝或在面接触中淀积一层金属和N型半导体形成金属半导体结,在该点上镀金形成正极,给另一面N+层镀金形成负极,即可完成管芯,如图4.1所示。

图4.1 肖特基二极管结构图

1、 肖特基势垒的形成原理

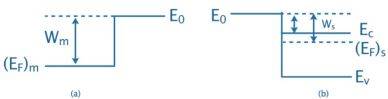

(1) 功函数与电子亲和能金属的功函数Wm

金属的功函数表示一个起始能量等于费米能级的电子,由金属内部逸出到表面外的真空中所需的最小能量,功函数的大小标志电子在金属中被束缚的强弱。

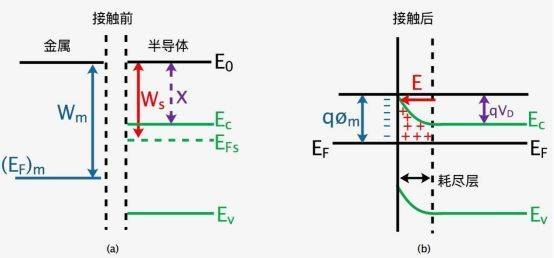

如图4.2(a)所示。

为真空中电子的能量,又称为真空能级。

图4.2 (a)金属功函数; (b)半导体功函数半导体的功函数Ws

半导体功函数半导体的功函数Ws

E0与费米能级之差称为半导体的功函数,如图4.2(b)所示。

和金属不同,半导体的费米能级

随掺杂类型和掺杂浓度而变化,所以Ws也与杂质类型和杂质浓度有关。

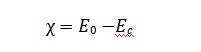

定义真空能级E0和导带底能量Ec的能量差为电子亲合能,用χ表示,即

电子亲合能表示使半导体导带底的电子逸出体外所需的最小能量。

(2) 肖特基势垒结的形成

功函数不同的两种晶体形成接触时,由于费米能级EF不在同一水平上,将有电子自 EF 较高一侧的表面流向对方表面,在两侧晶体的表面形成电荷层,从而在两者之间形成电势差,直到费米能级达到同一水平时,将不再有电子流流动。这时在两者之间形成的电势差称为接触电势差。接触电势差正好补偿两者费米能级之差。

假定有一块金属和一块n型半导体,并假定金属的功函数大于半导体的功函数,即:Wm>Ws。由于它们有相同的真空能级,所以在接触前,半导体的费米能级EFs高于金属的费米能级EFm,且EFs-EFm=Wm-Ws,如图4.3(a)所示。

图4.3 (a)金半接触前能级; (b)金半接触后能级变化。

当金属和N型半导体接触时,由于半导体的费米能级高于金属中的费米能级,

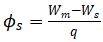

电子流从半导体一侧向金属一侧扩散,同时也存在金属中的少数能量大的电子跳到半导体中的热电子发射;显然,扩散运动占据明显优势,于是界面上的金属形成电子堆积,在半导体中出现带正电的耗尽层,如图 4.3(b)所示。界面上形成由半导体指向金属的内建电场,它是阻止电子向金属一侧扩散的,而对热电子发射则没有影响。随着扩散过程的继续,内建电场增强,扩散运动削弱。在某一耗尽层厚度下,扩散和热电子发射处于平衡状态。宏观上耗尽层稳定,两边的电子数也稳定。界面上就形成一个对半导体一侧电子的稳定高度势垒:

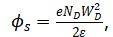

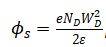

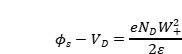

它和耗尽层厚度有如下关系:

其中

为N的掺杂浓度,在势垒区,������为耗尽层宽度。电子浓度比体内小的多,是一个高阻区域,称为阻挡层,界面处的势垒通常称为肖特基势垒。耗尽层和电子堆积区域称为金属-半导体结。

2、 肖特基二极管的整流特性

如果给金属-半导体结加上偏压,则根据偏压方向不同,其导电特性也不同。

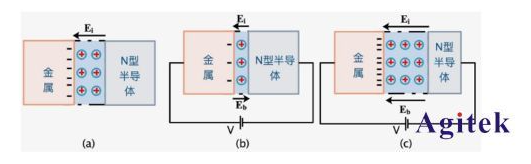

零偏压:保持前述势垒状态,如图4.4(a)所示。

正偏:金属一侧接正极,半导体一侧接负极,如图4.4(b)所示。

外加电场与内建电场方向相反,内建电场被削弱,耗尽层变薄,肖特基势垒高度降低,使扩散运动增强,半导体一侧的电子大量的源源不断的流向金属一侧造成与偏压方向一致的电流,金属-半导体结呈正向导电特性,且外加电压越大,导电性越好,其关系为:

反偏:金属一侧接负极,半导体一侧接正极,如图4.4(c)所示。

外加电场与内建电场方向一致,耗尽层变厚,扩散趋势削弱,热电子发射占优势,但这部分电子数量较少,不会使发射电流增大。在反偏电压的规定范围内,只有很小的反向电流。在反偏情况下,肖特基势垒呈大电阻特性。反偏电压过大时,则导致反向击穿。

图4.4 肖特基二极管在不同偏压下的情况

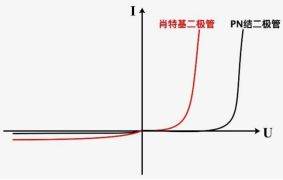

肖特基二极管与 PN 结二极管具有类似的整流特性,硅肖特基二极管的反向饱和电流比典型的PN结二极管的反向饱和电流大103~108倍,如图4.5所示,具体的数值取决于肖特基势垒高度。较小的肖特基势垒高度导致反向饱和电流较大,较大的反向饱和电流意味着产生相同的正向电流,肖特基二极管的正向导通电压较小,这个特性使得肖特基二极管更适合应用于低压以及大电流领域。

图4.5 肖特基二极管伏安特性曲线

1、 势垒电容

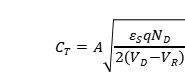

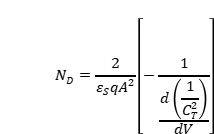

耗尽层的厚度随外加电压的变化直接反映着耗尽层具有一定的电容。耗尽层的两个界面可以看作平行板电容器的两个面板,假如半导体内杂质浓度是均匀的且不存在氧化层,则在耗尽层的区域内,其电容为:

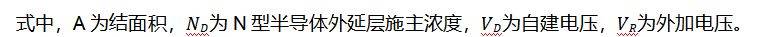

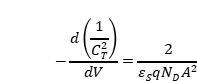

如果半导体均匀掺杂,则 为一条直线,通过直线的斜率可求得半导体的掺杂浓度为:

审核编辑:汤梓红

-

二极管

+关注

关注

147文章

9602浏览量

166140 -

测试

+关注

关注

8文章

5223浏览量

126563 -

肖特基二极管

+关注

关注

5文章

919浏览量

34800 -

硅材料

+关注

关注

0文章

44浏览量

8018

发布评论请先 登录

相关推荐

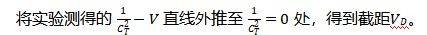

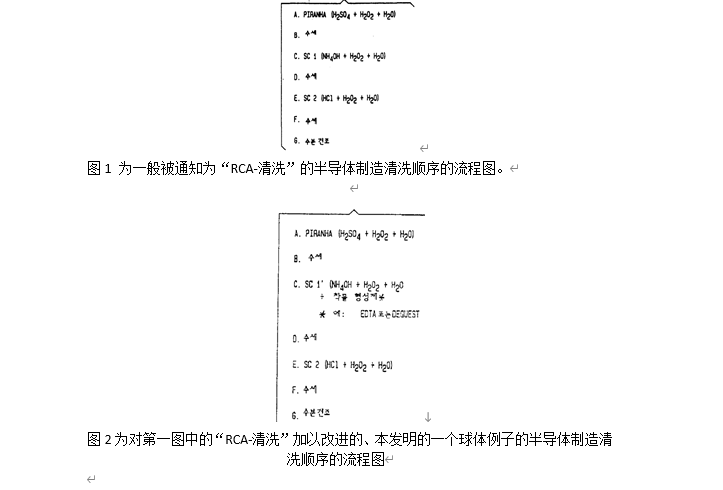

如何减少硅晶片表面上的金属杂质

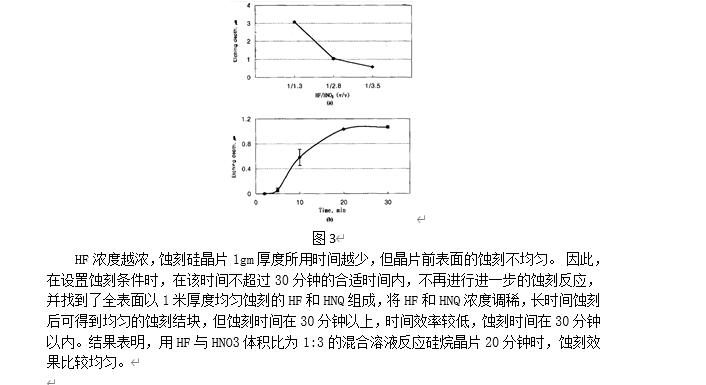

不同浓度和温度的硫酸对材料的腐蚀差别较大

氧气 浓度 方案开发

模拟电子复习总结(一):半导体二极管

数字源表应用方案的半导体霍尔效应测试

如何采用89C52和MQ-3酒精浓度传感器设计酒精浓度测试仪?

吉时利源表在宽禁带材料测试的应用方案

为什么硅仍然主导着集成电路产业?

微电子器件教程之PN结的详细资料说明

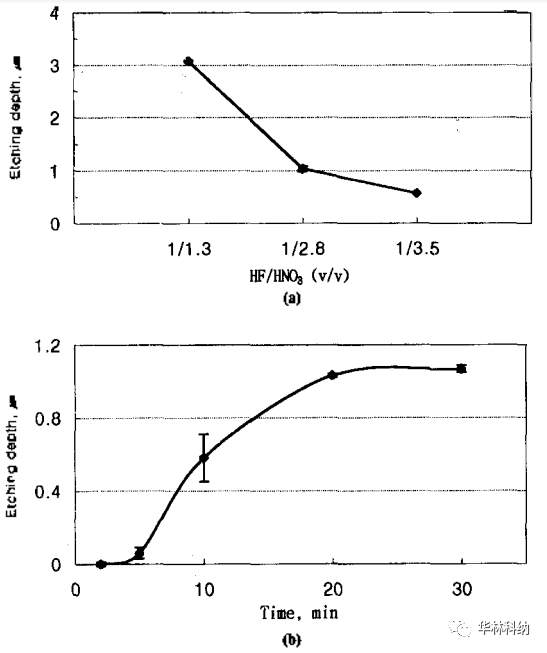

用蚀刻法测定硅晶片表面的金属杂质

利用蚀刻法消除硅晶片表面金属杂质

硅材料杂质浓度测试方案

硅材料杂质浓度测试方案

评论