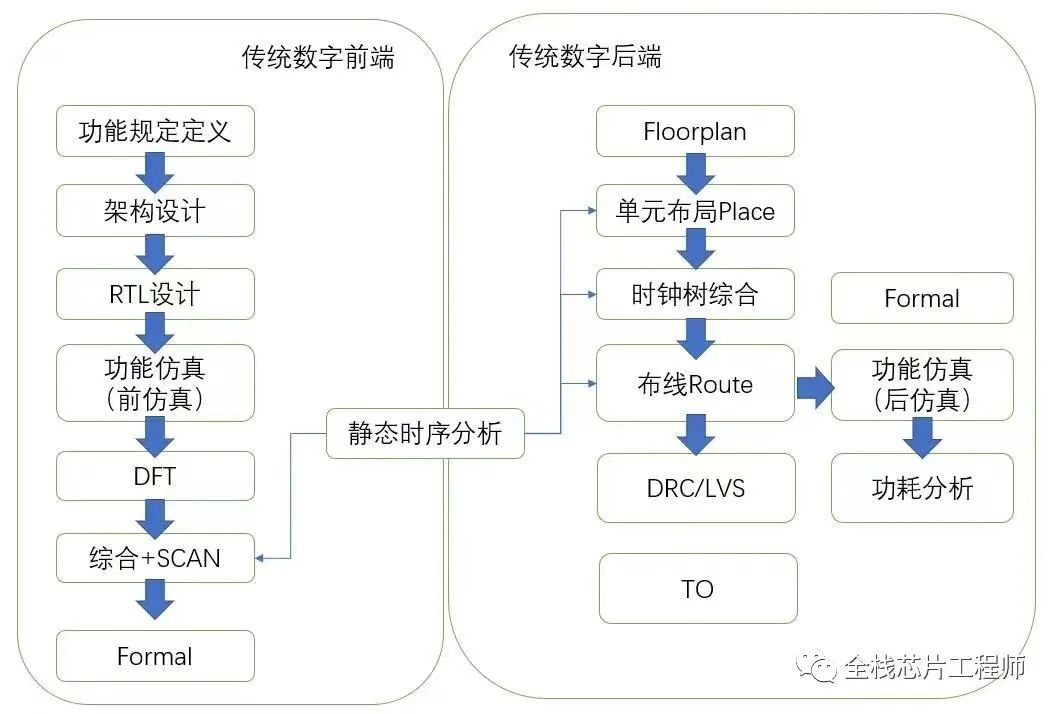

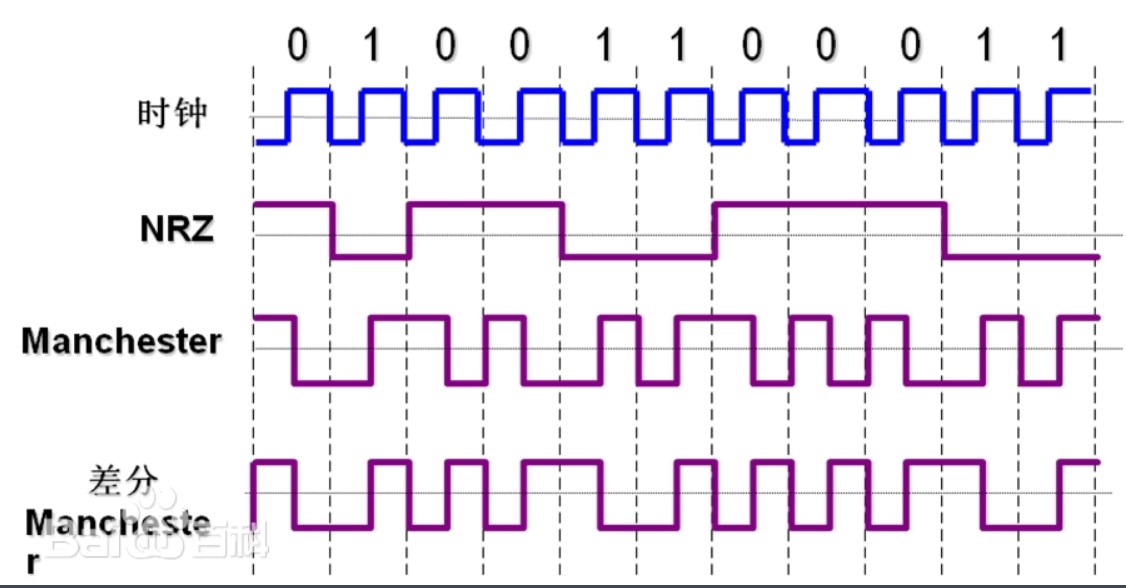

我们知道,Verdi横空出世,大大加速了数字设计验证的debug的效率,verdi波形格式是fsdb,压缩率高,逐步取代了VCD波形,但是有些芯片设计环节仍然需要VCD。比如功耗分析需要fsdb转换成VCD,比如interwetten与威廉的赔率体系 仿真需要数字的VCD激励波形。

VCD是不压缩的文本格式,兼容性好,缺点是文件太大。后仿先写出高压缩比的FSDB文件,再转成VCD。可指定转换起止时间、结束时间。接下来介绍怎么转。

1. 转换全部信号

%fsdb2vcd verilog.fsdb -o output.vcd

2.转换指定模块内的信号(命令需要指定-s),并指定转换时间,时间默认是ns,也可以带单位s|ms|us|ns|ps|fs。-level 1是/system/i_cpu不包括子模块的所有信号,如果想得到/system/i_cpu及其子模块的所有信号,则需要-level 0

%fsdb2vcd verilog.fsdb -s /system/i_cpu -level 1 -bt 10 -et 100

3. 生成fsdb的summary,如下命令并没转换。

%fsdb2vcd verilog.fsdb -summary

除了Redhwak、Voltus看功耗外,使用PTPX工具也可以进行代码级功耗评估。PTPX工具需要使用SAIF对翻转率进行标定,以得到相对准确功耗。SAIF文件从仿真波形中提取时较为稳妥,并且具有接近实际工作场景的翻转率。fsdb2saif提取波形文件中信号翻转率

1.转换FSDB为SAIF

%fsdb2saif verilog.fsdb -o verilog.fsdb.saif

2. 指定时间转换FSDB为SAIF

%fsdb2saif verilog.fsdb -bt 10ps -et 1000ps -o verilog.fsdb.saif

3. 指定转换范围

%fsdb2saif rtl.fsdb -s "/system/i_cpu" -o rtl.fsdb.saif

通常,$fsdbDumpvars(0, top)可以dump全部波形。

审核编辑:刘清

-

转换器

+关注

关注

27文章

8700浏览量

147122 -

芯片设计

+关注

关注

15文章

1017浏览量

54885 -

VCD

+关注

关注

0文章

37浏览量

34721 -

仿真器

+关注

关注

14文章

1018浏览量

83730 -

Verilog语言

+关注

关注

0文章

113浏览量

8225

原文标题:【景芯SoC培训】后仿波形处理

文章出处:【微信号:全栈芯片工程师,微信公众号:全栈芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

请高手帮忙设计Labview 的声音采集及处理 有模板可以来仿

我后仿出现了10种警告。。。求助

labview2012与simulink通过SIT联仿后信号处理部分的问题

怎样用calibreview格式提取参数做后仿?有哪几种方法

saber仿真软件波形如何处理分析、saber仿真软件如何画电路图

浅析后仿波形处理

浅析后仿波形处理

评论