RS触发器的逻辑功能是什么

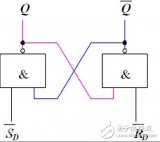

RS触发器是一种常见的数字逻辑门电路元件,它由两个相互反馈的逻辑门组成。RS触发器的逻辑功能可以描述为存储器元件或双稳态开关。

RS触发器有两个输入端(R和S)和两个输出端(Q和Q‘)。这里的R和S代表“Reset”(复位)和“Set”(置位),它们控制输出状态。

以下是RS触发器的逻辑功能:

1. 当R=S=0时,触发器保持状态,不发生变化。输出Q保持上一个存储的值。这种状态称为“保持”或“无效”状态。

2. 当R=0、S=1时,触发器的输出Q被置为逻辑“0”(低电平)。这称为“复位”状态。

3. 当R=1、S=0时,触发器的输出Q被置为逻辑“1”(高电平)。这称为“置位”状态。

4. 当R=S=1时,触发器将进入禁止状态。在禁止状态下,输入的改变不产生输出变化,即状态保持不变。这种状态是被禁止的,因为在理想情况下,R和S不应同时为1。

RS触发器可以实现存储、复位和置位功能,具有双稳态特性。它可以用于数字电路中的时序逻辑和存储器设计。需要注意的是,由于输入的不确定性和禁止状态的问题,使用RS触发器可能引起不稳定的结果,因此通常在实际应用中会使用更可靠的触发器类型,如D触发器或JK触发器。

基本RS触发器的四种状态

基本RS触发器具有四种可能的状态,这取决于其两个输入端(R和S)的逻辑电平,以及初始状态。以下是基本RS触发器的四种状态:

1. 保持状态(Hold State):当R=0且S=0时,触发器保持其当前状态。这种状态下,输出保持不变,无论之前的输入状态是什么,触发器的状态保持不变。

2. 复位状态(Reset State):当R=0且S=1时,触发器进入复位状态。在此状态下,输出Q被强制为逻辑低电平(0),而输出Q’被强制为逻辑高电平(1)。

3. 置位状态(Set State):当R=1且S=0时,触发器进入置位状态。在此状态下,输出Q被强制为逻辑高电平(1),而输出Q‘被强制为逻辑低电平(0)。

4. 禁止状态(Forbidden State):当R=1且S=1时,触发器处于禁止状态。在此状态下,输入的变化不会导致输出的变化。这种状态应该尽量避免,因为它会导致不可预测的结果。

需要注意的是,禁止状态是不稳定的,并且R和S输入的变化可能导致从禁止状态到复位状态或置位状态的不受控制的切换。因此,为了保证稳定和可控的行为,通常会使用带有附加逻辑电路的改进型触发器,如带有时钟输入的D触发器或JK触发器。

rs触发器的约束条件是什么

RS触发器在设计和使用时存在一些约束条件,以确保其正确的功能和避免潜在的问题。以下是RS触发器的一些常见约束条件:

1. 非禁止状态:输入R和S不应同时为逻辑高电平(1),即R和S不能同时为1。这是为了避免触发器进入禁止状态,因为禁止状态下触发器的行为是不可预测的。

2. 触发器建立和保持时间:对于RS触发器的输入信号,应满足触发器的建立时间(Setup Time)和保持时间(Hold Time)要求。即在输入信号的变化之前和之后,输入信号需要保持在足够的时间窗口内,以使触发器能够稳定地识别和响应输入。

3. 输入噪声和抖动:输入信号的噪声和抖动也是需要考虑的因素。由于RS触发器是基于电平变化的触发器,输入端的不稳定性可能导致输出的不稳定性和误触发。

4. 重置和置位的优先级:在特定情况下,当R和S同时变为1时,触发器会由于竞态条件而产生问题。为了避免竞态条件,可以设定重置和置位的优先级,即确定在同时满足R和S条件时,应该重置还是置位。

5. 时序和时钟边沿:在一些应用中,RS触发器需要与时钟信号一起使用,这涉及到时序和时钟边沿的配合和同步。必须确保输入信号的变化和触发器的状态变化在正确的时钟边沿上同步。

这些约束条件可以确保RS触发器在工作中的可靠性和稳定性。在实际使用中,设计者必须满足这些约束条件,并且根据具体应用场景进行测试和验证,以确保触发器的正确操作。

编辑:黄飞

-

存储器

+关注

关注

38文章

7484浏览量

163769 -

RS触发器

+关注

关注

3文章

101浏览量

17934 -

触发器

+关注

关注

14文章

2000浏览量

61134 -

逻辑功能

+关注

关注

0文章

14浏览量

3102

发布评论请先 登录

相关推荐

基本rs触发器的约束条件

RS触发器工作原理_RS触发器逻辑功能_RS触发器和SR触发器的区别

RS触发器的逻辑功能是什么 rs触发器的约束条件是什么

RS触发器的逻辑功能是什么 rs触发器的约束条件是什么

评论