1、在做 PCB 设计时,为了满足某一组所有信号线的总长度满足在一个公差范围内,通常要使用蛇形走线将总长度较短的信号线绕到与组内最长的信号线长度公差范围内,这个用蛇形走线绕长信号线的处理过程,就是我们俗称的 PCB 信号等长处理。等长的目标是为了满足同组信号的时序匹配要求。

2、等长范围应严格遵守不同接口或者信号的要求,具体的可参考模块规范内容。如若有疑问,及时与客户进行确认。

3、处理等长之前应先把同组内线长最长的信号线找到,第一步优化最长信号的长度。

4、等长处理完后应对整根信号线路径进行检查,检查其是否避开干扰源,检查其是否合格。

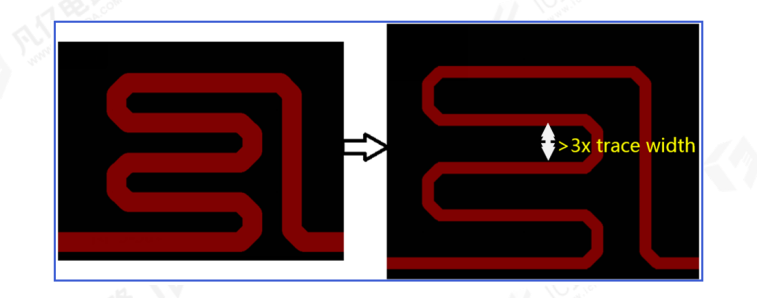

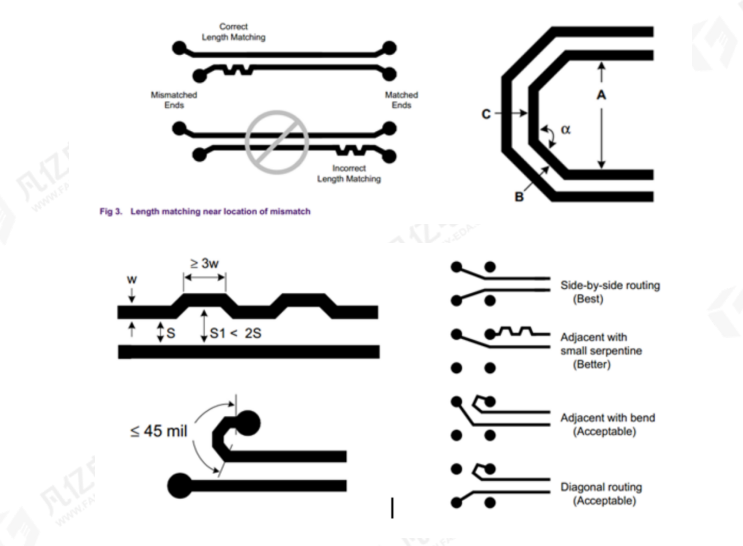

5、等长处理时,间距优选4W,如空间受限,可调整到3W;等长高度控制在40-150mil为宜,不能过高;转角长度不小于线宽的1.5倍,一般控制在6-10mil大小,如线宽4mil,转角大小控制在6mil,转角不能太小,如图1所示。

图1 蛇形走线的要求

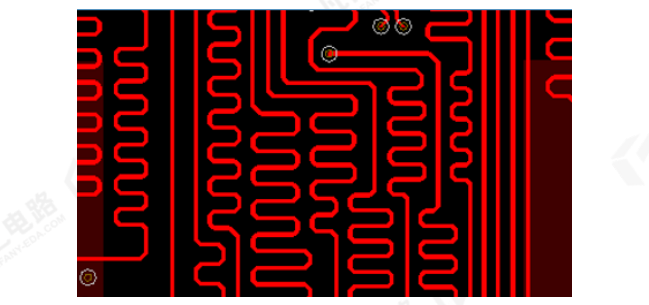

6、等长应尽量处理在水平或竖直方向上,避免处理在斜线上;处理不能太过散乱,应尽量集中处理,保证其美观性,原则上是处理完一根信号后,第二根先修线挨到其旁边,再对第二根进行等长处理,以保证空间的利用率及整体设计美观性。同一设计内,等长的高度应控制差不多相同,不要相差太多,如图2。

图2 PCB的蛇形咬合等长

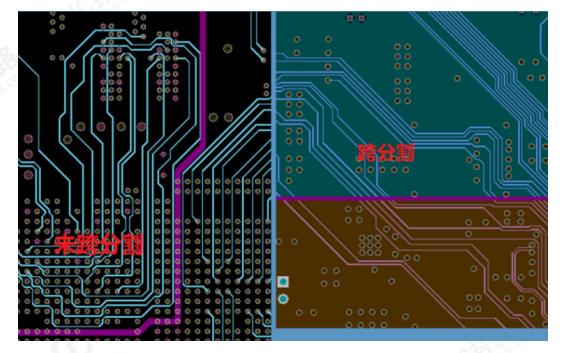

7、处理完等长后,应检查其参考层情况,不允许其跨分割。PCB上时钟信号(一般以clk结尾)等重要信号也要避免跨分割情况出现,跨分割后会导致信号阻抗突变。

图3 PCB布线夸分割

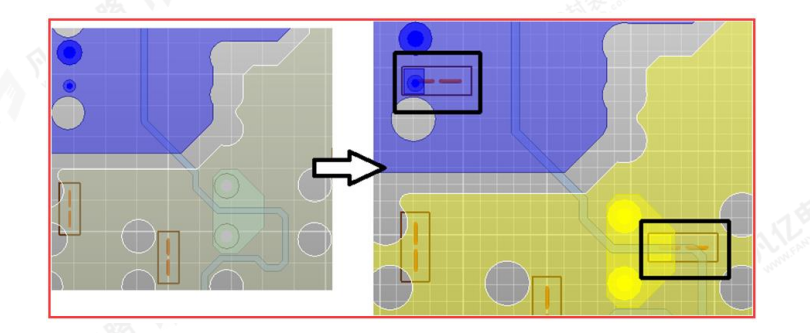

8、当走线的参考平面有跨电源层时,建议在2个电源层分别加对地电容以提供完整的回流路径,如图4所示。

图4 走线夸分割处理

9、差分信号对内等长位置应在不耦合产生的位置附近进行等长,对内等长高度及宽度参考下图5示要求。

图5 差分线的等长要求

-

pcb

+关注

关注

4318文章

23054浏览量

396884 -

PCB设计

+关注

关注

394文章

4680浏览量

85456 -

布线

+关注

关注

9文章

770浏览量

84312 -

差分线

+关注

关注

0文章

37浏览量

8902 -

差分信号线

+关注

关注

0文章

10浏览量

1960

原文标题:PCB设计中常见的走线等长要求

文章出处:【微信号:FANYPCB,微信公众号:凡亿PCB】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

PCB设计中DDR布线要求及绕等长要求

高速PCB设计常见问题

AD9446 LVDS信号线的PCB走线的差分对间等长有没有要求?

pcb开窗怎么设计_PCB设计怎样设置走线开窗

pcb设计中常见的走线等长要求是什么

pcb设计中常见的走线等长要求是什么

评论