文本转自公众号系列文章,欢迎关注

《基于“矿板”低成本学习Zynq系列》之四-第一个工程HelloWorld一下 (qq.com)

一.前言

矿板,可能一些器件都不稳定了,比如DDR,所以我们来测试下,做个压力测试。

这一篇先测试DDR,后面再测试其他的。

参考https://mp.weixin.qq.com/s/eecigPSyHQGUIx8hwSoAtQ

二.创建工程

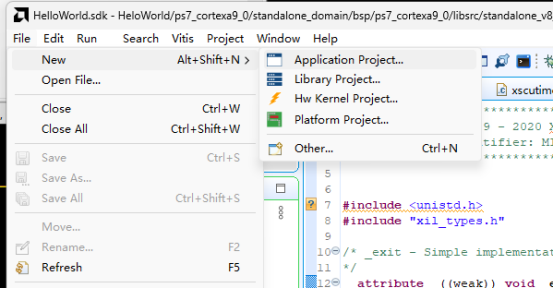

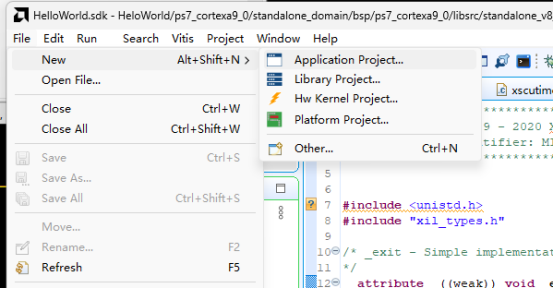

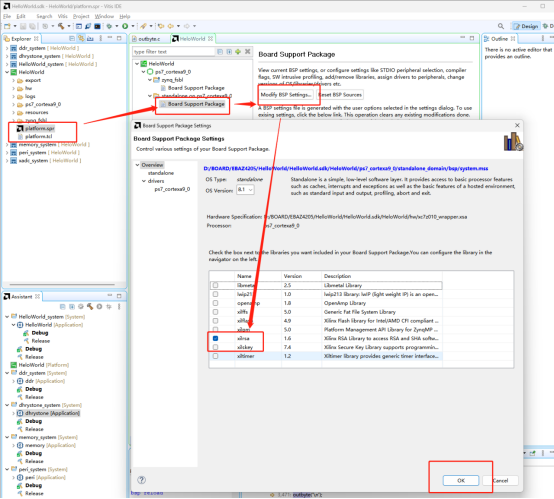

File->New->Application Project...

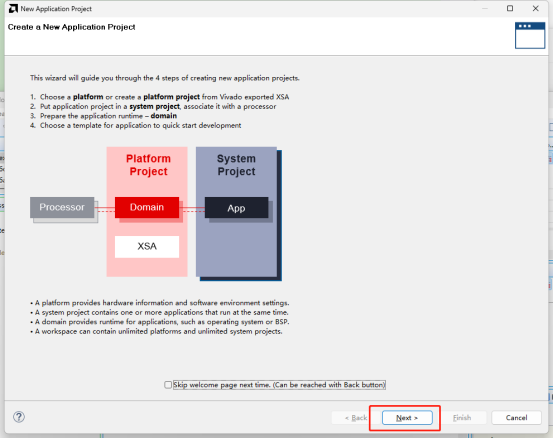

Next

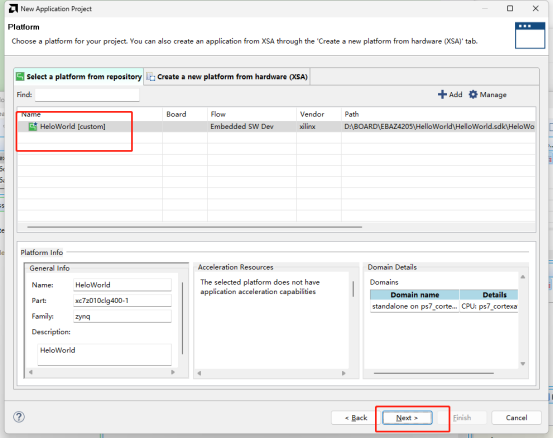

选择之前创建的平台,Next

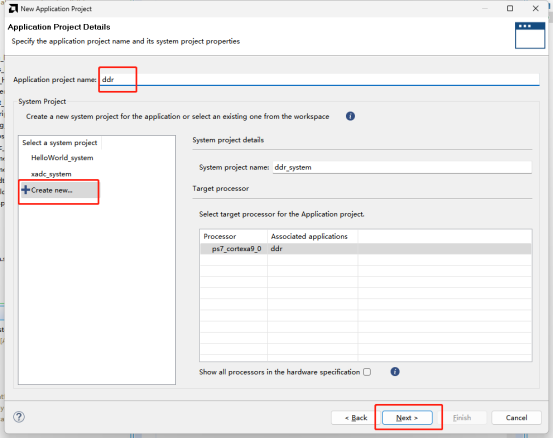

输入工程名ddr,next

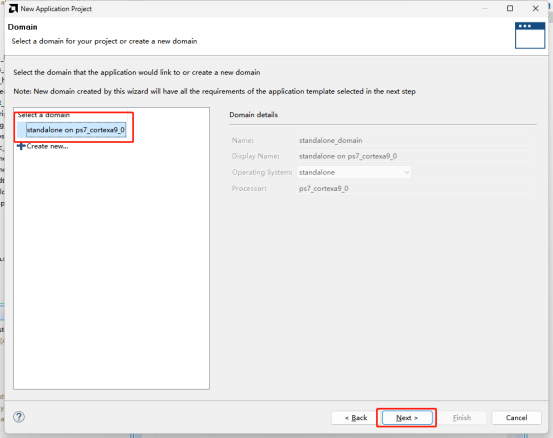

Next

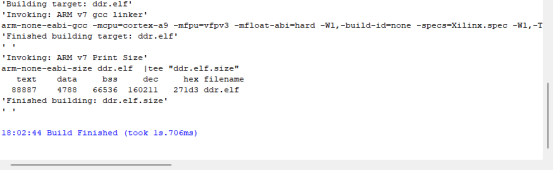

三.编译

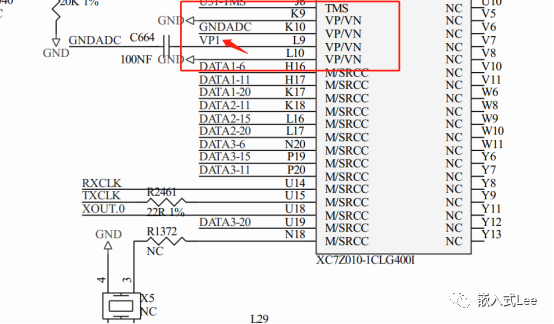

从原理图可以看出

DDR 256M 16位

EM6GD16EWKG-12H

所以

int bus_width = 32;

改为

int bus_width = 16;

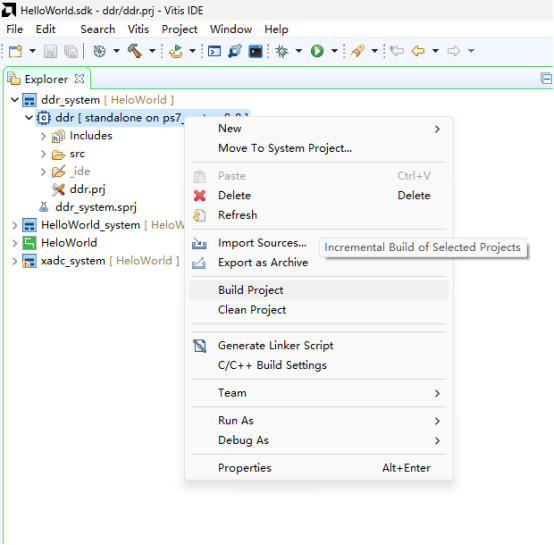

右键点击DDR工程,build project

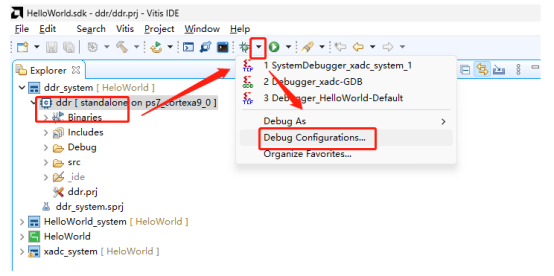

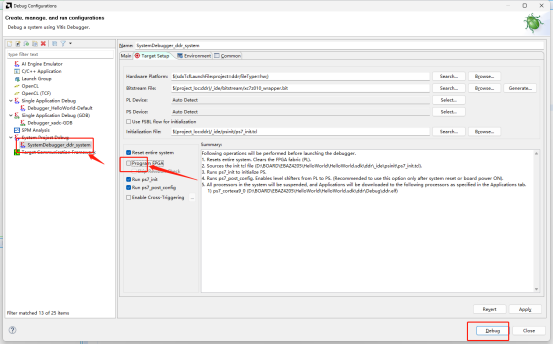

四.仿真运行

五.测试

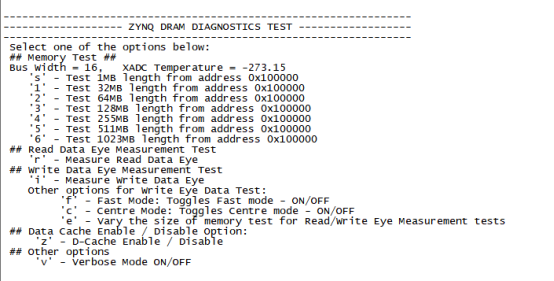

运行后打印如下

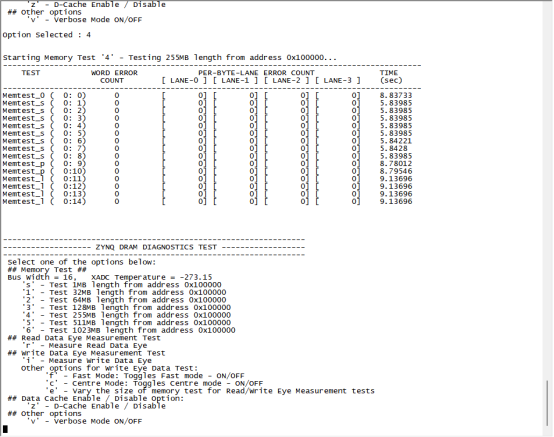

输入4测试255M的大小

r测试读眼图

i测试写眼图

六.总结

以上测试,确认DDR目前看还比较可靠,没有问题。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

测试

+关注

关注

8文章

5241浏览量

126579 -

DDR

+关注

关注

11文章

712浏览量

65311 -

眼图

+关注

关注

1文章

67浏览量

21122 -

编译

+关注

关注

0文章

655浏览量

32845 -

Zynq

+关注

关注

10文章

609浏览量

47166

发布评论请先 登录

相关推荐

请问4层板能实现zynq+ddr3吗?

想diy一个小玩意,考虑到成本问题,只使用4层板用的主要芯片就两个1.Xilinx ZYNQ XC7Z010-1CLG225 (15 * 15 0.8mm BGA)2.16bit DDR

发表于 01-08 22:50

使用Vitis 在EBAZ4205(ZYNQ)矿机上实现"Hello World!"

立即学习—60天FPGA工程师入门就业项目实战特训营(3月16日开班)Vitis是 Xilinx 最新推出的开发平台,虽然Vitis 早就在电脑上安装好了,但一直没怎么使用。现在用低成本的ZYNQ

发表于 03-06 22:59

如何调试Zynq UltraScale+ MPSoC VCU DDR控制器

Xilinx DDR 控制器。 DDR PHY 与电路板调试: Zynq UltraScale+ MPSoC VCU DDR 控制器采

发表于 01-07 16:02

低成本 MiniZed Zynq SoC 开发板

MiniZed Zynq SoC 开发板基于全新 Xilinx Zynq Z-7007S 器件,现可通过安富利订购,仅需 89 美元。该开发板为单核 ARM Cortex-A9 开发人

DDR PHY 与电路板调试

UltraScale+ MPSoC VCU(H.264/H.265 视频编解码器)连用。

因此,调试将不同于 MIG 等传统 Xilinx DDR 控制器。

DDR PHY 与电路板调试:

如何调试 Zynq UltraScale+ MPSoC VCU DDR 控制器?

UltraScale+ MPSoC VCU(H.264/H.265 视频编解码器)连用。

因此,调试将不同于 MIG 等传统 Xilinx DDR 控制器。

DDR PHY 与电路板调试:

发表于 02-23 06:00

•15次下载

Xilinx Zynq小试FPGA开发流程

Xilinx Zynq系列是带有ARM Cortex-A系列CPU核的FPGA,前几年流落到二手市场上的“矿板”就以

《基于“矿板”低成本学习Zynq系列》之六-DDR测试

《基于“矿板”低成本学习Zynq系列》之六-DDR测试

评论