开漏(open drain)(OC开集,OD开漏)

开漏电路概念中提到的“漏”就是指MOS FET的漏极。同理,开集电路中的“集”就是指三极管的集电极。

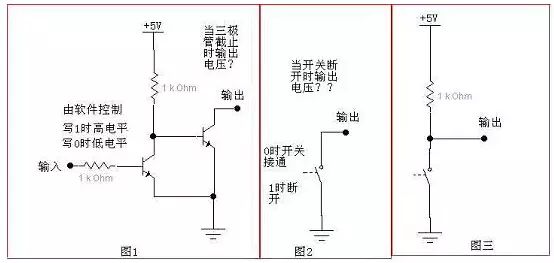

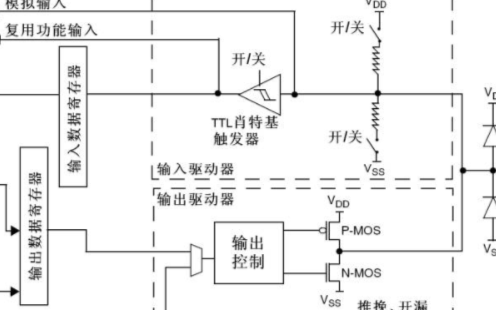

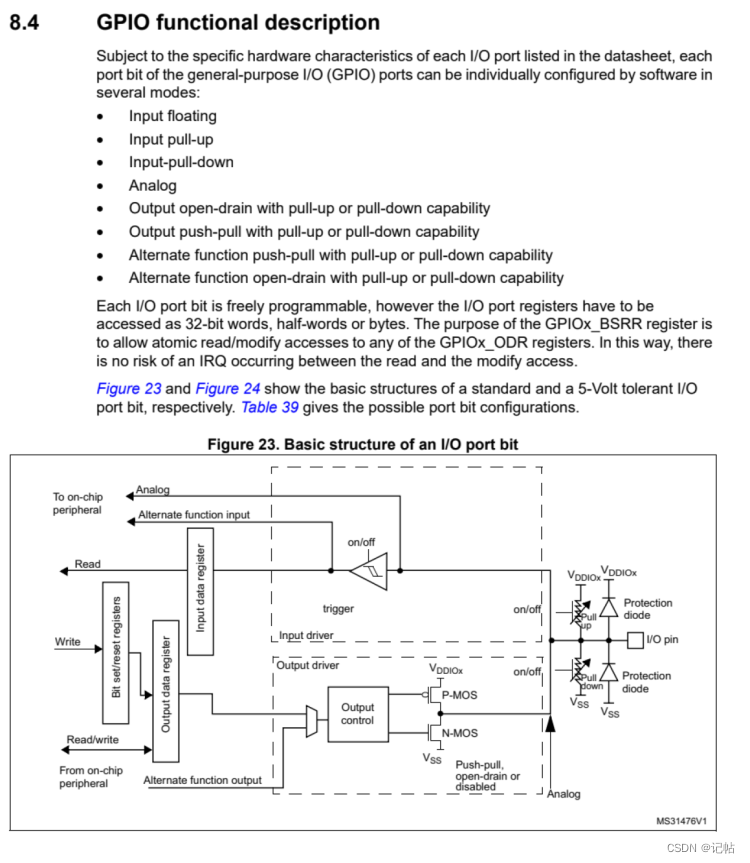

开漏电路就是指以MOS FET的漏极为输出的电路。一般的用法是会在漏极外部的电路添加上拉电阻。完整的开漏电路应该由开漏器件和开漏上拉电阻组成。组成开漏形式的电路有以下几个特点:

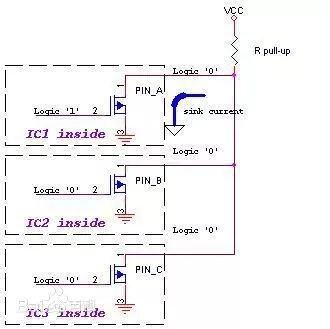

- 利用 外部电路的驱动能力,减少IC内部的驱动。当IC内部MOSFET导通时,驱动电流是从外部的VCC流经R pull-up ,MOSFET到GND。IC内部仅需很小的栅极驱动电流。

- 可以将多个开漏输出的Pin,连接到一条线上。形成 “线与逻辑” 关系。如图1,当PIN_A、PIN_B、PIN_C任意一个变低后,开漏线上的逻辑就为0了。这也是I2C,SMBus等总线判断总线占用状态的原理。

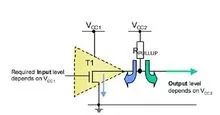

- 可以利用改变上拉电源的电压,改变传输电平。如图2, IC的逻辑电平由电源Vcc1决定,而输出高电平则由Vcc2决定。这样我们就可以用低电平逻辑控制输出高电平逻辑了。

- 开漏Pin不连接外部的上拉电阻,则只能输出低电平(因此对于经典的51单片机的P0口而言,要想做输入输出功能必须加外部上拉电阻,否则无法输出高电平逻辑)。

图1

图2

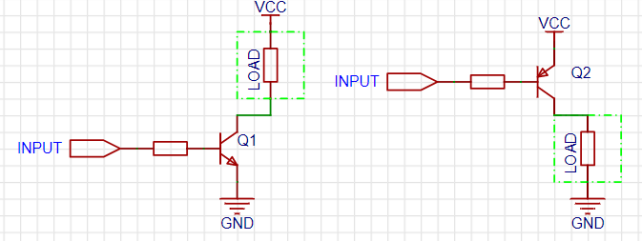

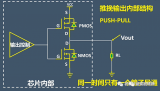

推挽电路(图腾柱电路)

推挽电路就是两不同极性晶体管连接的输出电路。推挽电路采用两个参数相同的功率BJT 管或MOSFET 管,以推挽方式存在于电路中,各负责正负半周的波形放大任务,电路工作时,两只对称的功率开关管每次只有一个导通,所以导通损耗小效率高。推挽输出既可以向负载灌电流,也可以从负载抽取电流。推挽电路适用于低电压大电流的场合,广泛应用于功放电路和开关电源中。

将端口引脚置成推挽输出方式,这将使能端口引脚驱动器。总体上来讲,数据输入端口引脚置成开漏方式、数据输出端口引脚置成推挽方式。当引脚用于输出连接上拉电阻(也就是说当与5V系统接口时)时配置成开漏输出。

-

三极管

+关注

关注

142文章

3611浏览量

121887 -

MOSFET

+关注

关注

147文章

7160浏览量

213192 -

驱动器

+关注

关注

52文章

8232浏览量

146282 -

上拉电阻

+关注

关注

5文章

359浏览量

30616 -

推挽电路

+关注

关注

18文章

113浏览量

37947

发布评论请先 登录

相关推荐

浅析开漏和推挽电路

浅析开漏和推挽电路

评论