今天我们要介绍的时序分析概念是 Combinational logic . 中文名组合逻辑单元。这是逻辑单元的基本组成器件。比如我们常见的and, or, not, nand,nor等门电路。

对于组合逻辑来说,输出只是当前输入逻辑电平的函数(有延时),与电路的原始状态无关。当前电路输入信号任何一个发生改变,输出都将发生改变。

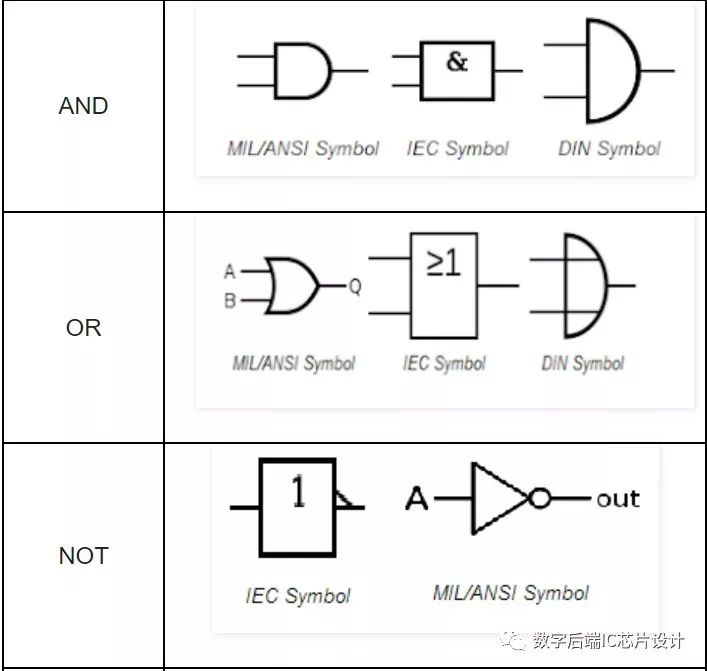

AND, OR, NOT是最基本的门电路,NAND与NOR是通用门电路,可以实现任何其他组合逻辑电路。还有一些常见的复杂组合逻辑电路,比如全加器,数据选择器,译码器等等。

下表是常见的逻辑门电路示意图:

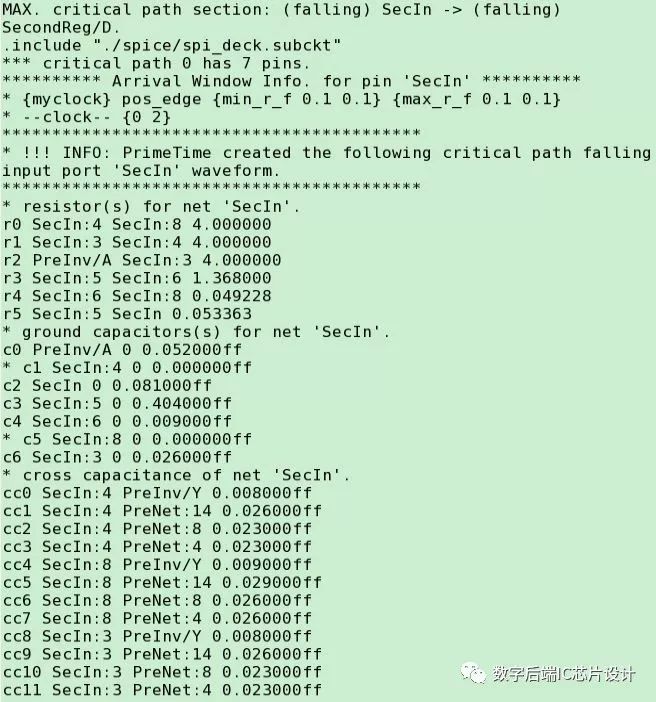

对于组合逻辑单元,每个输入pin和输出pin都会存在一个timing arc关系,这也是我们平时说的cell的delay.

如下图所示:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

门电路

+关注

关注

7文章

199浏览量

40196 -

全加器

+关注

关注

10文章

62浏览量

28527 -

时序分析

+关注

关注

2文章

127浏览量

22572 -

时序分析器

+关注

关注

0文章

24浏览量

5287 -

逻辑电平设计

+关注

关注

0文章

2浏览量

1166

发布评论请先 登录

相关推荐

时序分析基本概念介绍<Operating Condition>

今天我们要介绍的时序分析概念是 **Operating Condition** 。也就是我们经常说的PVT环境,分别代表fabrication process variations(工

时序分析基本概念介绍&lt;spice deck&gt;

今天我们要介绍的时序分析概念是spice deck。平时用得可能比较少,是PT产生的一个spice信息文件,可以用来和HSPICE做correlation。

时序分析基本概念介绍&lt;generate clock&gt;

今天我们要介绍的时序分析概念是generate clock。中文名为生成时钟。generate clock定义在sdc中,是一个重要的时钟概念

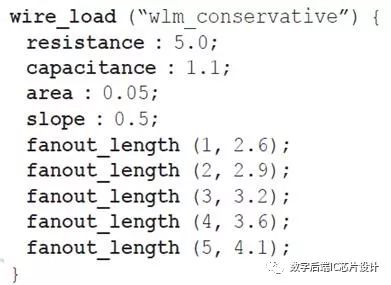

时序分析基本概念介绍&lt;wire load model&gt;

今天我们要介绍的时序分析基本概念是wire load model. 中文名称是线负载模型。是综合阶段用于估算互连线电阻电容的模型。

时序分析基本概念介绍<Combinational logic>

时序分析基本概念介绍<Combinational logic>

评论