近二十年来,PCI Express®(PCIe®)规范一直是计算领域的首选互连标准。从2010年发布的PCIe 3.0开始,每一代新标准的信号传输速率都比上一代增加一倍,而且在满足各种用例的带宽需求方面远远领先于市场。

但近年来,人工智能/机器学习(AI/ML)、高性能计算(HPC)等性能关键型应用所产生的数据呈现爆发式增长,企业也纷纷上云。面对巨大的数据流量,数据中心在数据处理和数据存储上正承受着极限压力,这也使得服务器和网络设备上的PCIe互连成为瓶颈。

PCIe 6.0 - 服务于高带宽要求的应用

为了不断满足行业对高速率、低延迟互连的需求,PCI-SIG发布了PCIe 6.0规范。该规范将数据传输速率提升至64 GT/s,相较PCIe 5.0规范(32 GT/s)带宽和能效提高了一倍。

为了实现这一带宽的巨大飞跃全新的PCIe 6标准作出了一些根本性的改变:

-PAM4调制信号:PCIe 6.0使用PAM4取代了PCIe 5.0和前几代标准所使用的NRZ调制信号,实现了更快的数据传输和更高的带宽。

-前向纠错(FEC):为了减少因PAM4调制信号而增加的误码率,PCIe 6.0加入了FEC。

-固定大小数据包(FLIT)模式:PCIe 6.0采用FLIT模式来简化控制器层面的数据管理并提高带宽效率、降低延迟和减少控制器的占用空间。

-L0p模式:PCIe 6.0利用这一低功耗模式使流量在更少的通道上运行,起到了节能的效果。

凭借这些创新,我们预计,PCIe6.0威廉希尔官方网站 将大大纾解行业所面临的带宽困境,并为数据中心带来最佳的性能。

专为PCIe 6.0打造的Rambus IP解决方案

凭借在高速信号领域30多年的专业知识和近20年的PCIe解决方案的实施经验,Rambus推出了一款专为ASIC而设计的可配置和可扩展控制器IP——PCIe 6.0控制器解决方案。

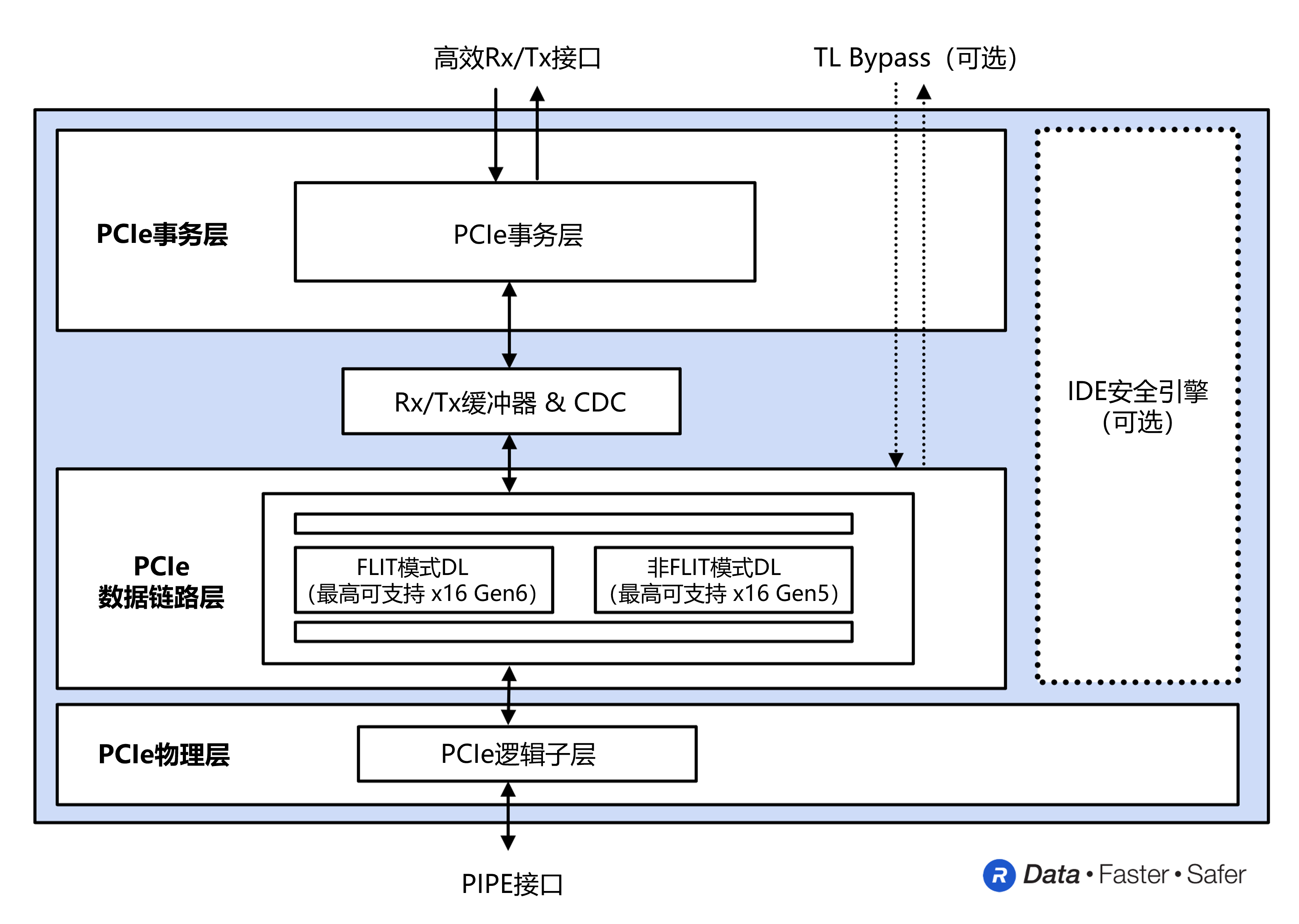

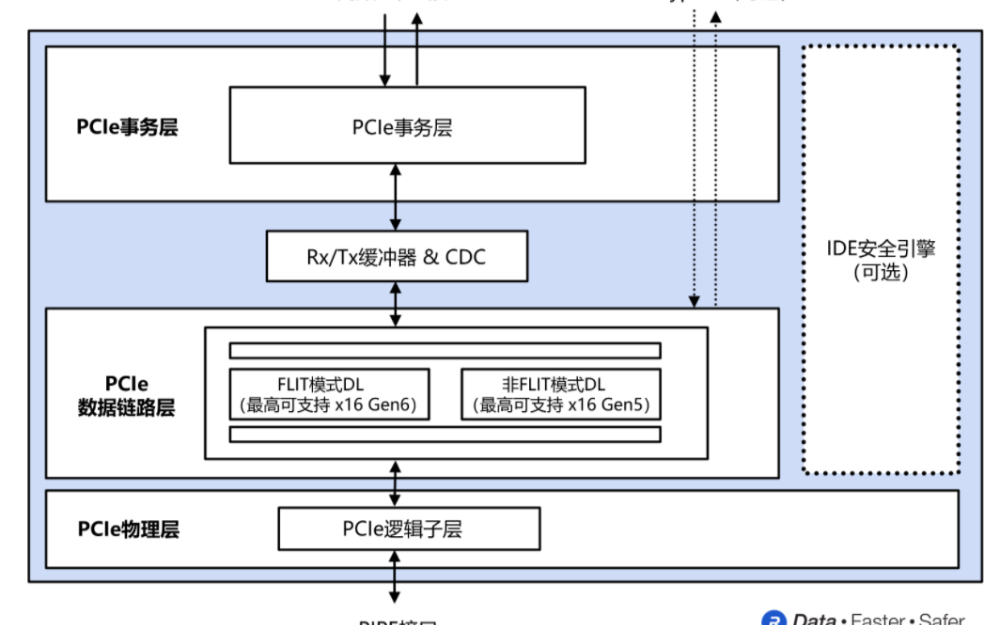

该控制器支持PCIe 6.0规范并向后兼容PCIe 5.0、4.0和3.1/3.0规范。它还支持6.x版本的PCI Express物理层接口(PIPE)规范。这款控制器提供了一个高效率的发射器(Tx)和接收器(Rx)接口,具有可配置的总线宽度。该IP旨在满足众多客户和行业用例的需求,支持端点、根端口、交换端口和双模式拓扑结构配置,可提供多种不同的使用模式。Rambus所提供的图形用户界面(GUI)向导使设计人员可以通过启用、禁用和调整大量参数,来根据他们的具体要求设定使用该IP。

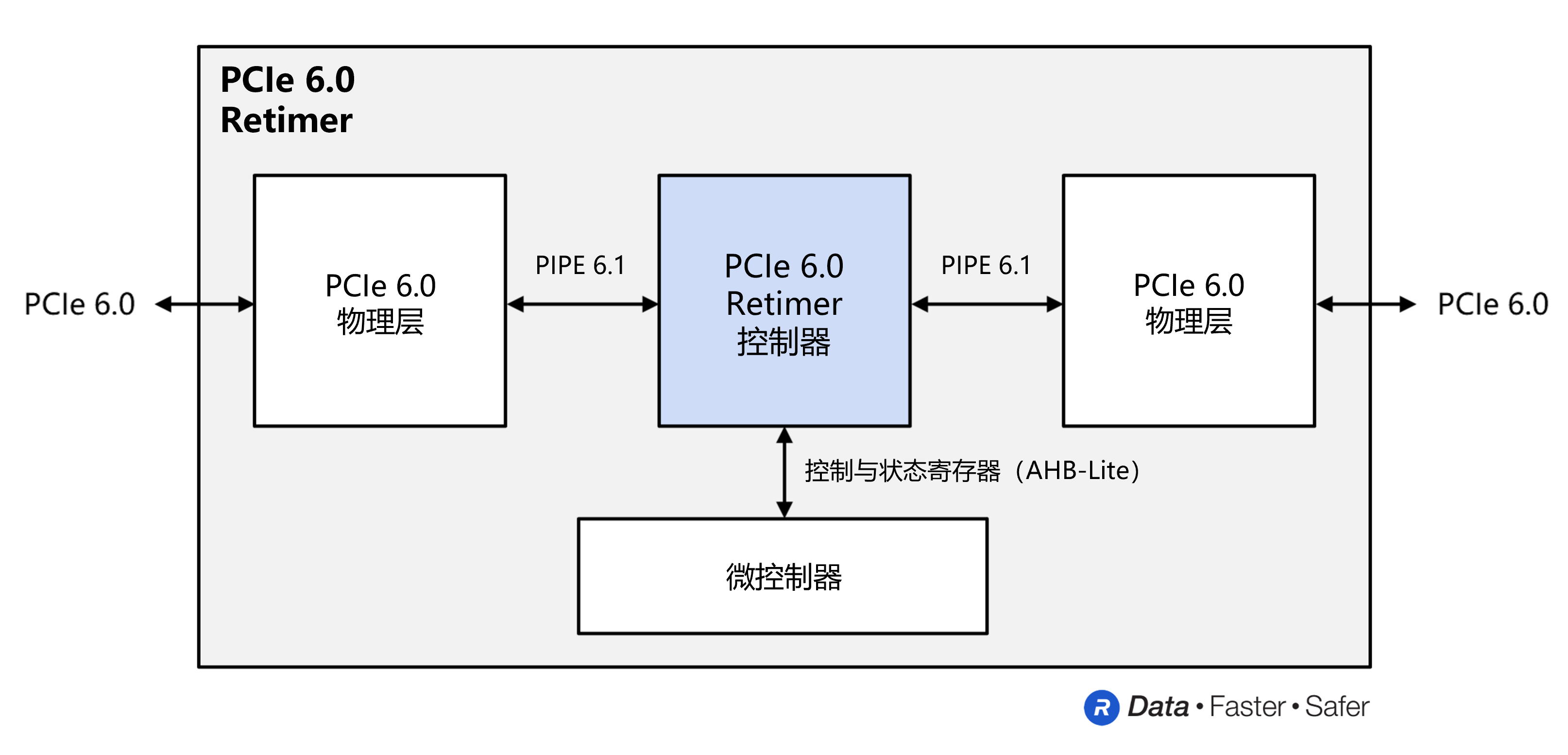

随着数据在计算系统中的价值迅速上升,保证设备内部和设备间链路的安全已成为一项关键任务。因此,Rambus PCIe 6.0控制器提供了一个集成的IDE(完整性和数据加密)安全引擎,并对其性能进行了优化。此外,Rambus还提供一个PCIe 6.0 Retimer控制器。

显示Rambus PCIe 6.0 Retimer控制器的Retimer芯片框图

威廉希尔官方网站

的进步带来对更高带宽永无止境的追求。PCIe 6.0代表了最新一代的系统接口标准,而随着PCI Express标准现以两年为一个升级周期,PCIe 6.0将成为实现更高计算性能水平的重要组成部分。

责任编辑:彭菁

-

控制器

+关注

关注

112文章

16346浏览量

177898 -

PCI

+关注

关注

4文章

666浏览量

130259 -

数据中心

+关注

关注

16文章

4769浏览量

72106

发布评论请先 登录

相关推荐

Rambus推出面向下一代数据中心的PCIe 6.0控制器

中兴选择Tundra公司PCI Express产品创建下一代

下一代数据中心对机柜系统的要求

华为数据中心能源将开启下一代智能数据中心

数据中心行业正经历着前所未有的增长和创新

400G将如何引领下一代数据中心网络

Molex莫仕Mirror Mezz Pro屡获殊荣,为下一代数据中心提供224G解决方案

谷歌将推出第六代数据中心AI芯片Trillium TPU

东盟能源和华为主编的《东盟下一代数据中心建设白皮书》正式发布

PCI Express 6.0:为下一代数据中心带来前所未有的性能

PCI Express 6.0:为下一代数据中心带来前所未有的性能

评论