引言

静态时序分析(STA)是用来分析数字电路是否满足时序目标的威廉希尔官方网站 手段之一。比如,检查CPU电路是否达到1GHz的目标频率。

本文没有目录分类,而是想先快速的讲完一个案例,然后再回个头来慢慢引出一些STA概念和知识,以便后面进行分类讲解。(ps.这个时候出现的STA专业术语只需有个印象即可。)

案例分析

某芯片回片测试发现功能异常,不符合预期。经过设计人员层层排查,锁定到某条嫌疑路径。我们画出几组精简的逻辑电路图和时序波形图来示意解释问题出在哪。

该电路不是真实案例对应的具体电路,而是为了说明问题,虚拟抽象出来的相似电路,它不影响我们对问题的探究剖析。

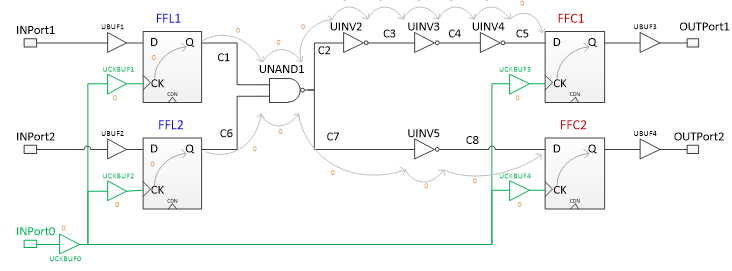

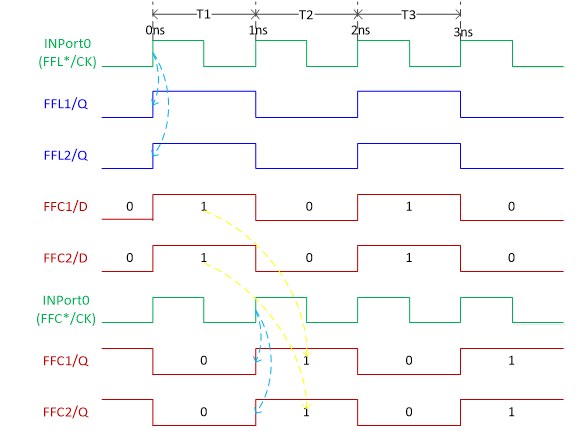

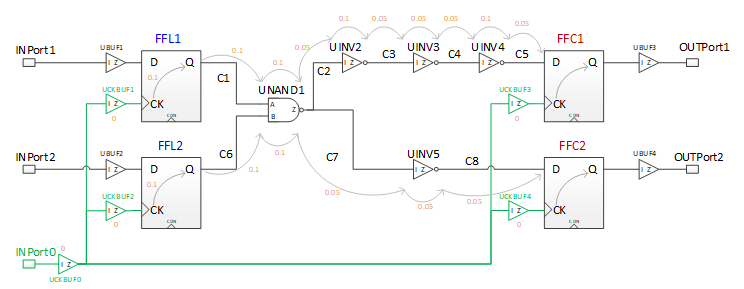

图一、图二是数字电路前端设计人员熟悉的逻辑电路图和时序波形图,其中时序波形图代表了该逻辑电路的预期功能。

图一 逻辑电路图(理想延迟)

图二 时序波形图(理想延迟)

可以看出:

在0ns时刻之前

FFL1、FFL2两个寄存器储存的逻辑值分别是0、0。

在0ns时刻时

FFL1、FFL2打出来新的逻辑值1、1,经过逻辑运算和路径传播后,到达FFC1、FFC2的D端。

在1ns时刻时

FFC1、FFC2的D端出现的1、1分别被捕获锁存进寄存器FFC1、FFC2,即T2周期FFC1、FFC2寄存器储存的逻辑值是上个周期(T1)的D端输入值。

实际芯片中,信号经过任何cell和wire都是有延迟的。而且芯片处在不同的工作环境下,这些cell和wire会有不同的延迟值。

因此在不影响问题说明的前提下,为了近一步降低理解难度,我们先假设从clock源头到任何寄存器的时钟输入端的延迟是0ns,而且假设不同工作条件下信号经过同一条wire网络具有相同的延迟值。

图三、图四是在BC工作条件下的逻辑电路图(含延迟信息)和时序波形图:

图三 逻辑电路图(含BC工作条件下的延迟信息)

图四 时序波形图( BC****工作条件)

在0ns时刻之前

FFL1、FFL2两个寄存器储存的逻辑值分别是0、0。

在0ns时刻时

FFL1、FFL2打出来逻辑1、1,这两个输出的逻辑值经过路径UNAND1、UINV2、UINV3、UINV4的逻辑运算后到达FFC1的D端。

其路径延迟 = 经过的cell延迟 + 经过的wire延迟,即:

路径延迟D(FFL1->FFC1) = D(FFL2->FFC1)

= D(FFL1CP2Q) + D(C1) ~ ~ + D(UNAND1) + D(C2) + D(UINV2) + D(C3) + D(UINV3) + D(C4) + D(UINV4) + D(C5)

= 0.1 + 0.1 + 0.1 + 0.05 + 0.1 + 0.05 + 0.05 + 0.05 + 0.1 + 0.05

= 0.75ns;

同样,两个输出经过UNAND1、UINV5的逻辑运算后到达FFC2的D端,其路径延迟为:

路径延迟D(FFL1->FFC2) = D(FFL2->FFC2)

= D(FFL2CP2Q) + D(C6) ~ ~ + D(UNAND1) + D(C7) + D(UINV5) + D(C8)

= 0.1 + 0.1 + 0.1 + 0.05 + 0.05 + 0.05

= 0.45ns;

在1ns时刻时

由于

D(FFL1->FFC1) = D(FFL2->FFC1) = 0.75ns < Tperiod – Tsetup = 1 – 0.1 = 0.9ns,

D(FFL1->FFC1) = D(FFL2->FFC1) = 0.75ns > Thold = 0.1ns,

D(FFL1->FFC2) = D(FFL2->FFC2) = 0.45ns < Tperiod – Tsetup = 1 – 0.1 = 0.9ns,

D(FFL1->FFC2) = D(FFL2->FFC2) = 0.45ns > Thold = 0.1ns,

所以FFC1、FFC2的D端出现的1、1能可靠的分别被捕获锁存进寄存器FFC1、FFC2,即T2周期FFC1、FFC2寄存器锁存了上个周期(T1)的D端输入值。

**可见,在BC工作条件下,计算了cell和wire延迟后,电路功能依然符合预期。 **

图五、六是在WC工作条件下的逻辑电路图(含延迟信息)和时序波形图。

图五 逻辑电路图(含WC工作条件下的延迟信息)

图六 时序波形图( WC****工作条件)

在0ns时刻时

FFL1、FFL2打出来逻辑1、1,这两个输出的逻辑值经过路径UNAND1、UINV2、UINV3、UINV4的逻辑运算后到达FFC1的D端,其路径延迟为:

路径延迟D(FFL1->FFC1) = D(FFL2->FFC1)

= D(FFL1CP2Q) + D(C1) ~ ~ + D(UNAND1) + D(C2) + D(UINV2) + D(C3) + D(UINV3) + D(C4) + D(UINV4) + D(C5)

= 0.2 + 0.1 + 0.2 + 0.05 + 0.2 + 0.05 + 0.1 + 0.05 + 0.2 + 0.05

= 1.2ns;

同样,两个输出经过UNAND1、UINV5的逻辑运算后到达FFC2的D端,其路径延迟为:

路径延迟D(FFL1->FFC2) = D(FFL2->FFC2)

= D(FFL2CP2Q) + D(C6) ~ ~ + D(UNAND1) + D(C7) + D(UINV5) + D(C8)

= 0.2 + 0.1 + 0.2 + 0.05 + 0.1 + 0.05

= 0.7ns;

在1ns时刻时

与前面两种情况不同,在这种场景下,在1ns时刻时出现在FFC1、FFC2的D端的是0、1(上面场景出现的是1、1)。

因此,此时锁存进FFC1、FFC2寄存器的值分别是0、1。与我们所预期的T2周期FFC1、FFC2寄存器值是1、1不同。

至此,芯片功能测试异常的原因我们已经找到。简单的说即芯片中去往FFC1的D端的这2条路径(没看错,是2条),在实际运行场景中的某个时刻,恰好处于接近WC的工作条件,导致FFC1在某时刻采样错误,表现出来芯片功能异常。

-

逻辑电路

+关注

关注

13文章

494浏览量

42623 -

寄存器

+关注

关注

31文章

5343浏览量

120373 -

STA

+关注

关注

0文章

51浏览量

18965 -

静态时序分析

+关注

关注

0文章

28浏览量

9587 -

ffc连接器

+关注

关注

1文章

12浏览量

8412

发布评论请先 登录

相关推荐

[MATLAB智能算法30个案例分析].史峰等.扫描版

从一个账号开始玩转机智云(应用构建)

HLS系列 – High Level Synthesis(HLS) 从一个最简单的fir滤波器开始4

HLS系列 – High LevelSynthesis(HLS) 从一个最简单的fir滤波器开始5

STA分析-从一个案例开始

STA分析-从一个案例开始

评论