声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

时序分析

+关注

关注

2文章

127浏览量

22565 -

STA

+关注

关注

0文章

51浏览量

18958 -

时序分析器

+关注

关注

0文章

24浏览量

5277 -

时序路径

+关注

关注

0文章

12浏览量

1397

发布评论请先 登录

相关推荐

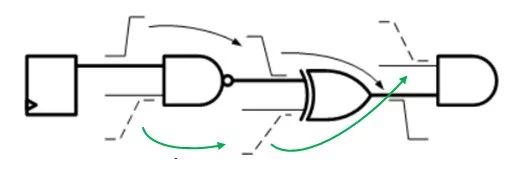

【时序约束】关于设置FALSE PATH

总得来说,FALSE PATH就是我们在进行时序分析时,不希望工具进行分析的那些路径。一般不需要工具时序分析的路径指的是异步的

发表于 06-27 06:34

Vivado下显示指定路径时序报告的流程

Vivado运行Report Timing Summary时,只显示各个子项目最差的十条路径,很可能并不包含你最关心的路近,这个时候显示指定路径的时序报告就显得很重要了,下面就简单

发表于 01-15 16:57

Timing Groups and OFFSET Const

Timing Groups and OFFSET Constraints:

•Use the Constraints Editor to create groups of path

发表于 01-11 08:55

•4次下载

Path-Specific Timing Constrain

Path-Specific Timing Constraints:Constraining Between Risingand Falling Clock Edges•

发表于 01-11 08:56

•10次下载

基于FALSE PATH的设置

总得来说,FALSE PATH就是我们在进行时序分析时,不希望工具进行分析的那些路径。一般不需要工具时序分析的路径指的是异步的

发表于 09-19 10:46

•0次下载

静态时序分析基础与应用

STA的简单定义如下:套用特定的时序模型(Timing Model),针对特定电路分析其是否违反设计者给定的时序限制(Timing Constraint)。以分析的方式区分,可分为

发表于 04-03 15:56

•10次下载

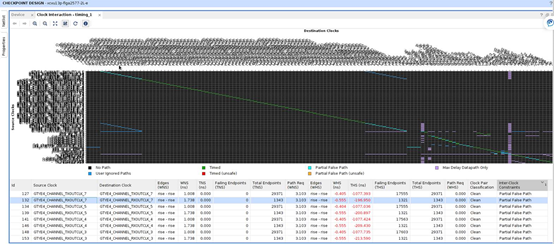

如何判断路径的timing exception约束

随着设计复杂度和调用IP丰富度的增加,在调试时序约束的过程中,用户常常会对除了自己设定的约束外所涉及的繁杂的时序约束感到困惑而无从下手。举个例子,我的XDC里面并没有指定set_false_path

AOCV时序分析概念介绍

今天我们要介绍的时序分析概念是 **AOCV** 。全称Stage Based Advanced OCV。我们知道,在OCV分析过程中,我们会给data path,clock path上设定单一的

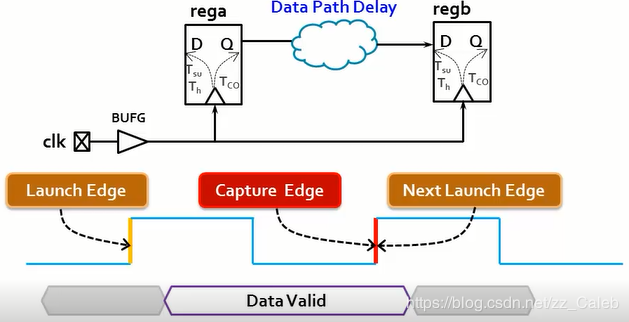

什么是时序路径timing path呢?

什么是时序路径timing path呢?

评论