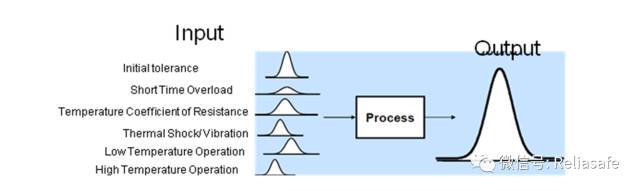

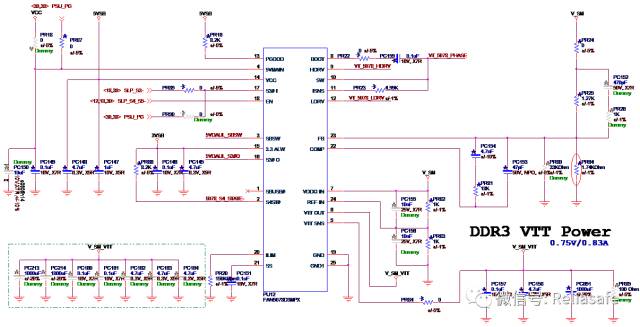

在产品的电路设计时,我们常常苦恼于电路输出的精度问题。尤其在一些关键电路部分,一些较大的电压波动会造成严重的器件失效。因为通过组合来实现某一功能的电路系统,都是有各种各样的元器件组成,例如电阻,电容,以及IC等等。而每个元器件总是存在由于各种因数导致的变异性,这就使得系统的输出有很大的变异,因此降低了输出的精确度。如图所示:

容差分析方法就是用来分析电路的组成部分在规定的使用环境范围内其参数偏差和寄生偏差参数对电路性能容差的影响,并根据分析结果提出相应的改进措施。

**1. **电性能参数发生变化的原因:

电路性能参数发生变化的主要现象有:性能不稳定,参数发生漂移,退化等,造成这些现象的原因有以下三种:

v 组成电路的元器件参数存在着公差

电路设计时通常只采用元器件参数的标称值进行设计计算,忽略了参数的公差。而元器件的实际参数值并不一定是标称值,因此原有的计算必然会引起偏差。如标称值为1000Ω,精度为±10%的电阻,其实际阻值可能在900Ω~1100Ω范围内,此时根据标称值确定的电路性能参数实际上会出现参数偏差。这种原因产生的参数偏差是固定的。

v 环境条件的变化产生参数漂移

环境温度、相对湿度的变化、电应力的波动,会使电子元器件参数发生变化,在设备工作过程中各种干扰会引起电源电压波动,从而使电源电压和元器件参数的实际值变化,偏离标称值没,产生漂移。漂移之后的元器件参数就可能会使电路性能参数超出允许范围。这种原因产生的偏差在多种情况下是可逆的,即随条件而改变,参数可能恢复到原来的数值。

v 退化效应

很多电器产品在长期的使用过程中,随着时间的累积,元器件参数会发生变化。这种原因产生的偏差是不可逆的。

通常元器件包含哪些变异因数呢?通过经验总结,我们可以知道:

– Initial tolerance

– TemperatureCoefficient of Resistance

– Load LifeStability (Aging)

– Short TimeOverload

– Effects ofSoldering

– TemperatureCycling

– MoistureResistance (Humidity Exposure)

– Low TemperatureOperation

– High TemperatureOperation

– Terminal Strength-Bend(Manufacturing Associated Stress)

– Thermal Shock

– Vibration

**2. **容差分析程序:

1)确定待分析电路

根据电路的重要性、经费与进度等的限制条件以及FMEA或其他分析结果来确定需要进行容差分析的关键电路。主要有:

· 严重影响产品安全的电路;

· 严重影响功能实现的电路;

· 价格昂贵的电路;

· 采购或制作困难的电路;

· 需要特殊保护的电路。

- 明确电路设计的有关基线

电路设计的基线包括:

· 被分析电路的功能和使用寿命;

· 电路使用的环境应力条件(或环境剖面);

· 元器件参数的标称值、偏差值和分布;

· 电源和信号源的额定值和偏差值;

· 电路接口参数。

对电路进行分析,得出在各种工作条件下及工作方式下电路的性能参数、输入量和元器件参数之间的关系。

- 容差分析

a) 根据已确定的待分析电路的具体要求和条件,,适当选择一种具体分析方法;

b) 根据已明确的电路设计的有关基线按选定的方法对电路进行容差分析,求出电路性能参数偏差的范围,找出对电路性能影响敏感较大的参数并进行控制,使电路满足要求。

- 分析结果判别

把容差分析所得到的电路性能参数的偏差范围与规定偏差要求相比较,比较结果分两种情况:

a) 符合要求,结束分析。

b) 若不符合要求,则需要修改设计(重新选择电路组成部分参数或其精度等级或更改原电路结构)。设计修改后,仍需进行容差分析,直到所求得的电路性能参数的偏差范围满足偏差要求为止。

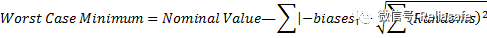

**3. ** 最坏情况分析法(Worstcase analysis )

最坏情况分析法是分析在电路组成部分参数最坏组合情况下的电路性能参数偏差的一种非概率统计法。它利用已知元器件参数变化极限来预计电路性能参数变化是否超过允许范围。在预计电路性能参数变化范围内,元器件参数的变化取决于它们的上、下极限值。如果预计的电路性能参数在规定的范围,就可以确信该电路有较高的稳定性。如果预计值超出了规定的允许变化范围,就可能发生漂移故障。最坏情况分析法可以预测某个电路是否发生漂移故障,并提供改进的方向,但是不能确定发生这种故障的概率。

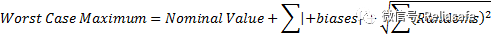

Example : Thefollowing example illustrates a reprehensive calculation for deterring theworst case minimum and maximum values for a 1200µf CLR capacitor.

Worst Case Minimum (RSS) =-48-22.4=-70.4%

Worst Case Maximum (RSS) =+29+22.4=+51.4%

Worst Case Minimum Capacitance (RSS) = 1200µf -1200µf (0.48+0.224) =355.2 µf

Worst Case Maximum Capacitance (RSS) = 1200µf +1200µf (0.298+0.224) =1816.8 µf

**4. ** 蒙特卡洛仿真分析(MonteCarlo Analysis )

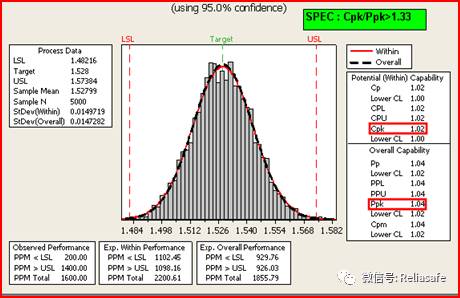

上面提到单纯的最坏情况分析法不能确定发生这种故障的概率,如果利用蒙特卡洛仿真则能有效的解决这个问题。蒙特卡洛分析法针对电路在最坏情况下的性能提供最真实可行的风险评估.根据元器件参数变化范围产生随机数进行稳态电路模拟,通常需要随机产生至少需要5000个数据以上.在产生随机数之前,我们必须知道所分析电路的功能方程式.然后把这些随机带入方程式,利用Minitab计算出输出电压值。最后计算出这组数据的Cpk 和Ppk。

当Cpk和Ppk在95%置信度水准下大于1.33时,我们认为设计符合要求。这里有一点需要特别提出的是,在计算Cpk和Ppk时必须首先要跟设计人员确认好输出值的公差范围。

5**. **案例分析

假设一个内存的供电电路设计为DCto DC ,输出电压的公差为±3%,我们需要评估该电路的设计是否符合要求。

a) 通过分析,我们可以得到:

Vout_DDR3_Sta=PU12*(1+PR25/PR64)

b) 其中的元器件各有3家供应商。

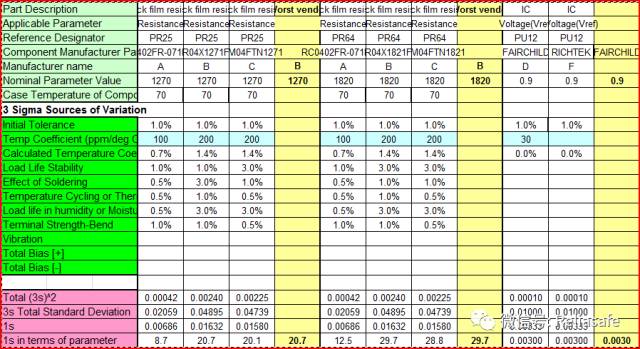

参照元器件Datasheet,整理各个参数得到:

c) 在Minitab中利用calc中的随机数功能,根据电路实现的方式基于整套分布,interwetten与威廉的赔率体系 出5000个输出电压值。如图所示:

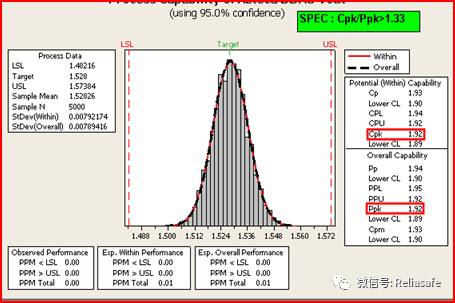

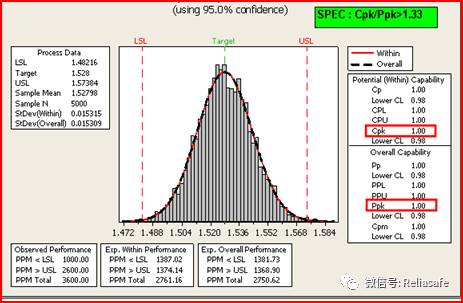

d) 同样利用Minitab计算出这组输出数据的Cpk/Ppk。输出电压为:1.528V+/-3%.

A 厂商:

B厂商:

C厂商:

如图所示,只有A厂商元器件各个参数才能满足CPk>1.33的要求。改进的方法是选择变异更小的电阻,来使得另外两家元器件的电阻可以满足设计的要求。

-

DDR3

+关注

关注

2文章

276浏览量

42246 -

电源电压

+关注

关注

2文章

989浏览量

23970 -

FMEA

+关注

关注

1文章

96浏览量

13607

发布评论请先 登录

相关推荐

最坏情况下电路容差的分析及改进措施

最坏情况下电路容差的分析及改进措施

评论