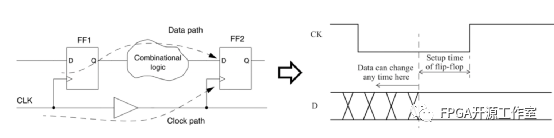

1 setup time

Setup time (建立时间)是数据信号(D)在时钟事件(这里以时钟上升沿为例)发生之前保持稳定的最小时间。以便时钟可靠地对数据进行采样。适用于同步电路,如触发器(flip-flop)。

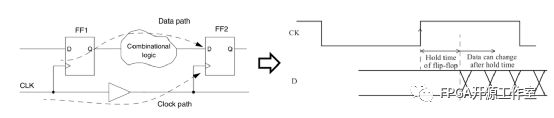

2 hold time

Hold time (保持时间) 是数据信号(D) 在时钟事件(这里以时钟上升沿为例)发生之后保持稳定的最小时间。

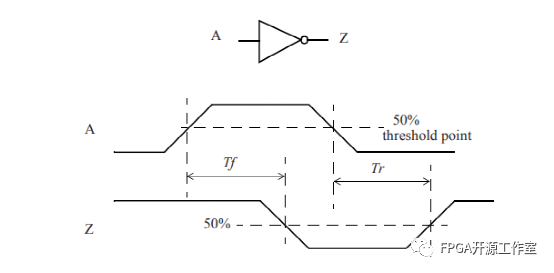

3 Propagation Delay

信号传播延时(Propagation Delay),以反相器(Inverter)为例,A输入信号变化(0-1的50%)为开始,到Z输出信号变化(1-0的50%)所需的时间称为Tf, A输入信号变化(1-0的50%)为开始,到Z输出信号变化(0-1的50%)所需的时间称为Tr。

Output fall delay (Tf)

Output rise delay (Tr)

# Threshold point of an input falling edge: input_threshold_pct_fall : 50.0; # Threshold point of an input rising edge: input_threshold_pct_rise : 50.0; # Threshold point of an output falling edge: output_threshold_pct_fall : 50.0; # Threshold point of an output rising edge: output_threshold_pct_rise : 50.0;

审核编辑:刘清

-

触发器

+关注

关注

14文章

2000浏览量

61160 -

时序分析

+关注

关注

2文章

127浏览量

22566 -

同步电路

+关注

关注

1文章

60浏览量

13311

原文标题:时序分析的基本概念(1)

文章出处:【微信号:leezym0317,微信公众号:FPGA开源工作室】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

时序分析基本概念

时序分析基本概念介绍

FPGA设计中时序分析的基本概念

时序分析基本概念介绍—Timing Arc

时序分析基本概念解析

时序分析的基本概念

时序分析的基本概念

评论