什么是dB?

其中dB概念怎么去消耗?其实要说对于dB概念最熟悉的莫过于射频工程师了,但是要好好把这个讲给局外人吸收掉,或许并不是一件特别容易的事,特别是对于常年不接触,只是偶尔才会碰到的人来说,更是困难。我也想别人一说dB,就能脑海里所有关于dB的内容都蹬蹬的冒出来,所以,我也不敢说自己说的怎么样,我只是想按照自己的方式来了结这个内容。

首先,dB****是一种纯计数方法,是一种比值,没有单位。

(感觉这个很基础吧,如果连这个都不懂,说出来好像很尴尬,所以必须清楚。)

既然是比值,则必然要有对比的对象,就像一个黑夹子的两端,输入与输出的对比:

在实际中主要用来对比的对象,是电压电流或者功率。

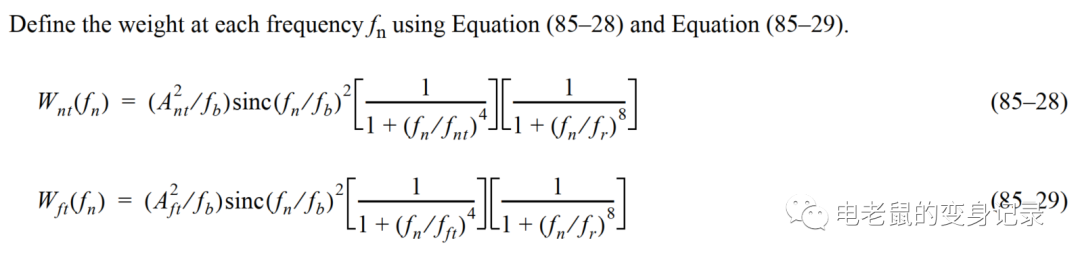

功率: dB = 10*lg(A/B)

电压或电流: dB = 20*lg(A/B)

(功率P = U²/R = I²R)

这里我们看到了公式是以10为底的对数,所以,想起了咱们的高中最熟悉的图如下:

有没有很熟悉,其中的x = OUTPUT/INPUT,a=10.

所以dB的曲线趋势则为上图的红色曲线。

记住这幅图的话,我觉得对于dB的理解还是会有很大的帮助的。

(比如假设你很陌生dB的概念,人家说dB的时候,你一头雾水,比如人家说减少了1个dB,那是怎么回事呢?这是可以马上画个草图,标一下点,哦,原来是说输出比输入少了一些,原来如此,这样的话,再也不怕别人提dB啦,因为我知道你在说什么。)

其次,为什么用dB ?——简化。

比如你可以常常听到工程师说下降了1个dB,假设这时候输入是1.3V,那么1个dB经过换算,可得输出为1.45862399059255V,不管是听的还是说的人,可能相对的更愿意听到前者而不是后者这么一大串数据吧。

再者,为什么是-27dB****或者-29dB?

我们可以换算一下,这里LPDDR的工作电压为1.2V,换算可得串扰阈值为46~58mV,即串扰容限大致在3.8%4.8%之间,此时如果升电压为1.3V,则,按同样的串扰容限进行换算,可接受的串扰阈值为49.862.8mV,可见,在同样的容限比例下,串扰阈值的空间加大了,因此,我想为什么有时候DDR出现问题,升压是可以解决部分问题的,但是升压同样也将带来另外的问题,功耗变大,为什么功耗为变大呢?(P= U²/R)

另外,关于信号串扰的阈值,我们可以在李玉山《信号完整性分析》书中得到一些经验值,5%。实际中,如果无法得到原厂提供的标准,可以以此为基准,当然是越小越好,如果能做到3%左右,我想当下阶段基本也都能够满足要求的。

然后,回顾串扰一些相关理论,我们知道,一般串扰只考虑其临边两线对齐造成的影响即可,又所谓的三线制串扰。

操作步骤概要:

①导出合适格式的PCB文件。

② ADS导入PCB文件,并进行简化处理。

③仿真环境的搭建。

④仿真以及仿真结果的数据处理与分析

-

DDR

+关注

关注

11文章

712浏览量

65341 -

ADS仿真

+关注

关注

0文章

71浏览量

10439 -

信号串扰

+关注

关注

0文章

15浏览量

8583

发布评论请先 登录

相关推荐

PCB设计与串扰-真实世界的串扰(下)

PCB设计与串扰-真实世界的串扰(上)

几张图让你轻松理解DDR的串扰

高速差分过孔产生的串扰情况仿真分析

DDR跑不到速率后续来了,相邻层串扰深度分析!

基于Cadence的DDRⅡ仿真设计

DDR串扰仿真笔记

DDR串扰仿真笔记

评论