我们已经看到了交错带来的优势以及所有不错的速度和带宽带来的一些缺点。现在让我们继续讨论几个读者在不同点上评论过的另一个话题。

这个问题围绕着ADC的噪声贡献因素。在评估ADC的噪声时,我们需要考虑哪些事项?噪声可以通过多种方式进入ADC。在接下来的几篇博客中,我们将介绍噪声进入ADC的所有门口,并可能出现在输出数据的FFT中。首先,我们将从确定门口开始。

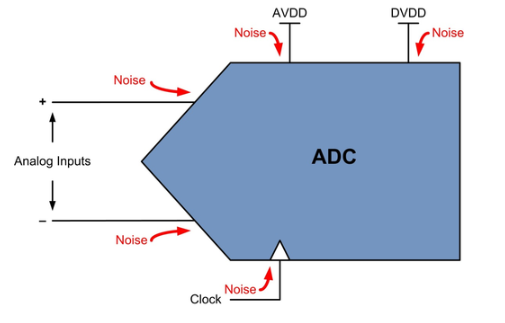

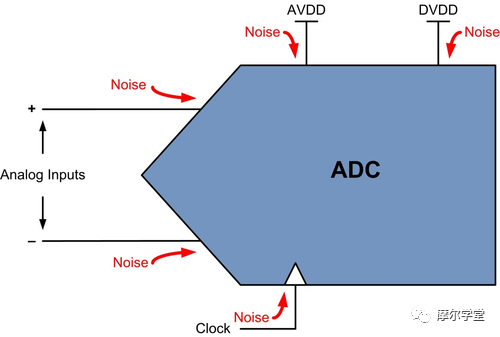

在考虑ADC中的噪声时,几乎可以将ADC视为混频器。如果有噪声从各种门口中的任何一个进入ADC,则噪声可以表现在输出数据的FFT中。如图1所示,噪声可以通过电源输入、interwetten与威廉的赔率体系 输入和时钟进入转换器。

图1

ADC噪声“门口”

由于噪声在这里是一个相当宽松的术语,让我们根据所讨论的ADC的输入(门口)来赋予它更多的含义。我们将从图表的顶部开始,逆时针方向工作。

电源输入是噪声进入ADC并出现在输出数据的FFT中的路径。在这种情况下,有几种方法可以评估这种噪声及其对ADC性能的影响。ADC的设计应使器件本身衰减来自电源的噪声输入。这里用于评估电源噪声的测量值是电源抑制比(PSRR)和电源调制比(PSMR)。通过测量这两个参数,我们可以了解ADC处理通过电源输入输入的噪声的能力。稍后我们将更详细地介绍这一点。现在,让我们继续看噪音门口。

接下来,让我们看一下ADC的模拟输入。从这个角度来看,必须从两个方面考虑噪声。首先,一般宽带噪声通过模拟输入进入转换器,通常来自信号链中ADC之前的组件。我们可以为ADC选择噪声极低的驱动放大器,但放大并输入ADC的噪声量仍然有限。

为了帮助解决这个问题,ADC的输入端通常使用抗混叠滤波器(AAF)。这有助于滤除可能进入ADC的大部分宽带噪声。这最终体现在ADC的信噪比(SNR)中。除宽带噪声外,杂散成分和谐波也可以通过模拟输入进入ADC。AAF 也有助于过滤这些。这将反映在ADC的无杂散动态范围(SFDR)上。拥有良好的 AAF 设计来帮助这两个方面非常重要。同样,我们将在以后的博客中更详细地研究这一点。

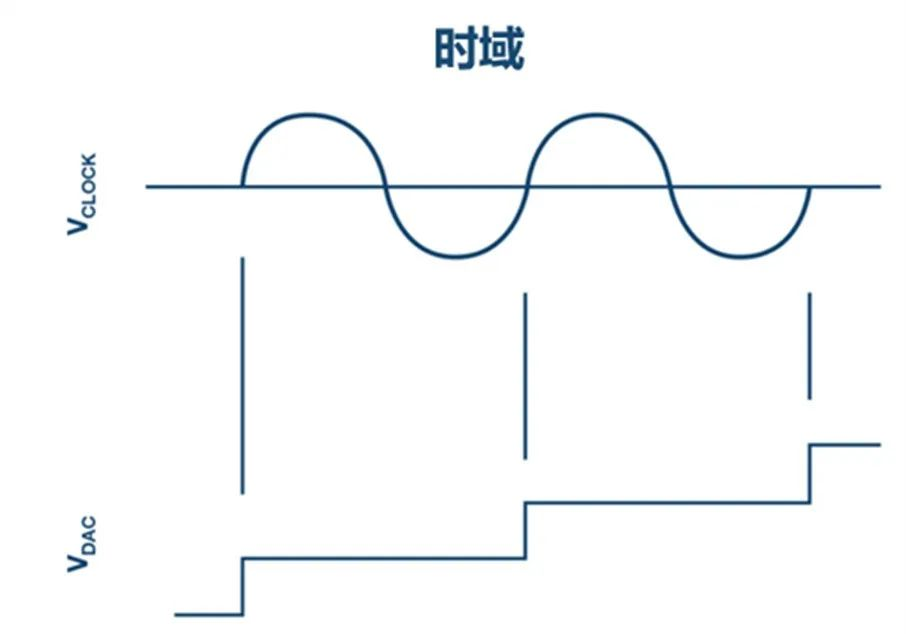

当我们围绕ADC逆时针移动时,我们看到的最后一个门口是时钟输入。该输入与模拟输入类似,允许宽带噪声以及杂散和谐波成分进入ADC,并出现在输出数据的FFT中。确保选择适当的时钟输入驱动器,为ADC提供干净的低抖动输入时钟非常重要。

该时钟信号应以这样一种方式路由到ADC,使其不会耦合到可能进入ADC的噪声中。与模拟输入类似,时钟输入端可以使用滤波器来帮助滤除可能通过时钟输入进入ADC的噪声。同样,与模拟输入的情况一样,通过时钟输入的噪声机制可以在ADC的SNR和SFDR性能中体现出来。

在使用ADC设计系统时,必须考虑所有这些门口。我们看到,我们应该将ADC视为一个混频器,它将来自这些门口中的任何一个的各种噪声成分混合到FFT的输出数据中。显然,系统设计人员希望仅在ADC的输出端获得所需信号。为此,我们必须对每个输入采取适当的步骤,以确保噪声最小化并且不会进入这些门口。请继续关注我们更深入地探讨这些输入中的每一个,并更详细地评估噪声如何耦合到ADC中,以及可以采取哪些措施来防止噪声。

审核编辑:郭婷

-

滤波器

+关注

关注

161文章

7805浏览量

178061 -

adc

+关注

关注

98文章

6497浏览量

544547 -

混频器

+关注

关注

10文章

679浏览量

45678

发布评论请先 登录

相关推荐

当堆栈被配置为空Mac地址时,无法理解Mac地址从何而来

STM32CubeIDE生成的固件文件字节从何而来

使用QSPI外设读写外部闪存存在的延迟从何而来?该如何解决?

SAI模块输出不包括WS信号,RT1024上的WS从何而来?

无线电威廉希尔官方网站 NFC、RFID从何而来?

嵌入式系统上的软件从何而来

步进电机的抖动和噪音从何而来 如何使步进电机完全静音

ADC噪声:从何而来?

ADC噪声:从何而来?

评论