JK触发器是一种可以设置、重置和切换的人字拖。它可用于制造计数器、事件检测器、分频器等等。

在本教程中,您将了解它的工作原理、其真值表以及如何使用逻辑门构建一个。

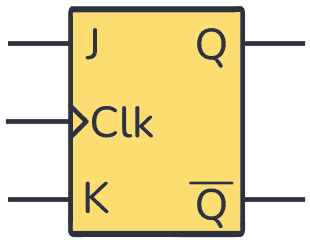

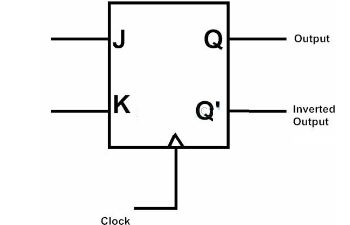

JK 触发器符号

JK 触发器符号

什么是 JK 触发器?

触发器是可以在其输出上存储数字值的组件。它们有一个时钟输入(Clk),用于确定何时可以更改输出状态。

与你的想法相反,JK

Flip-Flop的两个输入“J”和“K”并不是引脚功能的缩写(S-R锁存器就是这种情况)。它们的发明者杰克·基尔比(JK)选择了它们,以将他的人字拖设计与其他类型的人字拖设计区分开来。

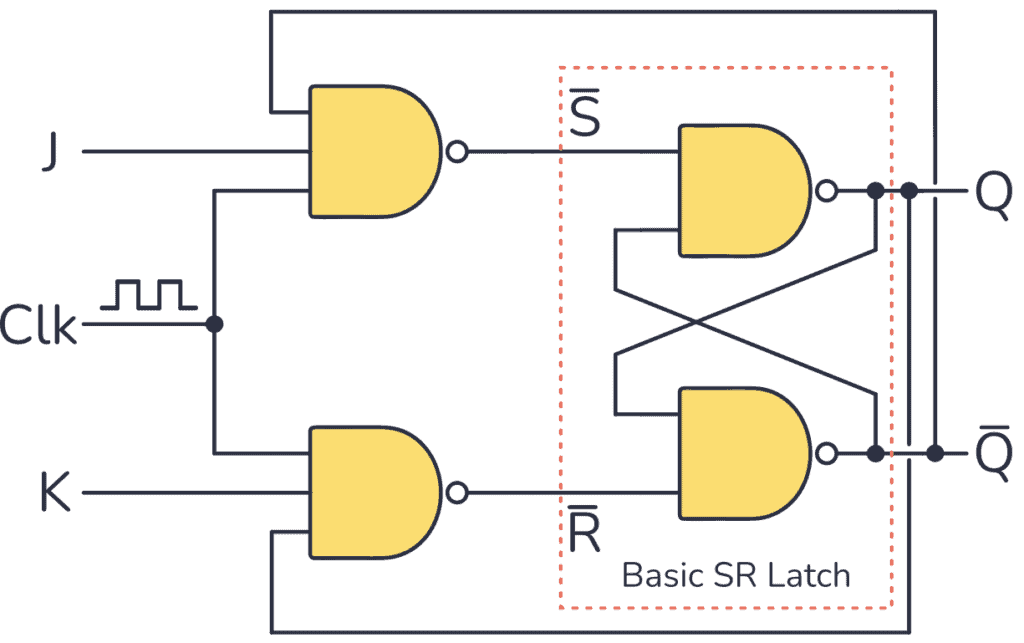

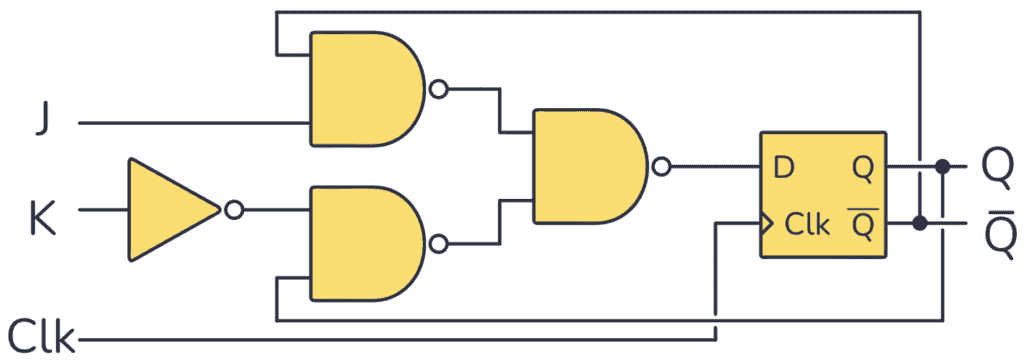

您可以在下面看到该电路的基本实现。它基于 S-R 锁存器,采用 NAND 门构建:

JK触发器基本电路

JK触发器基本电路

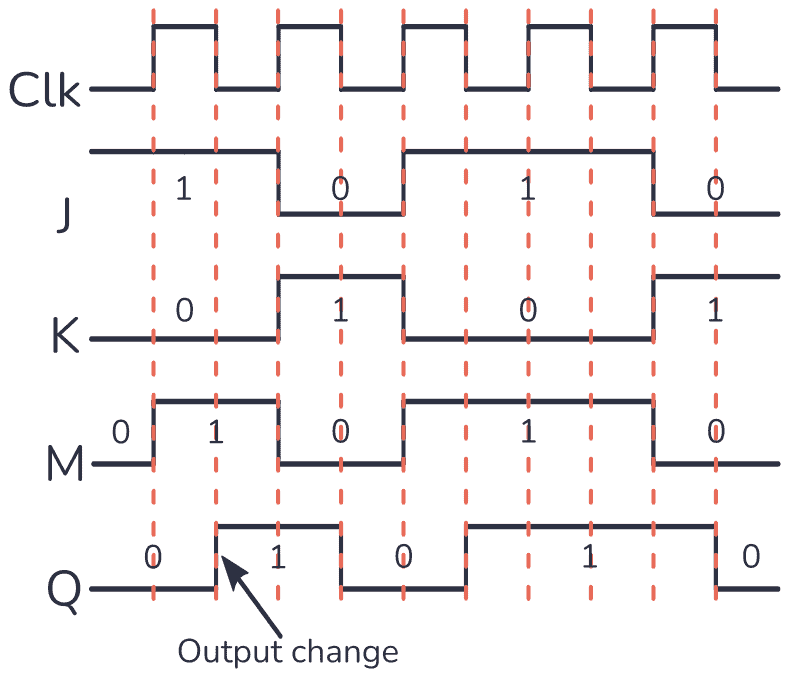

JK 触发器的 J 和 K 输入可用于设置、复位或切换输出,如下所示:

J=1 和 K=0 将输出设置为 1

J=0 和 K=1 将输出复位为 0

J=1 和 K=1 切换输出

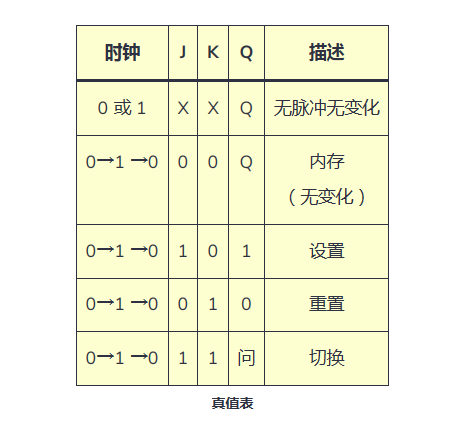

但要使触发器进行任何更改,其时钟输入必须为 1。查看下面的真值表:

时钟JKQ描述

0XXQClk in 0 Q 无

变化

100Q内存

(无变化)

1101设置

1010重置

111问切换

JK 触发器真值表

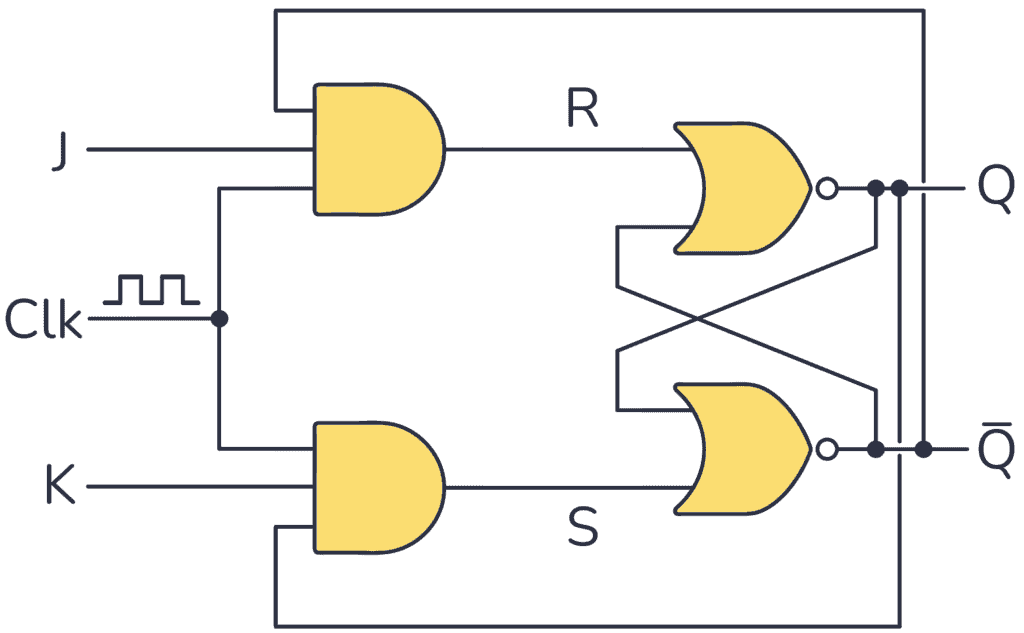

实现基本JK触发器电路的另一种方法是使用两个AND门和两个NOR门,如下所示(它的工作原理与使用NAND门构建的完全相同):

赛车问题

原则上,上述基本实现有效,但会出现时序问题。当时钟为“1”并且您想切换输出时,它将在“1”和“0”之间快速切换,直到时钟回到“0”。此问题称为争用条件。

您可以通过使触发器脉冲触发或边缘触发来解决此问题。

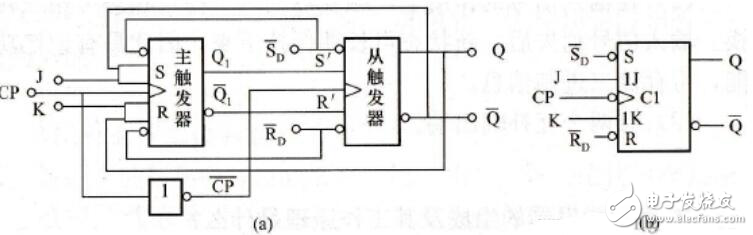

脉冲触发 JK 触发器

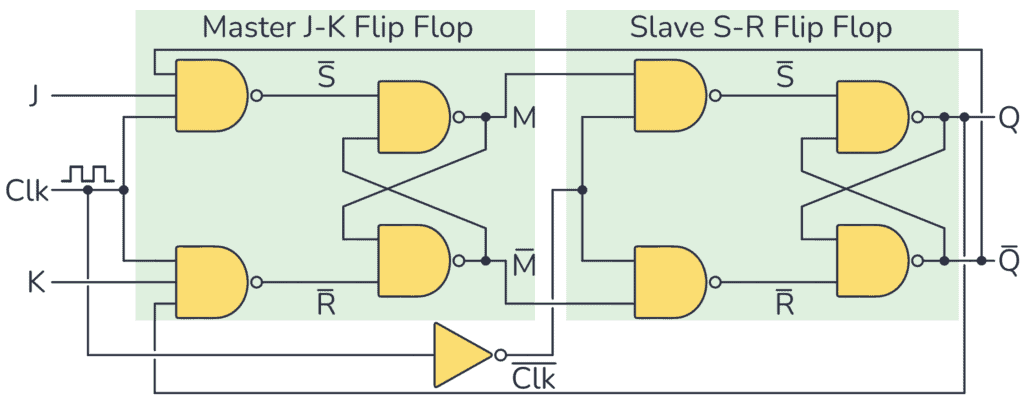

下面是一个基于主从原理的脉冲触发 JK 触发器:

主从电路

主从电路

如您所见,要构建此配置,您需要一个基本的 JK 触发器电路,该电路与 S-R 触发器连接在一起。

要了解此版本的工作原理,请查看下面的时序图:

一旦时钟产生上升沿 ↑,即从 0 到 1 (0→1

的变化),它就会触发主部分。因此,此部分中输出的值会更改。这些信号连接到从部分,但这不会在上升沿触发,因为时钟已经反转。

一旦时钟信号产生下降沿↓,从1变为0(1→0),就会触发从机部分,使Q输出反映主机的输出值。

因此,该电路需要一个完整的脉冲(0→1→0)才能改变输出。这就是为什么这种配置被称为脉冲触发的JK触发器。

边缘触发 JK 触发器

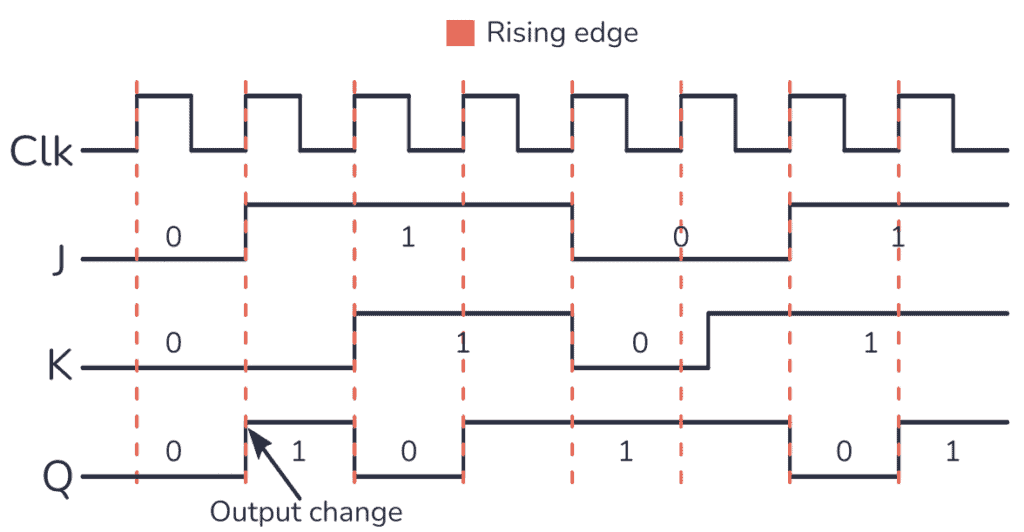

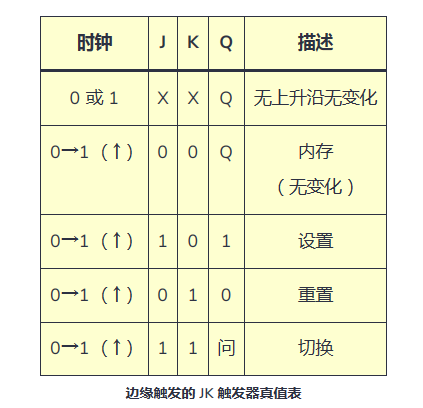

与需要完整脉冲的主从设计不同,您还可以构建从上升沿 ↑ 或下降沿 ↓ 触发的边沿触发设计。

下面是在上升沿触发的时序图:

上图显示了该电路如何只需要Clk输入上的上升沿来改变输出Q的状态。它只会在上升沿发生变化。

要构建仅由上升沿信号触发的 JK 触发器,您可以使用上升沿触发的 D 触发器、NOT 门和 NAND 门,如下所示:

边缘触发 JK 触发器电路

-

真值表

+关注

关注

0文章

25浏览量

15192 -

触发器

+关注

关注

14文章

1997浏览量

61095

发布评论请先 登录

相关推荐

R-S触发器真值表 R-S触发器工作原理及逻辑功能

JK触发器基本教程,讲的超详细!!

jk触发器是什么原理_jk触发器特性表和状态转换图

JK触发器的工作原理及真值表

JK触发器的工作原理及真值表

评论