在时序电路设计中,建立时间/保持时间可以说是出现频率最高的几个词之一了,人们对其定义已经耳熟能详,对涉及其的计算(比如检查时序是否正确,计算最大频率等)网上也有很多。但抛开这些表面,建立时间/保持时间到底是如何产生的,了解的人却不是很多。本篇文章就透过现象看本质,打开触发器的“黑盒子”,来了解一下到底什么是建立时间/保持时间。

01

先来看一下建立时间/保持时间的定义:

建立时间(setup time):触发器的时钟信号上升沿到来以前,数据需要保持稳定的时间。

保持时间(hold time):触发器的时钟信号上升沿到来之后,数据需要保持稳定的时间。

值得注意的是,建立/保持时间的概念是针对触发器的特性来说的。但是不仅触发器有建立/保持时间,锁存器也有,而且触发器的建立/保持时间还是基于锁存器的特性得来的。为此,先来了解一下锁存器。

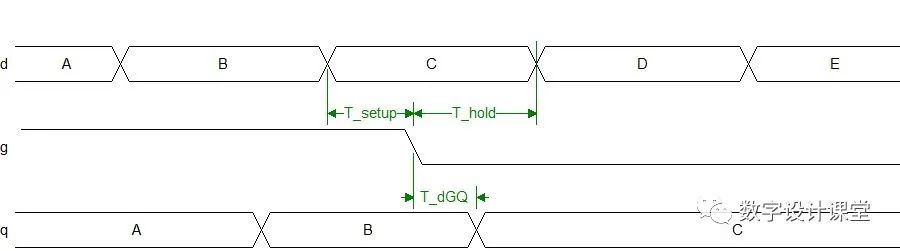

图1 锁存器的符号表示

典型的锁存器如图1所示,包括三个端口:数据输入端D,使能输入端G和数据输出端Q。当使能端为高电平时,输出Q随输入D变化;当使能端为低电平时,输出保持不变。锁存器的时序如图2所示。

图2 锁存器的时序特性

在使能端由高电平向低电平变化过程中,为了使锁存器正确锁存住数据,需要对输入数据的时间加以约束,因此便有了锁存器的建立时间和保持时间,即图2中的T_setup 和T_hold 。锁存器的这两个时序特性定义跟触发器很相似,不同的是在锁存器上这两个时序约束条件发生在使能端由高电平向低电平转化时。图2中的T_dGQ为使能端到输出端的延时。

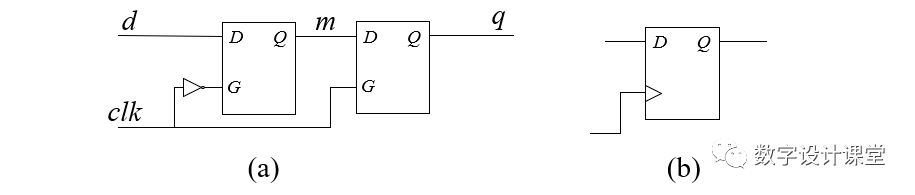

锁存器在使能信号为高电平时相当于透明,而如何组合锁存器,使其变成只在使能信号边沿锁存数据的触发器呢?答案是两个锁存器串联。如图3(a)所示,串联的前一个锁存器使能端为低电平触发(即反向使能),称为主锁存器,后一个锁存器称为从锁存器。在clk为低电平时,使能主锁存器,主锁存器的输出信号m随输入d变化,此时因为从锁存器未被使能,所以输出信号q无变化;在clk从低电平变为高电平时,m采样输入信号d并且保持,与此同时从锁存器打开,输出端输出被主锁存器锁存的信号值。触发器的符号表示如图3(b)。

图3 (a)两个锁存器组成的触发器 (b)触发器符号表示

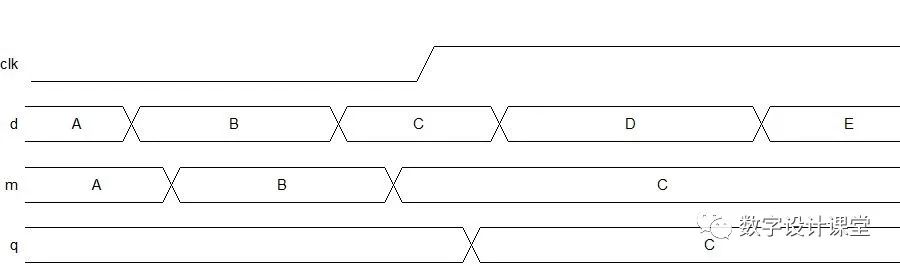

为了进一步了解主从锁存器的工作原理,示例的波形图如图4所示。可以看到,当clk为低时,m跟随d变化;当clk由低变高,主锁存器锁存输入值,中间m停止变化,此时从锁存器打开,经过一段延迟后将中间信号送至输出。

图4 两个锁存器组成的触发器时序波形

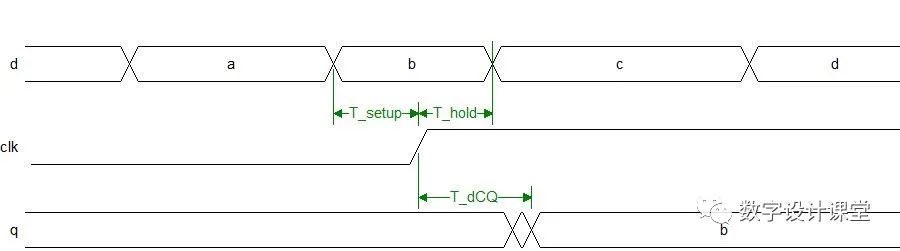

为了不引起混淆,图4在重画的波形图上给出触发器的时序特性表示。其中T_dCQ为触发器从clk端到Q端的延迟。需要注意的是,在clk上升后到Q端稳定以前,Q端可能会变化多次,T_dCQ 则是取从clk变化到稳定输出之间的延迟。

图5 触发器的时序特性表示

锁存器的时序特性和触发器的时序特性该如何对应呢?仔细一想就会得到答案:触发器的建立时间和保持时间其实就是主锁存器的建立时间和保持时间,而触发器的clk到q端的延迟T_dCQ就是从锁存器的延迟T_dGQ。

到这里我们已经打开了触发器的第一层“黑盒子”,但是建立时间和保持时间究竟是如何产生的呢?这就需要打开第二层“黑盒子”——触发器的门电路表示。

02

构成锁存器的电路多种多样,这里我们选择使用传输门和三态门构建的CMOS锁存器,电路如图6所示。

图6 锁存器电路

当G为高电平时,传输门Ug打开,信号从D端输入,经过Ug、U2、U4到达输出端Q,此时三态反相器为关闭状态;当G端变为低电平时,传输门关闭,U3打开,此时U2、U3构成双稳态器件将输入信号保持,输出端Q也稳定输出双稳态器件保持的信号。

现在来探讨锁存器的建立时间和保持时间。在G为高电平时,输入D变化后为了能输出正确的值,存储器——即双稳态器件必须存储到正确的输入值。这意味着要想使输出正确,在G下降前输入值必须经过U2。由此得出建立时间

T_setup = Tg + T2

其中Tg和T2分别为传输门和反相器U2的延迟。

当G变为低电平后,输入值需要在传输门关闭之前保持不变,否则输入值就会穿过传输门,从而无法锁存正确的值。传输门的关闭信号需要经过U1,所以得出保持时间

T_hold = T1

其中T1为反相器U1的延迟。

接下来算一下T_dGQ。G由高变低后,G的变化经过反相器U1到达传输门Ug,使传输门关闭,输入的信号再经过Ug、U2、U4到达输出端。所以

T_dGQ = T1 + Tg + T2 + T4

从输入端到输出端,信号经过了Ug、U2、U4,所以输入到输出的延迟

T_dDQ = Tg + T2 + T4

因为在触发器中T_dDQ意义不大,所以在此也不做过多赘述。

有了单个锁存器的基础,接下来进行触发器的探讨也会变得容易很多。

03

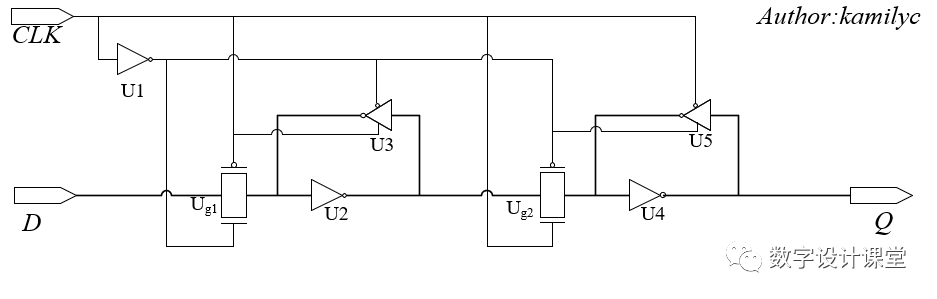

由第一段分析可知,触发器是由两个锁存器串联而组成的,由传输门和三态反相器构成的触发器如图7所示:

图7 触发器电路

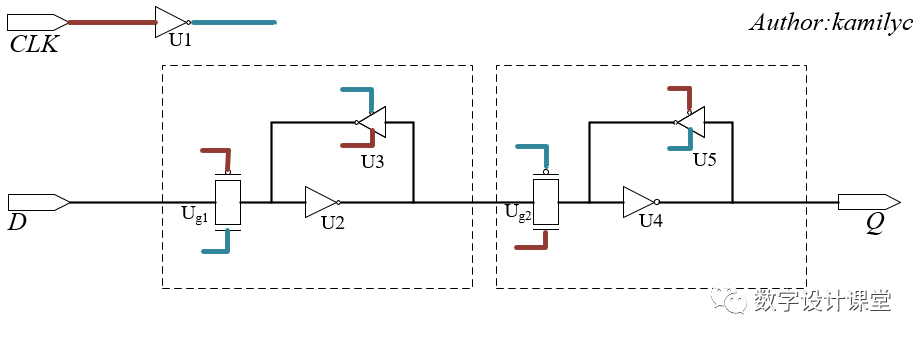

可以看到在触发器电路中,Ug1、U2、U3构成了主锁存器,Ug2、U4、U5构成了主锁存器。为了更直观的展示触发器的原理,将图7中的时钟信号用彩色的连线代替,得到图8:

图8 触发器的原理图的直观表示

在图8中,主锁存器和从锁存器分别用虚线框出,红色连线为clk信号,蓝色连线为经过反相器U1后的clk信号。

触发器的建立时间和保持时间与主锁存器的相同:

T_setup = Tg1 + T2

T_hold = T1

触发器的clk到Q端延迟则为从锁存器的延迟,分析方法与锁存器的分析方法相同:

T_dCQ = T1 + Tg2 + T4

-

反相器

+关注

关注

6文章

311浏览量

43294 -

时序电路

+关注

关注

1文章

114浏览量

21696 -

锁存器

+关注

关注

8文章

906浏览量

41497 -

门电路

+关注

关注

7文章

199浏览量

40160 -

触发器

+关注

关注

14文章

2000浏览量

61134

发布评论请先 登录

相关推荐

芯片设计进阶之路—从CMOS到建立时间和保持时间

FPGA时序分析-建立时间和保持时间裕量都是inf怎么解决呢?

建立时间和保持时间讨论

FPGA实战演练逻辑篇51:建立时间和保持时间

保持时间与建立时间

数字 IC 笔试面试必考点(9)建立时间以及保持时间 精选资料分享

为什么触发器要满足建立时间和保持时间

PCB传输线建立时间、保持时间、建立时间裕量和保持时间裕量

关于建立时间和保持时间的测量方法

到底什么是建立时间/保持时间?

到底什么是建立时间/保持时间?

评论