公众号:高速先生

作者:黄刚

大家可能已经习惯了高速先生善于解决各种高速信号和电源信号的疑难杂症,让很多从事EMC行业的粉丝们感觉格格不入。别急,今天就show一下我们在EMC方面的积累案例哈!

高速先生真的不只是专注于高速信号哈,其实我们也持续在研究EMC方面的理论,同时也积累了很多debug的案例和PCB设计经验,最近也收到很多粉丝要求,让我们分享一些EMC的设计案例,就今天,高速先生就给大家分享这么一个简单但是却很隐蔽的EMC设计问题。

案例来自一家和我们深度合作很多年的战略客户,我们在高速上合作比较的多,其实这个项目本身也是一个高速的项目,板上最高速的是25G的光模块信号链路。这个项目由我们的PCB工程师设计并进行仿真,当然仿真的是25G信号本身的通道性能,在确定仿真pass之后,设计工程师按照我们给出的建议去修改并制板加工和焊接,客户拿到完成的板卡之后首先进行25G光模块误码率的测试,测试发现没有问题,虽然我们的仿真是pass的,但是每一次客户真正调试成功我们才能放心。

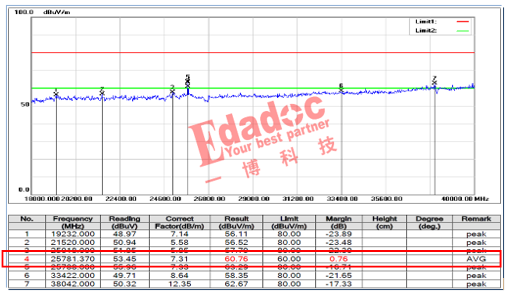

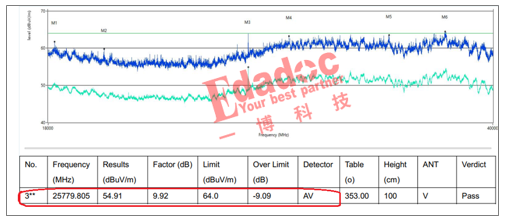

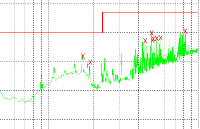

当我们认为又是一个对于高速先生很常规的仿真设计项目时,客户居然拿这块板去做了一个之前不需要做的测试,那就是EMC的辐射测试!而且更打击的是,在进行3M的远场测试时,发现在25G的频点辐射还稍有超标,要求是60dBuV/m,我们测试多了一丢丢,测试项为FCC part15 Class A,测试结果是下面这样的:

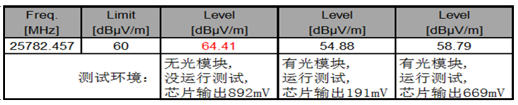

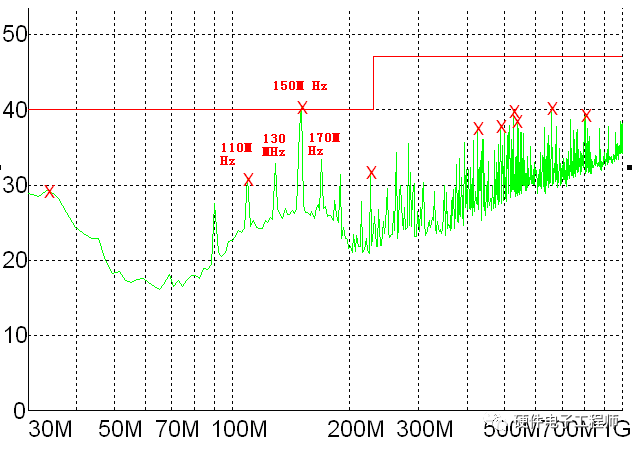

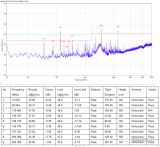

在25G的频点辐射超标,目标肯定直接指向了光模块的设计上,我们知道辐射的能量正相关于光模块的输出幅度,因此我们为了更好的判断光模块输出对辐射指标的影响,我们建议客户调节下FPGA的输出幅度(当前结果是输出幅度为892mV情况下测试),看看光模块的接收幅度变化对辐射的影响,按照我们的建议,客户进行了测试,列表如下:

通过测试结果传递给我们两个重要的信息:

1、的确是光模块链路导致的辐射影响;

2、降低FPGA输出幅度会减小辐射噪声,并成功通过EMC测试指标;

3、但是降低FPGA幅度可能会对信号质量产生影响。

当我们明确了光模块导致的影响后,那我们就看看PCB设计上还有什么可以优化的点,我们打开PCB文件,聚焦到该光模块区域的设计里面,发现了很重要的一个点:

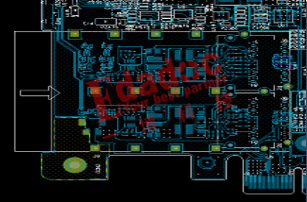

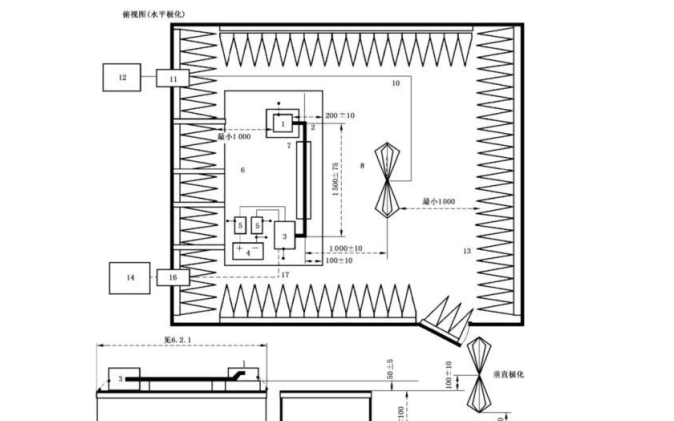

在TOP层,也就是光模块的焊接层,我们的机壳地是很好的连接起来的,如下所示:

于是我们再看看针脚那边的BOTTOM层,发现机壳地并没有接上,而是铺的是常规的数字地,高速先生咨询了设计工程师,他表示铺数字地可以更好的屏蔽板内的光模块信号,提供隔绝串扰和回流的作用,没有往EMC辐射这方面进行更多的权衡。高速先生评估之后,认为这个地方的铺数字地对信号的串扰和回流本身其实帮助不大,因为走线没有参考到这一层,相反接上机壳地的话,是更有可能对辐射的屏蔽产生正面的作用,因为光模块的外壳和针脚都连接到BOTTOM层的位置去了。

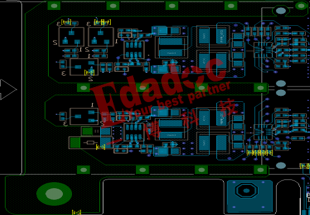

于是我们和客户商量之后,决定快速的再加工一版验证下,包括高速信号本身的大部分设计都不做改动,只是把BOTTOM这个机壳地像TOP层这样连接起来,如下所示:

很快板子重新完成了,客户再进行测试后给出了大家都满意的答案,在原有的FPGA输出幅度的情况下再进行EMC测试,成功将这个频点的辐射压低了, 满足了辐射的指标,而高速信号通道本身的测试也并没有问题,这下客户终于可以安心的结项了!

最后客户也很感慨的表示,在没测试辐射这个指标之前,还一直觉得机壳地的设计不会有那么重要的影响,通过这个案例后,看能不能对重视EMC辐射影响的粉丝们提供一些有意义的PCB设计思路哈!

审核编辑:汤梓红

-

辐射

+关注

关注

1文章

598浏览量

36339 -

emc

+关注

关注

170文章

3921浏览量

183154 -

光模块

+关注

关注

77文章

1266浏览量

59005 -

机壳地

+关注

关注

0文章

3浏览量

7530

发布评论请先 登录

相关推荐

某产品EMC辐射骚扰测试超标案例分析

HDMI辐射超标如何整改

【EMC家园】产品EMC辐射发射超标原因有哪些?

EMC辐射超标,内部时钟频率超标怎么解决?

造成EMC辐射超标原因有哪些(精彩案例分析)

3225贴片晶振EMC辐射超标工作建议和分析

某单板TVS接地不当造成辐射骚扰超标问题分析

时钟辐射超标怎么解决?

EMC整改如何解决时钟辐射超标问题

EMC辐射超标案例分析

EMC辐射超标案例分析

评论