摘要

半导体产业热门趋势-高速运算(HPC)市场在全球加速成长,进一步推动广泛应用如5G、云端数据中心、人工智能、行动运算、自驾车的发展。随着先进制程持续开发,对于设计产品要求高运算、低延迟、低耗能等市场需求驱动下,进而推动着高速存取界面应用、规范,以及先进制程的演变。生产成本提高与高速接口带宽速度增加,大幅增加了高速接口硅智财与SoC整合风险与难度。在芯片厂投入专业分工人力和EDA工具成本大幅提升,使先进制程高速接口IP整合硬核实做需求日益增加。

多样性高速接口应用规格与先进制程

随着电子装置处理器芯片运算效能提高,进一步带动高速传输数据的需求。而高速存取、视觉监控接口有多样的应用规格,如SATA、USB、PCIe MIPI等,就如同不同交通运输方式,芯片设计厂商往往会根据自身产品的应用,锁定几种类型的传输威廉希尔官方网站 规格。因此,唯有持续精进,才能于每一代威廉希尔官方网站 规格出现转换时,领先抢下市场商机。

现今庞大实时的高速运算下,对于低延迟、低功耗的极致追求,推进先进制程如FinFET等芯片制造,而在芯片实作先进制程过程中,除了专业人才培养,购买不同EDA工具、封装与测试等皆是必须的投资,这将导致整体生产成本大幅度提升,增加芯片厂商进入高速运算市场的困难度和风险。

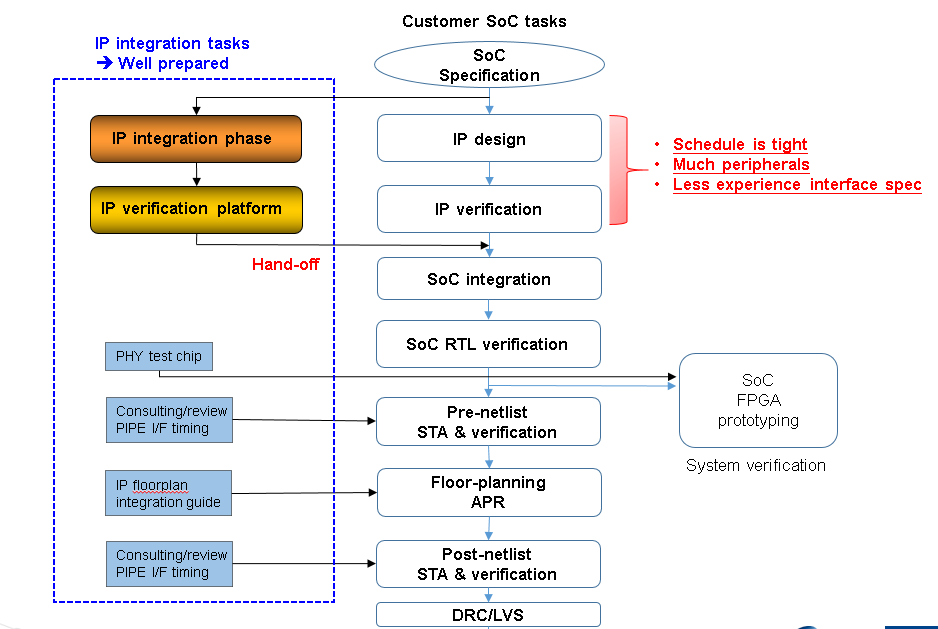

在芯片设计流程中,从本身产品的规格,到各个IP设计验证,乃至整体芯片的整合实做都须遵守着市场的关键准则- Time to Market。在庞大的时程压力之下,加上对于高速接口专业领域的不熟悉,如何在短时间内了解不同规格的高速传输存取接口,以及逐步完成由IP level、Sub-system level到Whole chip level的验证,并在竞争激烈的市场中胜出,无疑考验着每位工程师以及公司是否可承担风险。

高度整合专业分工

在SoC芯片中许多的高速传输存取接口中都会包括了物理层(PHY)以及控制处理器(Controller)。不同的高速接口规格都代表着不同的专业领域,对于高速传输接口专业领域不熟悉的情况之下,短时间完成快速且完整的验证,整合与实做皆会面临高度的风险。

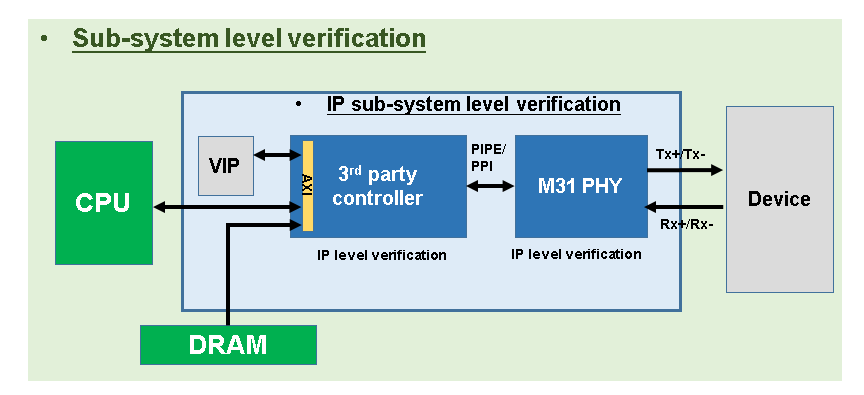

M31在40奈米、28奈米、22奈米与FinFET制程上皆已完成PCIe、MIPI、 USB等高速接口IP的设计开发及验证,并搭配不同接口的控制处理器与次系统(Sub-system)的验证方法(图1)来实现高速接口整合一站式服务(图2)。此服务协助客户能透过AMBA架构将次系统快速、简单的整合进入SoC,并降低风险,使客户可专注于芯片设计差异化与系统层次的整合,让客户的IC产品在效能和成本表现上更具市场竞争优势。

图1. Sub-system level verification

图2. IP Integration Service

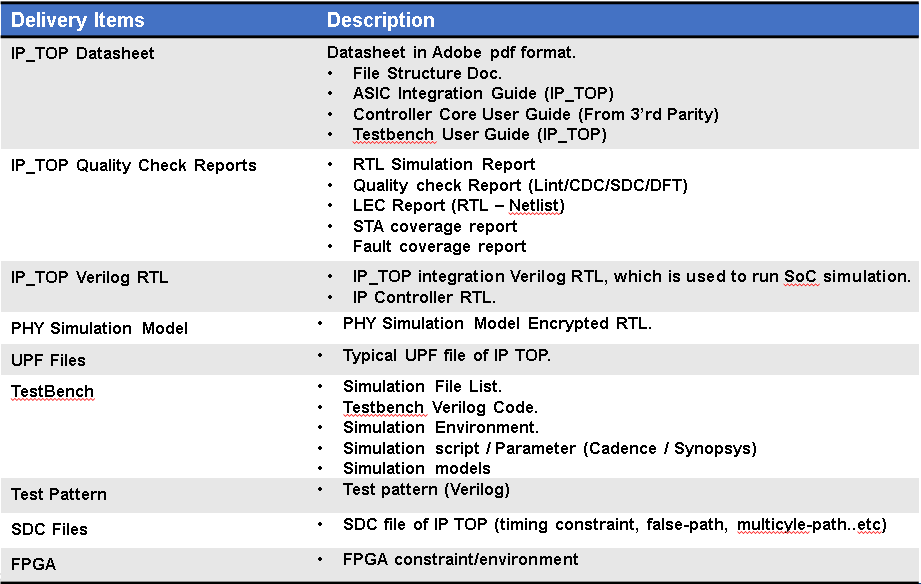

对于SoC设计者来说,IP视为一个黑盒子(Block box),要达到花费最少人力成本,并同时达到最佳效果,必须要能提供相关的设计套件组合,将该标准的系统接口完成整合。

M31提供完整设计套件组合,包含物理层仿真模块(Behavior model)、控制器本体、整合IPinterwetten与威廉的赔率体系 环境、实作合成约束文件(Constraint file)及EDA软件签核数据交付标准(Sign-off、Data-in)的质量分析报告,进一步替客户把关,帮助客户减少与原本SoC产生不兼容的问题。

表1. M31设计套件组合

M31高速存取接口硅智财整合一站式服务

随着制程快速的演进,从传统的IDM公司主导芯片开发,至SoC多样化应用领域再到专业的硅智财分工,无不考验着芯片设计的流程和风险管控,M31除持续开发先进制程最新世代的IP产品,更进一步为客户提供整合硬核实做服务,让设计业者在高速运算暨存取界面讲求效能与功耗兼具的应用市场中,降低风险并达到最大的效益,抢得市场利基。

-

IP

+关注

关注

5文章

1706浏览量

149535 -

SoC芯片

+关注

关注

1文章

611浏览量

34914 -

高速接口

+关注

关注

1文章

44浏览量

14774 -

IC芯片设计

+关注

关注

0文章

7浏览量

1085

发布评论请先 登录

相关推荐

拱墅区智慧照明产业质量基础设施“一站式” 服务平台于罗莱迪思正式设立

M31亮相北美设计自动化会议 展示先进制程IP解决方案

M31谈 高速存取接口硅智财整合一站式服务

M31谈 高速存取接口硅智财整合一站式服务

评论