1.eFlexPWM 介绍

2.PWM GPIO 口配置

3.eFlexPWM 配置(PWM 配置)

4.eFlexPWM 配置(死区 配置)

5.eFlexPWM 配置代码

6.开发板测试与波形

7.参考文档

1. eFlexPWM 介绍

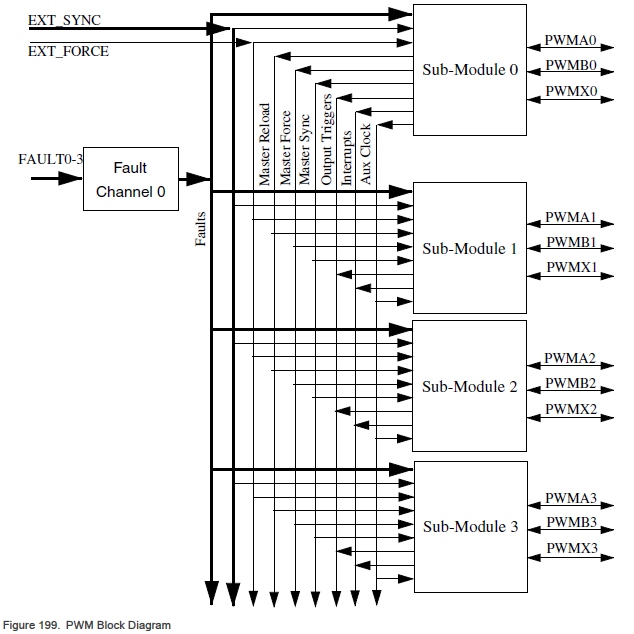

eFlexPWM 是 LPC553X 的一个高级 Timer 外设,针对电机应用和电源应用做了优化,并能够产生各种不同的 PWM 类型,PWM 输出功能主要有中心对齐(Center Aligned)、边缘对齐(Edge Aligned)、相移(Phase Shifted)、双开关(Double Switching)功能。

增强的输入捕获功能(Enhanced Capture),可以精确测量 PWM 频率和占空比。

一个 eFlexPWM 中还有 4 个子模块,4 个子模块之间具有同步开关功能,事件产生时同时动作,消除了中断和软件操作上的延时,特别适合于电机的换相操作。

eFlexPWM 还可以在精确的时刻触发 ADC 进行采样,在电机相电流采样中特别方便。

此外还有 counter 不同的重载逻辑,多样的寄存器 Buffer 更新时机,PWM 互补和死区自动生成等功能,本文主要讲解如何生成 6 路互补带死区的 PWM 以应用于电机控制,这些 PWM 通过 PreDriver 后驱动 MOS 或 IGBT,下图是 eFlexPWM 框图。

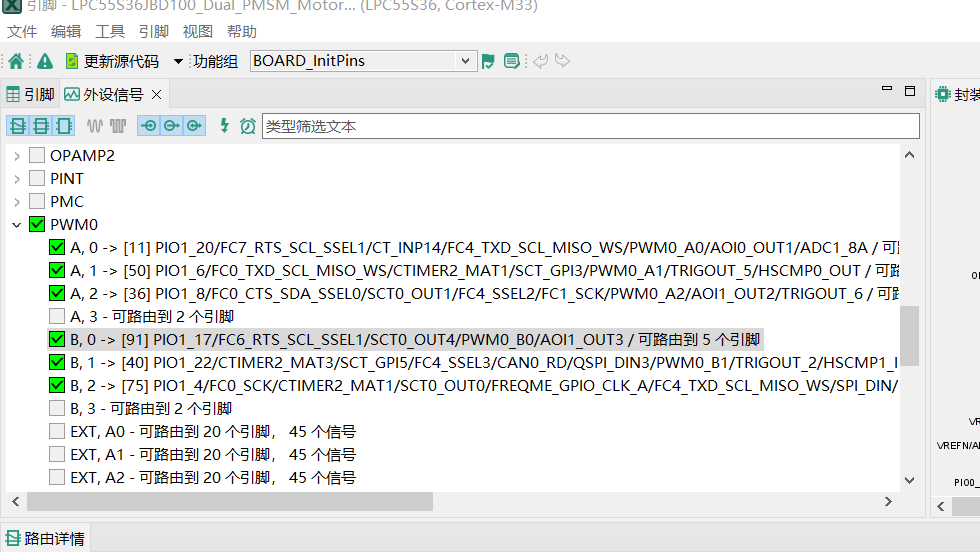

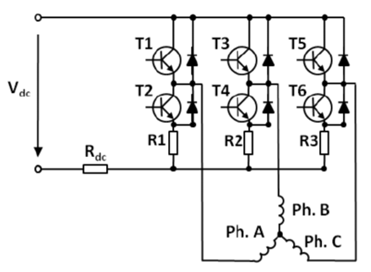

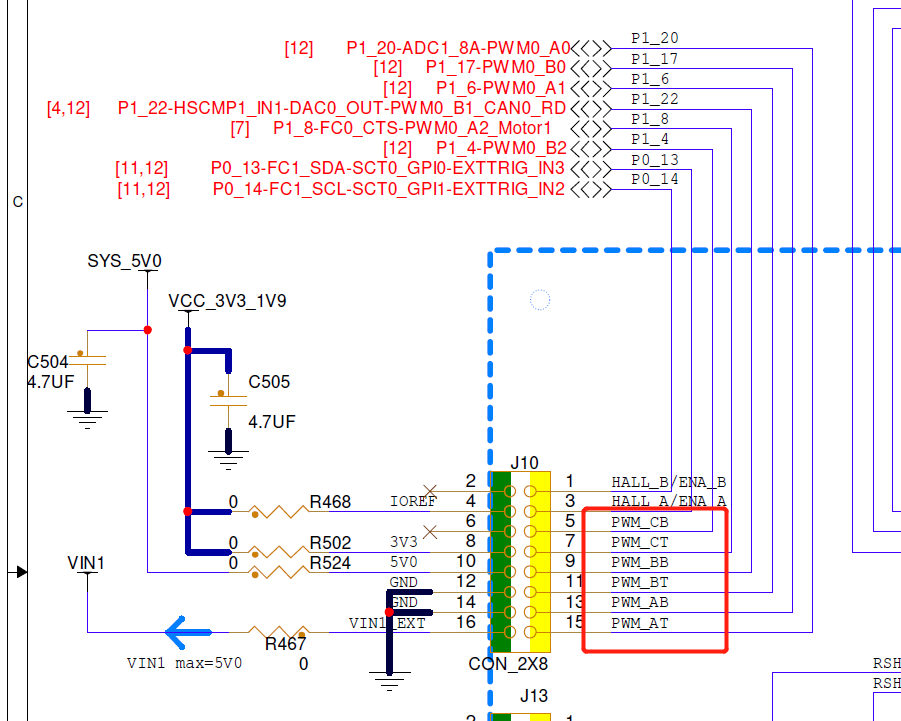

2. PWM GPIO 口配置

GPIO 口的初始化和分配使用 MCUXpresso config Tools 来配置,可以减少错误和冲突,配置完后将自动生成的 pin_mux.c 和 pin_mux.h 拷贝到工程中并在 main 中执行 BOARD_InitBootPins() 函数即可,图中的 A,0 和 B,0 为互补到死区的一对 PWM,将分别接到 Predriver 后驱动图中 MOS 管的 T1 和 T2 信号,其他依次类推。

3. eFlexPWM 配置(频率配置)

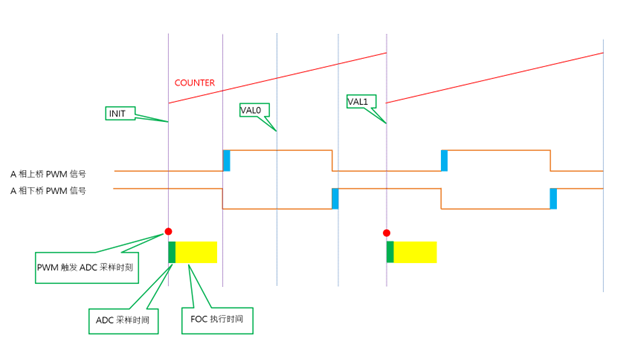

PWM 频率的配置主要通过配置 eFlexPWM 的 INIT 和 VAL1 寄存器配置,counter 从 INIT 开始计数,计到 VAL1 时重新计数,如果要产生 20KHz 的 PWM,计算过程为:INIT = 定时器时钟/20KHz/2 = 150MHz/20KHz/2 = 3750,VAL1 =定时器时钟/20KHz/2 -1 = 3749。部分代码:

/* value register initial values, duty cycle 50% */

PWMBase->SM[0].INIT = PWM_INIT_INIT((uint16_t)(-(M1_PWM_MODULO / 2)));//1875

PWMBase->SM[1].INIT = PWM_INIT_INIT((uint16_t)(-(M1_PWM_MODULO / 2)));

PWMBase->SM[2].INIT = PWM_INIT_INIT((uint16_t)(-(M1_PWM_MODULO / 2)));

PWMBase->SM[3].INIT = PWM_INIT_INIT((uint16_t)(-(M1_PWM_MODULO / 2)));

PWMBase->SM[0].VAL1 = PWM_VAL1_VAL1((uint16_t)((M1_PWM_MODULO / 2) - 1));

PWMBase->SM[1].VAL1 = PWM_VAL1_VAL1((uint16_t)((M1_PWM_MODULO / 2) - 1));

PWMBase->SM[2].VAL1 = PWM_VAL1_VAL1((uint16_t)((M1_PWM_MODULO / 2) - 1));

PWMBase->SM[3].VAL1 = PWM_VAL1_VAL1((uint16_t)((M1_PWM_MODULO / 2) - 1));

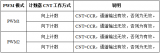

4. eFlexPWM 配置(死区配置)

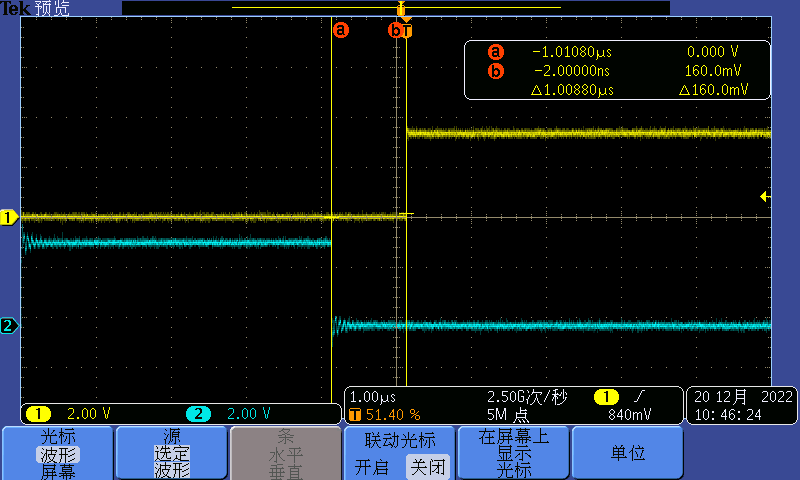

为了防止上下桥同时开通造成短路,可以根据 MOS 或 IGBT 的开关速度设置合适的死区时间,通过 DTCNT0 寄存器设置,计算方式如下, M1_PWM_DEADTIME 单位为 us,其位置为上图中的蓝色部分,部分代码:

PWMBase->SM[0].DTCNT0 = ((M1_PWM_DEADTIME * (MCU_CLOCK_FREQ / 1000000U)) / 1000U);

5. eFlexPWM 配置代码

eFlexPWM 的配置主要是开启时钟、复位、设置 INIT、VAL1 确定频率、死区、模式、占空比设置寄存器 VAL2、VAL3,以下代码为基于寄存器方式的完整配置代码:

void eFlexPWM0_init(void)

{

PWM_Type *PWMBase = (PWM_Type *)PWM0;

/*eFlexPWM0 init*/

SYSCON->PWM0SUBCTL = (SYSCON_PWM0SUBCTL_CLK0_EN_MASK | SYSCON_PWM0SUBCTL_CLK1_EN_MASK | SYSCON_PWM0SUBCTL_CLK2_EN_MASK | SYSCON_PWM0SUBCTL_CLK3_EN_MASK); //Enable Sub-module0 clock

CLOCK_EnableClock(kCLOCK_Pwm0);

/* value register initial values, duty cycle 50% */

PWMBase->SM[0].INIT = PWM_INIT_INIT((uint16_t)(-(M1_PWM_MODULO / 2)));//1875

PWMBase->SM[1].INIT = PWM_INIT_INIT((uint16_t)(-(M1_PWM_MODULO / 2)));

PWMBase->SM[2].INIT = PWM_INIT_INIT((uint16_t)(-(M1_PWM_MODULO / 2)));

PWMBase->SM[3].INIT = PWM_INIT_INIT((uint16_t)(-(M1_PWM_MODULO / 2)));

PWMBase->SM[0].VAL1 = PWM_VAL1_VAL1((uint16_t)((M1_PWM_MODULO / 2) - 1));

PWMBase->SM[1].VAL1 = PWM_VAL1_VAL1((uint16_t)((M1_PWM_MODULO / 2) - 1));

PWMBase->SM[2].VAL1 = PWM_VAL1_VAL1((uint16_t)((M1_PWM_MODULO / 2) - 1));

PWMBase->SM[3].VAL1 = PWM_VAL1_VAL1((uint16_t)((M1_PWM_MODULO / 2) - 1));

// TODO - TEST, init to 0 otherwise (see above).

PWMBase->SM[0].VAL2 = (uint16_t)(-(M1_PWM_MODULO/4));

PWMBase->SM[1].VAL2 = (uint16_t)(-(M1_PWM_MODULO/4));

PWMBase->SM[2].VAL2 = (uint16_t)(-(M1_PWM_MODULO/4));

PWMBase->SM[3].VAL2 = (uint16_t)(-(M1_PWM_MODULO/4));

PWMBase->SM[0].VAL3 = (uint16_t)((M1_PWM_MODULO/4));

PWMBase->SM[1].VAL3 = (uint16_t)((M1_PWM_MODULO/4));

PWMBase->SM[2].VAL3 = (uint16_t)((M1_PWM_MODULO/4));

PWMBase->SM[3].VAL3 = (uint16_t)((M1_PWM_MODULO/4));

/* PWM0 module 0 trigger on VAL4 enabled for ADC synchronization */

PWMBase->SM[0].VAL4 = PWM_VAL4_VAL4((uint16_t)((-(M1_PWM_MODULO / 2))));

/*xx_xxx1b - PWM_OUT_TRIG0 will set when the counter value matches the VAL0 value */

PWMBase->SM[0].TCTRL |= PWM_TCTRL_OUT_TRIG_EN(0b010001);//PWAOT0 PWBOT1 TRGFRQ OUT_TRIG_EN

PWMBase->SM[0].INTEN = (0x1UL << 12UL);//RIE,Reload Interrupt Enable

/* set deadtime (number of Fast Peripheral Clocks)

DTCNT0,1 = T_dead * f_fpc = 1.0us * 150MHz = 150 */

PWMBase->SM[0].DTCNT0 = ((M1_PWM_DEADTIME * (MCU_CLOCK_FREQ / 1000000U)) / 1000U);

PWMBase->SM[1].DTCNT0 = ((M1_PWM_DEADTIME * (MCU_CLOCK_FREQ / 1000000U)) / 1000U);

PWMBase->SM[2].DTCNT0 = ((M1_PWM_DEADTIME * (MCU_CLOCK_FREQ / 1000000U)) / 1000U);

PWMBase->SM[3].DTCNT0 = ((M1_PWM_DEADTIME * (MCU_CLOCK_FREQ / 1000000U)) / 1000U);

PWMBase->SM[0].DTCNT1 = ((M1_PWM_DEADTIME * (MCU_CLOCK_FREQ / 1000000U)) / 1000U);

PWMBase->SM[1].DTCNT1 = ((M1_PWM_DEADTIME * (MCU_CLOCK_FREQ / 1000000U)) / 1000U);

PWMBase->SM[2].DTCNT1 = ((M1_PWM_DEADTIME * (MCU_CLOCK_FREQ / 1000000U)) / 1000U);

PWMBase->SM[3].DTCNT1 = ((M1_PWM_DEADTIME * (MCU_CLOCK_FREQ / 1000000U)) / 1000U);

/* Control Register */

PWMBase->SM[0].CTRL = ( 0x0UL << 12UL ) //LDFQ

|( 0x0UL << 11UL ) //HALF

|( 0x1UL << 10UL ) //FULL

|( 0x0UL << 7UL ) //COMPMODE

|( 0x0UL << 4UL ) //PRSC

|( 0x0UL << 3UL ) //SPLIT

|( 0x0UL << 2UL ) //LDMOD,

|( 0x0UL << 1UL ) //DBLX

|( 0x0UL << 0UL ); //DBLEN

/* Control Register */

PWMBase->SM[1].CTRL = ( 0x0UL << 12UL ) //LDFQ

|( 0x0UL << 11UL ) //HALF

|( 0x1UL << 10UL ) //FULL

|( 0x0UL << 7UL ) //COMPMODE

|( 0x0UL << 4UL ) //PRSC

|( 0x0UL << 3UL ) //SPLIT

|( 0x0UL << 2UL ) //LDMOD,

|( 0x0UL << 1UL ) //DBLX

|( 0x0UL << 0UL ); //DBLEN

/* Control Register */

PWMBase->SM[2].CTRL = ( 0x0UL << 12UL ) //LDFQ

|( 0x0UL << 11UL ) //HALF

|( 0x1UL << 10UL ) //FULL

|( 0x0UL << 7UL ) //COMPMODE

|( 0x0UL << 4UL ) //PRSC

|( 0x0UL << 3UL ) //SPLIT

|( 0x0UL << 2UL ) //LDMOD,

|( 0x0UL << 1UL ) //DBLX

|( 0x0UL << 0UL ); //DBLEN

/* Control Register */

PWMBase->SM[3].CTRL = ( 0x0UL << 12UL ) //LDFQ

|( 0x0UL << 11UL ) //HALF

|( 0x1UL << 10UL ) //FULL

|( 0x0UL << 7UL ) //COMPMODE

|( 0x0UL << 4UL ) //PRSC

|( 0x0UL << 3UL ) //SPLIT

|( 0x0UL << 2UL ) //LDMOD,

|( 0x0UL << 1UL ) //DBLX

|( 0x0UL << 0UL ); //DBLEN

/* Fault0 trigger, Disable X,Disable B,Disable A */

// PWMBase->SM[0].DISMAP[0] = 0xF111U;

// PWMBase->SM[1].DISMAP[0] = 0xF111U;

// PWMBase->SM[2].DISMAP[0] = 0xF111U;

// PWMBase->SM[3].DISMAP[0] = 0xF111U;

PWMBase->SM[0].DISMAP[0] = 0;

PWMBase->SM[1].DISMAP[0] = 0;

PWMBase->SM[2].DISMAP[0] = 0;

PWMBase->SM[3].DISMAP[0] = 0;

/* PWMs are re-enabled at PWM full cycle / half cycle */

PWMBase->FSTS = (PWMBase->FSTS & ~(PWM_FSTS_FFULL_MASK | PWM_FSTS_FHALF_MASK)) | PWM_FSTS_FFULL(0x1) | PWM_FSTS_FHALF(0x1);

/* PWM fault filter - 3 Fast periph. clocks sample rate, 5 agreeing samples to activate */

PWMBase->FFILT = (PWMBase->FFILT & ~PWM_FFILT_FILT_PER_MASK) | PWM_FFILT_FILT_PER(2);

/* All interrupts disabled, safe manual fault clearing, inversed logic (trigger level = high) */

PWMBase->FCTRL &= ~(PWM_FCTRL_FLVL_MASK | PWM_FCTRL_FAUTO_MASK | PWM_FCTRL_FSAFE_MASK | PWM_FCTRL_FIE_MASK); /* clear FCTRL register prior further settings */

PWMBase->FCTRL |= PWM_FCTRL_FLVL(0x1U);

PWMBase->FCTRL |= PWM_FCTRL_FAUTO(0x1U);

PWMBase->FCTRL |= PWM_FCTRL_FSAFE(0x1U);

PWMBase->FCTRL |= PWM_FCTRL_FIE(0U); /* FAULT 0 & FAULT 1 - Interrupt disable */

/* Clear all fault flags */

PWMBase->FSTS = (PWMBase->FSTS & ~PWM_FSTS_FFLAG_MASK) | PWM_FSTS_FFLAG(0xF);

PWMBase->MASK = 0;//UPDATE_MASK MASKA MASKB MASKx

PWMBase->SWCOUT = 0;

PWMBase->DTSRCSEL = 0;//

PWMBase->SM[0].FRCTRL |= ((0UL << 4UL) | (0UL << 2UL) | (0UL << 1UL)) ;//FRAC45_EN 4,FRAC23_EN 2,FRAC1_EN1

PWMBase->SM[0].FRACVAL2 = 0 << 11UL;

PWMBase->SM[0].FRACVAL3 = 0 << 11UL;

PWMBase->SM[1].FRACVAL2 = 0 << 11UL;

PWMBase->SM[1].FRACVAL3 = 0 << 11UL;

PWMBase->SM[2].FRACVAL2 = 0 << 11UL;

PWMBase->SM[2].FRACVAL3 = 0 << 11UL;

PWMBase->SM[3].FRACVAL2 = 0 << 11UL;

PWMBase->SM[3].FRACVAL3 = 0 << 11UL;

PWMBase->SM[0].CTRL2 = ( 0x0UL << 15UL ) //DBGEN

|( 0x0UL << 14UL ) //WAITEN,Sleep Enable

|( 0x0UL << 13UL ) //INDEP,0b - PWM_A and PWM_B form a complementary PWM pair.

|( 0x0UL << 12UL ) //PWM23_INIT,

|( 0x0UL << 11UL ) //PWM45_INIT

|( 0x0UL << 10UL ) //PWMX_INIT

|( 0x0UL << 8UL ) //INIT_SEL,counter load init value,Local sync,Master reload,Master sync,EXT_SYNC

|( 0x0UL << 7UL ) //FRCEN

|( 0x0UL << 6UL ) //FORCE

|( 0x0UL << 3UL ) //FORCE_SEL,local force,master force,local reload,master reload,local sync,master sync,external force,external sync

|( 0x0UL << 2UL ) //RELOAD_SEL,0b - The local RELOAD signal

|( 0x0UL << 0UL ); //CLK_SEL,

//00b - The IPBus clock

//01b - EXT_CLK

//10b - Submodule 0’s clock (AUX_CLK)

PWMBase->SM[1].CTRL2 = ( 0x0UL << 15UL ) //DBGEN

|( 0x0UL << 14UL ) //WAITEN,Sleep Enable

|( 0x0UL << 13UL ) //INDEP,0b - PWM_A and PWM_B form a complementary PWM pair.

|( 0x0UL << 12UL ) //PWM23_INIT,

|( 0x0UL << 11UL ) //PWM45_INIT

|( 0x0UL << 10UL ) //PWMX_INIT

|( 0x2UL << 8UL ) //INIT_SEL,counter load init value,Local sync,Master reload,Master sync,EXT_SYNC

|( 0x0UL << 7UL ) //FRCEN

|( 0x0UL << 6UL ) //FORCE

|( 0x1UL << 3UL ) //FORCE_SEL,local force,master force,local reload,master reload,local sync,master sync,external force,external sync

|( 0x1UL << 2UL ) //RELOAD_SEL,1b - The master RELOAD signal

|( 0x0UL << 0UL ); //CLK_SEL,

//00b - The IPBus clock

//01b - EXT_CLK

//10b - Submodule 0’s clock (AUX_CLK)

PWMBase->SM[2].CTRL2 = ( 0x0UL << 15UL ) //DBGEN

|( 0x0UL << 14UL ) //WAITEN,Sleep Enable

|( 0x0UL << 13UL ) //INDEP,0b - PWM_A and PWM_B form a complementary PWM pair.

|( 0x0UL << 12UL ) //PWM23_INIT,

|( 0x0UL << 11UL ) //PWM45_INIT

|( 0x0UL << 10UL ) //PWMX_INIT

|( 0x2UL << 8UL ) //INIT_SEL,counter load init value,Local sync,Master reload,Master sync,EXT_SYNC

|( 0x0UL << 7UL ) //FRCEN

|( 0x0UL << 6UL ) //FORCE

|( 0x1UL << 3UL ) //FORCE_SEL,local force,master force,local reload,master reload,local sync,master sync,external force,external sync

|( 0x1UL << 2UL ) //RELOAD_SEL,1b - The master RELOAD signal

|( 0x0UL << 0UL ); //CLK_SEL,

//00b - The IPBus clock

//01b - EXT_CLK

//10b - Submodule 0’s clock (AUX_CLK)

PWMBase->SM[3].CTRL2 = ( 0x0UL << 15UL ) //DBGEN

|( 0x0UL << 14UL ) //WAITEN,Sleep Enable

|( 0x0UL << 13UL ) //INDEP,0b - PWM_A and PWM_B form a complementary PWM pair.

|( 0x0UL << 12UL ) //PWM23_INIT,

|( 0x0UL << 11UL ) //PWM45_INIT

|( 0x0UL << 10UL ) //PWMX_INIT

|( 0x2UL << 8UL ) //INIT_SEL,counter load init value,Local sync,Master reload,Master sync,EXT_SYNC

|( 0x0UL << 7UL ) //FRCEN

|( 0x0UL << 6UL ) //FORCE

|( 0x1UL << 3UL ) //FORCE_SEL,local force,master force,local reload,master reload,local sync,master sync,external force,external sync

|( 0x1UL << 2UL ) //RELOAD_SEL,1b - The master RELOAD signal

|( 0x0UL << 0UL ); //CLK_SEL,

//00b - The IPBus clock

//01b - EXT_CLK

//10b - Submodule 0’s clock (AUX_CLK)

/* Start PWMs (set load OK flags and run - we need to trigger the ADC) */

PWMBase->MCTRL = (PWMBase->MCTRL & ~PWM_MCTRL_CLDOK_MASK) | PWM_MCTRL_CLDOK(0xF);

PWMBase->MCTRL = (PWMBase->MCTRL & ~PWM_MCTRL_LDOK_MASK) | PWM_MCTRL_LDOK(0xF);

PWMBase->MCTRL = (PWMBase->MCTRL & ~PWM_MCTRL_RUN_MASK) | PWM_MCTRL_RUN(0xF);

//PWMBase->OUTEN = 0xFF0;//0xFF0,11-8,PWMA3_EN ~ PWMA0_EN, 7-4 PWMB3_EN ~ PWMB0_EN, 3-0 PWMX3_EN ~ PWMX0_EN

/* Enable & setup interrupt from PWMA */

NVIC_SetPriority(FLEXPWM0_RELOAD0_IRQn, 0U);

NVIC_EnableIRQ(FLEXPWM0_RELOAD0_IRQn);

}

6. 开发板测试与波形

本文使用 NXP 原厂的 LPC55S36-EVK 测试,生成的 6 路 PWM 对应原理图中的 PWM_AT、PWM_AB、 PWM_BT、PWM_BB、 PWM_CT、PWM_CB,如下图所示:

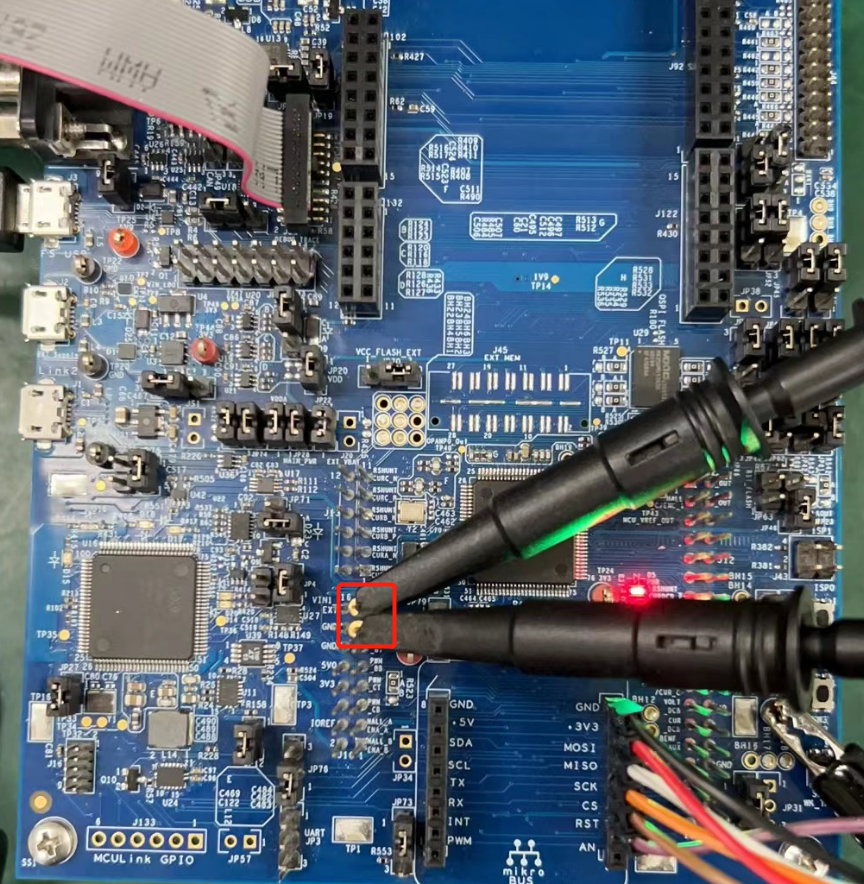

示波器探头连接开发板 J10 插件 15 与 13 脚,如下图中红框部分如图所示:

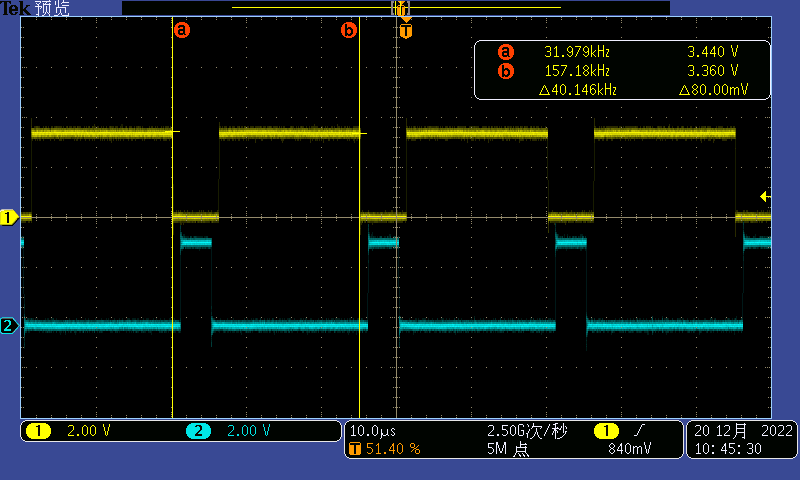

示波器黄色探头为 PWM_AT,蓝色为 PWM_AB,测量为 40KHz PWM,死区 1us,与设置的一致。

-

PWM

+关注

关注

114文章

5186浏览量

213953 -

电机

+关注

关注

142文章

9021浏览量

145501

发布评论请先 登录

相关推荐

PWM信号生成方法 PWM调制原理讲解

PWM死区的定义和作用

求助,关于编码盘与PWM的疑问求解

STM8S003 TIM1高级定时器输出互补带死区方波怎么解决?

采用STM32F030K6T6作互补PWM输出时,互补通道没有波形输出是为什么?

用STM32F051 TIM17产生两路带死区的互补pwm,互补pwm出来了,但死区没有,为什么?

带集成FET的3-V-6-V输入、6-A输出同步降压PWM切换器TPS5461x数据表

学威廉希尔官方网站

| 使用 LPC553X eFlexPWM 生成 6 路互补带死区 PWM

学威廉希尔官方网站

| 使用 LPC553X eFlexPWM 生成 6 路互补带死区 PWM

评论