先楫半导体的HPM6750集成2个RISC-V 处理器,主频高达816MHz。既然有两个CPU,岂可让它白白浪费?本文来带你一起尝试双核例程,体验双引擎带来的风驰电掣般的感觉。

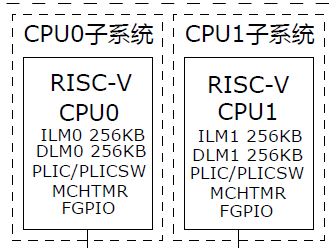

HPM6750双核采用主从结构,CPU0 和CPU1 采用相同配置:

●支持相同指令集

●相同容量的L1 指令和数据缓存

●相同容量的指令和数据本地存储器:256 KB ILM 和256 KB DLM

CPU0 和CPU1 采用相同的存储器映射,以下为例外:

● CPU 自身的指令/数据本地存储器ILM / DLM 为私有;

●FGPIO 为私有

●软件中断控制器PLICSW 为私有

●机器定时器MCHTMR 为私有

CPU0 和CPU1 采用相同的特权模式设置。

CPU0 为主CPU,CPU1 为从CPU,当复位发生时,系统总是由CPU0 启动,而CPU1 处于待机状态。需要时,由CPU0 装载CPU1 的程序镜像,之后释放CPU1,步骤如下:

1. CPU0 将CPU1 的代码镜像地址写入SYSCTL_CPU1_GPR0 寄存器

2. CPU0 将CPU1 启动代号写入SYSCTL_CPU1_GPR1 寄存器,代号为0xC1BEF1A9

3. CPU0 将SYSCTL_CPU1_LP [HALT] 位清0,即可释放CPU1

双核应用程序的开发步骤如下:

根据

“E:\sdk_env_v0.9.0\hpm_sdk\samples\multicore\hello”中README_zh.md文件如下:

多核示例工程在Core0上运行"hello word"示例,在core1上运行"rgb_led"示例。

在本工程中:

- 串口输出 "hello world"; 键盘手动输入字符串信息,通过串口打印出来

- RGB LED会在红、绿、蓝三色中依次切换

## 硬件设置

BOOT_PIN 应该设置为:0-OFF, 1-OFF

## 生成和编译多核工程

本示例中:core0示例在FLASH中原地执行, core1工程在ILM里执行。

用户必须先生成和编译__Core1__工程

用户必须在生成和编译完core1工程后再生成和编译__Core0__工程

### 生成core1工程

__CMAKE_BUILD_TYPE__ 必须是 下列选项中的一种:

- *"sec_core_img"*

- *"sec_core_img_release"*

若通过SDK env 包来生成工程,需要用 *"-t sec_core_img"*

### 生成core0工程

__CMAKE_BUILD_TYPE__ 无限制

## 运行现象

- 下载core0示例到设备并运行

- 下载core1示例到设备并运行

本文参照以上说明将在core0和core1中分别新建FreeRTOS相关程序,即在双核上各自运行RTOS。

新建Core1程序的SES工程

复制HPM 6750的SDK文件夹“sdk_env_v0.9\hpm_sdk\samples\rtos”下面的freertos_hello实例工程,复制到“sdk_env_v0.9.0\hpm_sdk\samples\multicore\hello\”并重新命名成“FreeRTOS_RISCV1”。

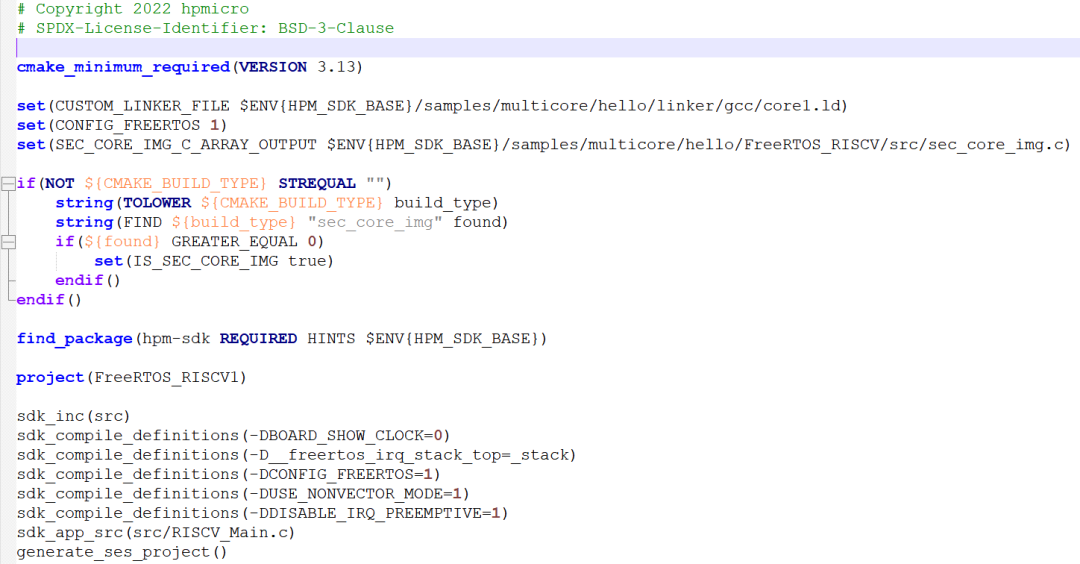

修改CMakeLists.txt文件中的配置,增加core1的链接文件,如下图所示:

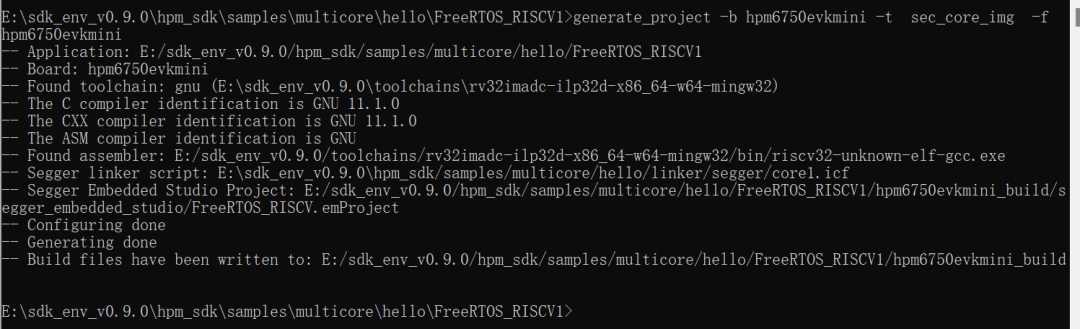

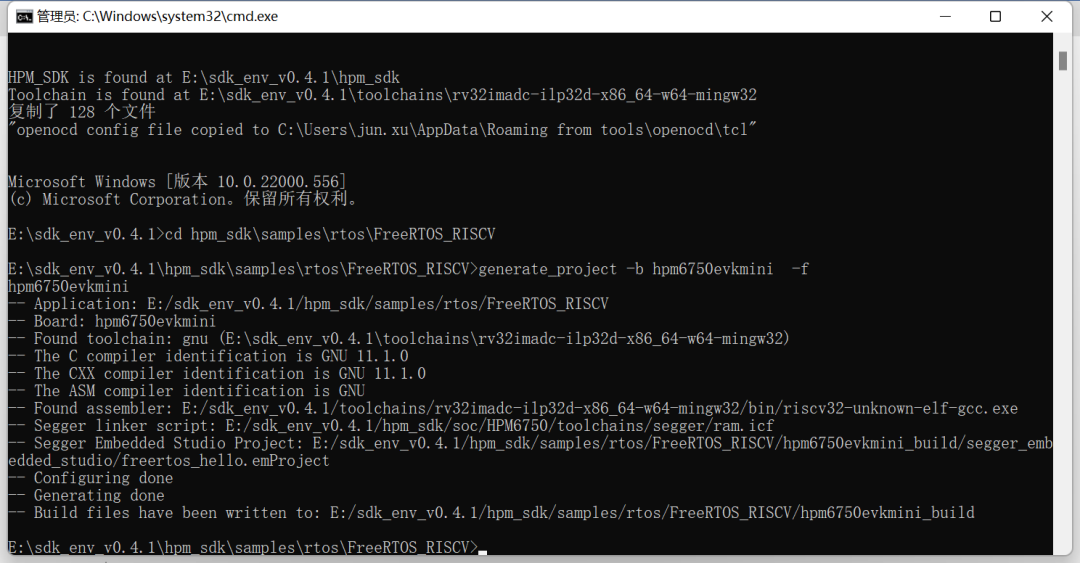

然后根据SDK 开发指南文档《HPM6750EVKMINI_UG》中的工程生成步骤,来生成segger embedded studio的工程文件。SDK env 包来生成工程,需要增加"-t sec_core_img"*

新建Core0程序的SES工程

复制HPM 6750的SDK文件夹“sdk_env_v0.9\hpm_sdk\samples\rtos”下面的freertos_hello实例工程,复制到“sdk_env_v0.9.0\hpm_sdk\samples\multicore\hello\”并重新命名成“FreeRTOS_RISCV”。

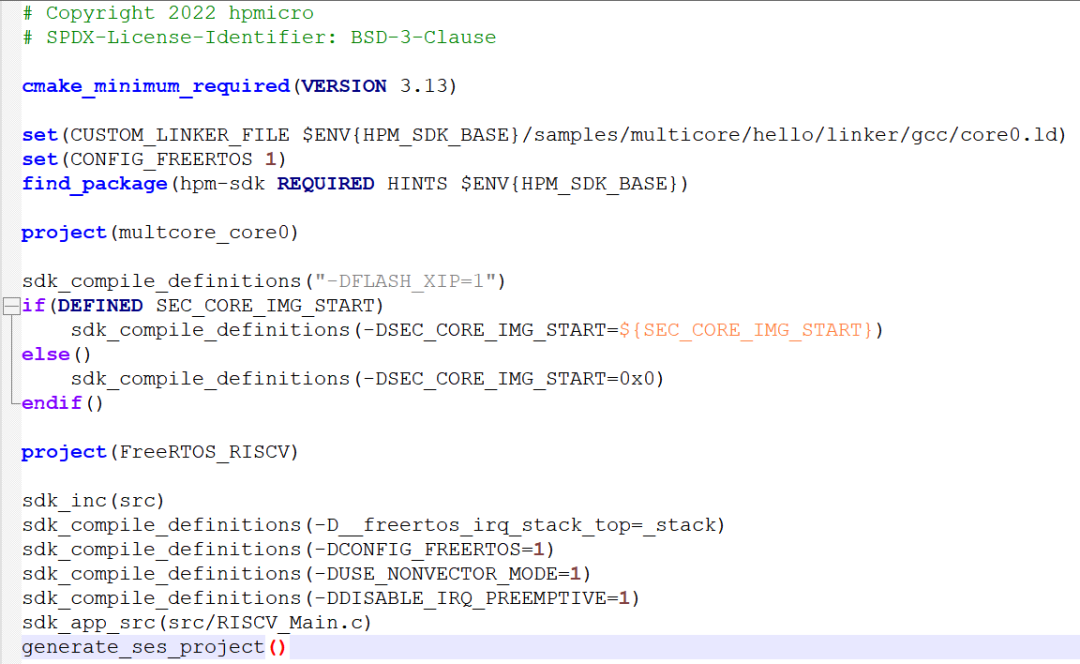

修改CMakeLists.txt文件中的配置,增加core0的链接文件,如下图所示:

然后根据SDK 开发指南文档《HPM6750EVKMINI_UG》中的工程生成步骤,来生成segger embedded studio的工程文件。

编译Core1程序的SES工程

因为core0程序中依赖core1工程编译并转换的源文件,因此,在编译core0程序前,必须先将core1工程编译好。

SDK会生成工程文件FreeRTOS_RISCV在FreeRTOS_RISCV\hpm6750evkmini_build\segger_embedded_studio文件路径下面,通过双击该文件可以直接进入SES(segger embedded studio),并打开该工程,然后编译。

在core1的工程编译完成会生成文件“sec_core_img.c”,并被自动拷贝到core0的工程路径FreeRTOS_RISCV/src/。在core1的FreeRTOS例程中主要完成RGBLED的依次点亮运行。

编译Core0程序的SES工程

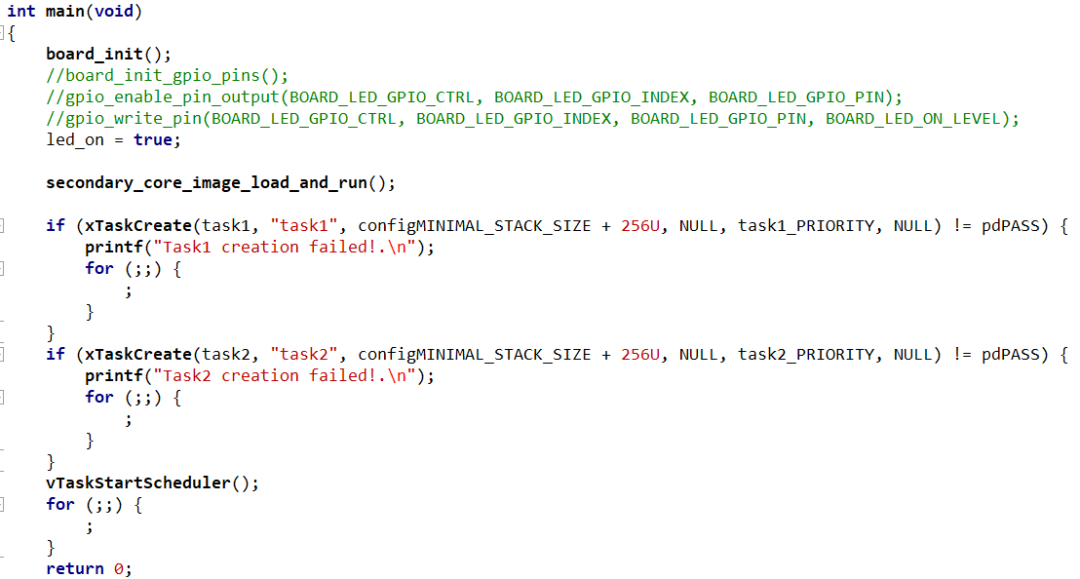

在core0的FreeRTOS例程中主要完成RTOS多任务运行。

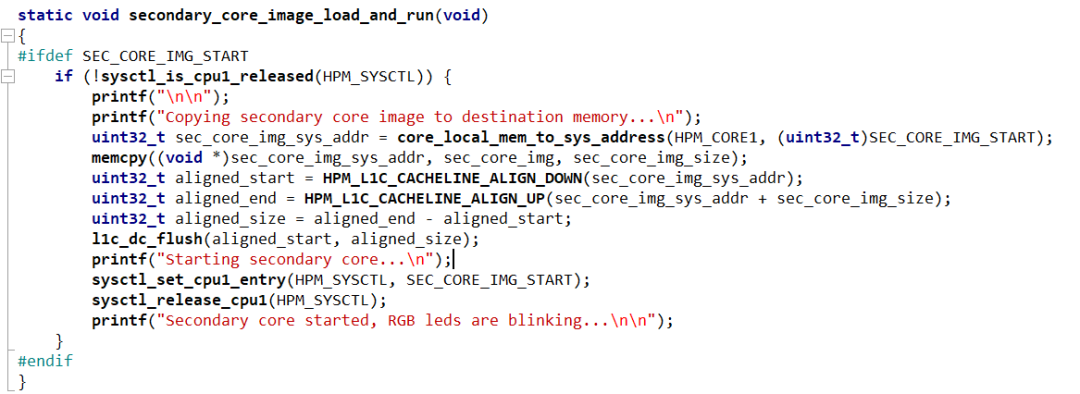

先在core0的工程增加从核镜像加载处理接口。

并将该接口放置在board_init之后

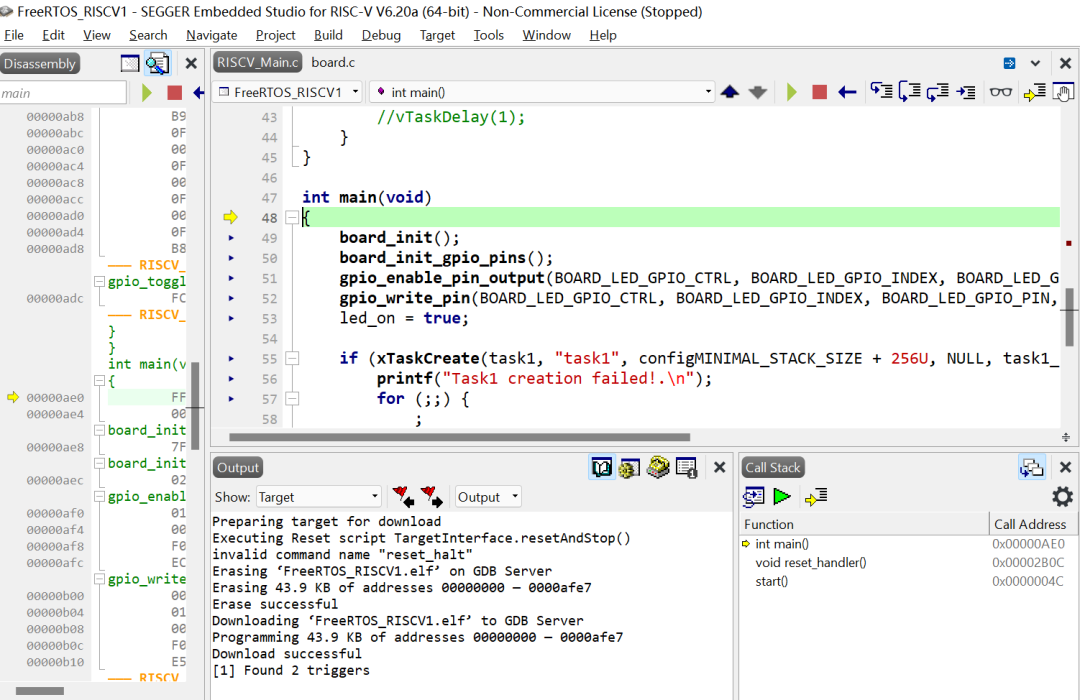

多核调试

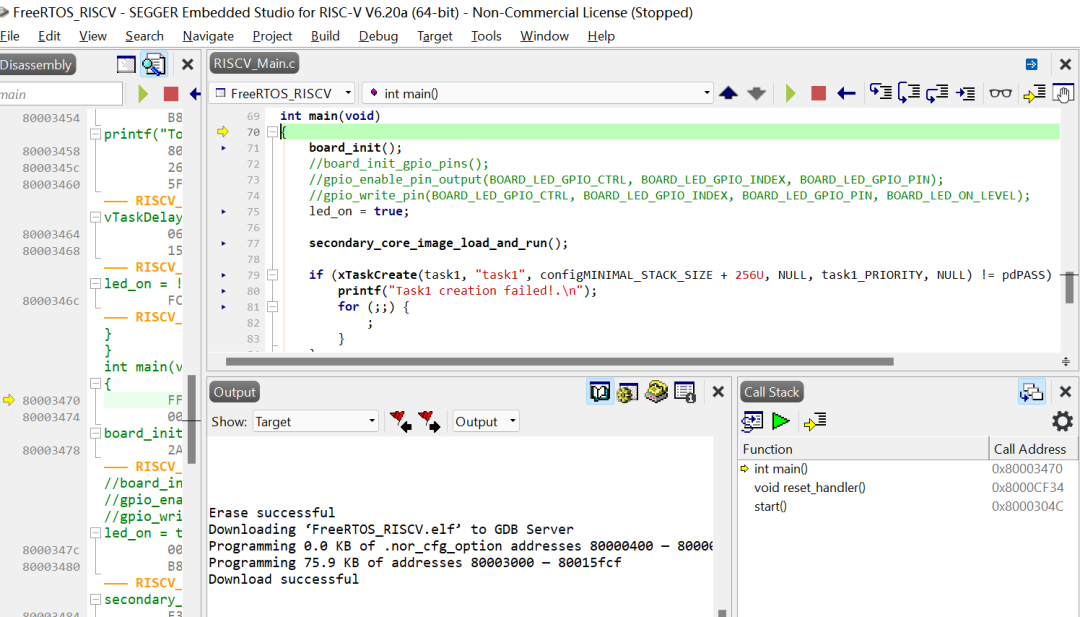

在进行双核程序调试时,先下载并启动core0的程序。

先在core0的SES工程中按F5,让core0主核的程序运行;再在core1的SES工程中按F5,让core1的程序运行。

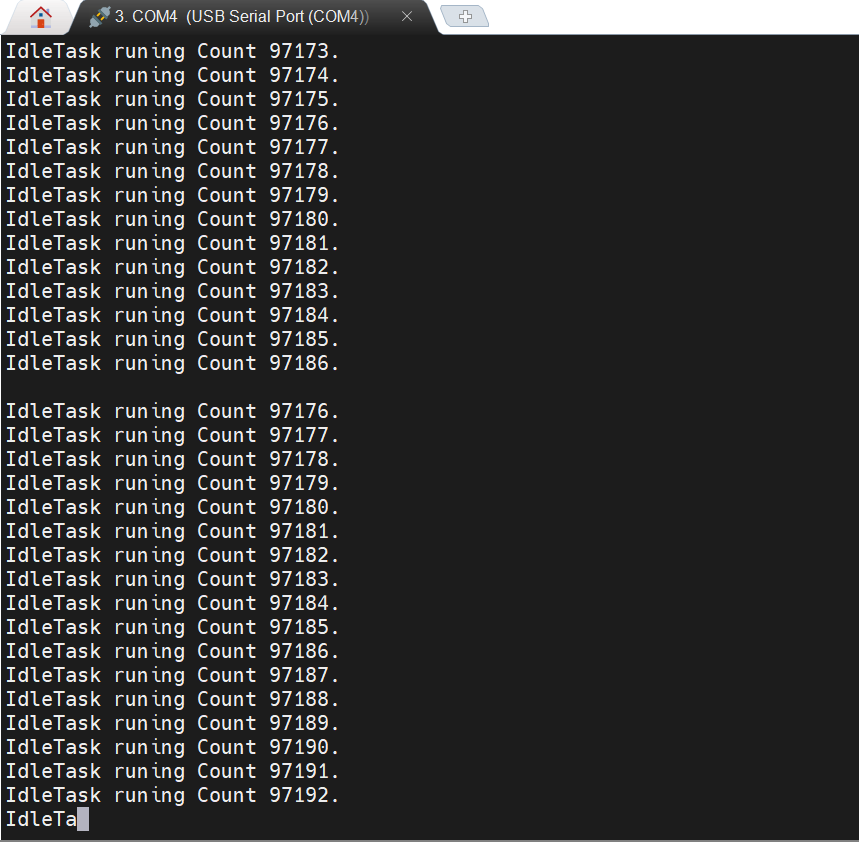

可以看出core0的程序任务1和任务2,能够轮流执行,并且IDLE任务在他们休眠的间隙能够被调度执行。

对上面的代码稍作调整,调整任务1和任务2的延时时间,其中task2不再延时。

结论

HPM6750 采用双RISC-V 内核,可以方便的适配主核和从核的各种接口,能够充分灵活地利用soc的各种资源。为实时性要求高,控制内容多样的应用提供更为友好的体验。

-

双核

+关注

关注

0文章

37浏览量

15188

发布评论请先 登录

相关推荐

怎么从零基础入门先楫

先楫HPM6E00威廉希尔官方网站 日 | 百人研讨共话工业应用创新及发展趋势

有奖提问!先楫半导体HPM6E00系列新品发布会!!

工业芯标杆,邀您来围观——先楫HPM6E00新品上市在即

威廉希尔官方网站 赋能,携手共创未来:先楫半导体成功举办2024 DFAE培训活动

聚焦工业多场景应用,先楫发展势头锐不可当

先楫6880如何实现bootload + APP应用跳转

引领极致视界——先楫高性能MCU HPM6800系列产品生态绽放,共链未来

先楫高性能MCU HPM6800系列产品生态绽放,共链未来

芯原2.5D GPU IP赋能先楫半导体HPM6800系列RISC-V MCU

芯原宣布先楫半导体的HPM6800系列采用了高性能2.5D图形处理器(GPU)IP

先楫半导体上海办公室乔迁大吉

先楫 RT-Thread BSP v1.4.0 正式发布

“狂飙!来感受先楫芯高速双引擎的澎湃动力。”

“狂飙!来感受先楫芯高速双引擎的澎湃动力。”

评论