低通FIR将基带信号的旁瓣滤去,保留基带信号的主瓣。基带信号之所以是基带信号,正是因为它处在零中频附近。实际上,信号之所以在高频甚至射频的原因主要有:

1.接收天线的长度与电磁波的波长存在正比例关系,所以波长越小,接收天线也可以做的越小。电磁波波长与频率存在反比例关系,所以需要将基带信号上变频至高频部分,方便天线接收。

2.方便扩展信号带宽,提高频带利用率。

本文将通过DDS IP核输出的正弦波,与基带信号混频上变频至高频部分,将涉及一点数字信号处理内容。

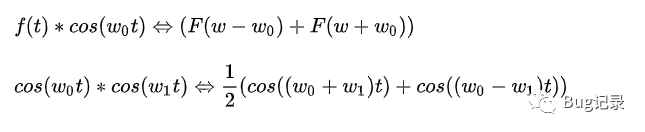

首先,简单写一下上变频的数学理论基础,

基带信号乘以一个正弦波,频域卷积,频谱上会将基带信号的频谱搬移到正弦波的频率。

所以,我们需要做的就是生成一个所需的正弦波,并与基带信号相乘。这个过程就需要使用到Xilinx的DDS IP核以及DSP IP核。

在Vivado中IP Catalog中找到DDS IP核,

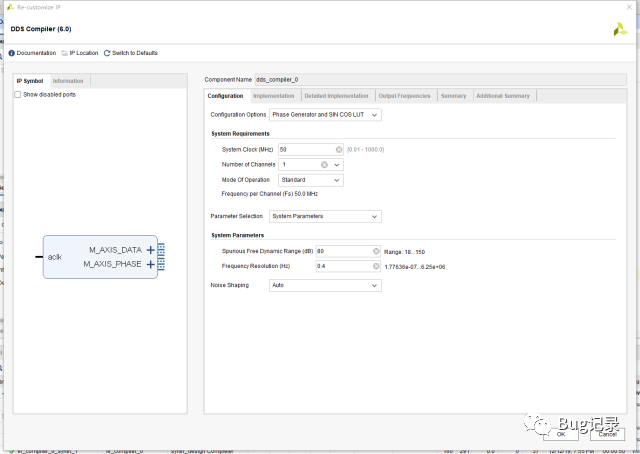

DDS IP核设置

系统时钟选择50MHz,通选数量选择1,其他的可以保持默认。注意Configuration Option,这里选择Phase Generator and SIN COS LUT,这个模式会根据GUI设置自动产生所需要的频率的正弦波;而另一种模式SIN COS LUT ONLY,会根据输入的相位信息phase_data输出对应的正弦波值,相位信息需要不断地自加获取输出的正弦波值。两种模式各有利弊,第一种模式设置更方便,第二种模式不需要固定输入时钟,可以改变参数获取不同的频率的正弦波。

第一种模式下,dds实例化,只需要取m_axis_data_tdata的数据即可,输出的波形按照GUI设置的要求。

dds_compiler_0 dds_inst (

.aclk(clk_50m), // input wire aclk

.m_axis_data_tvalid(), // output wire m_axis_data_tvalid

.m_axis_data_tdata(cos_o), // output wire [15 : 0] m_axis_data_tdata 13 - 2

.m_axis_phase_tvalid(), // output wire m_axis_phase_tvalid

.m_axis_phase_tdata() // output wire [31 : 0] m_axis_phase_tdata

);

第二种模式下,dds实例化,需要不断地自加相位数据,DDS会根据相位数据输出对应的正弦波值。这更像ROM表,相位数据为ROM地址,根据ROM地址输出相应地址的数据。

always @ (posedge clk or posedge rst)beginif (rst)

phase_data <= 16'd0;

else

phase_data <= phase_data + fre_word;end

dds_compiler_0 dds_i (

.aclk(clk), // input wire aclk

.aclken(1'b1), // input wire aclken

.s_axis_phase_tvalid(1'b1), // input wire s_axis_phase_tvalid

.s_axis_phase_tdata(phase_data), // input wire [15 : 0] s_axis_phase_tdata

.m_axis_data_tvalid(), // output wire m_axis_data_tvalid

.m_axis_data_tdata(t_data) // output wire [31 : 0] m_axis_data_tdata);

其实DDS的原理正是ROM表存储,相位数据就是地址信息,根据地址信息查找表,输出对应数据,FPGA擅长的正是查表。第一种模式固定了相位数据和相位差,简化了操作但固定了使用时的输出频率;第二种模式开放了相位数据接口,输出的频率更加多变。

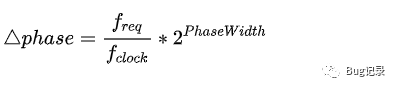

根据公式可知,

上面示例中的fre_word计算来源于这个公式。

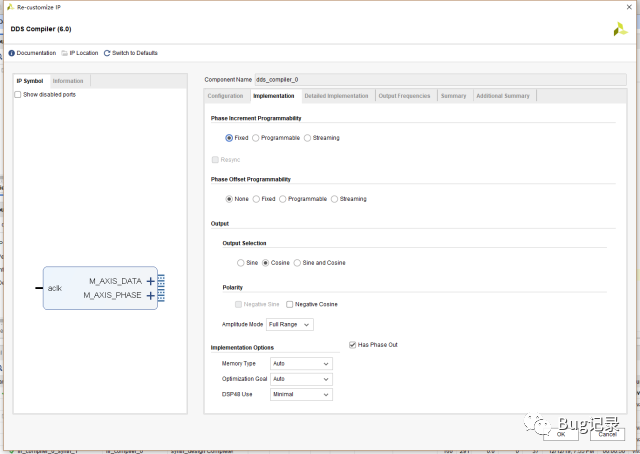

DDS IP核设置

Output Selection可以选择输出的波形是Sine,Cosine,Sine and Cosine。注意选择Sine and Cosine时输出的信号宽度是Sine,Cosine的两倍,需要使用截位的方法将信号的前半段与后半段分开。高半段为Sine,低半段为Cosine。

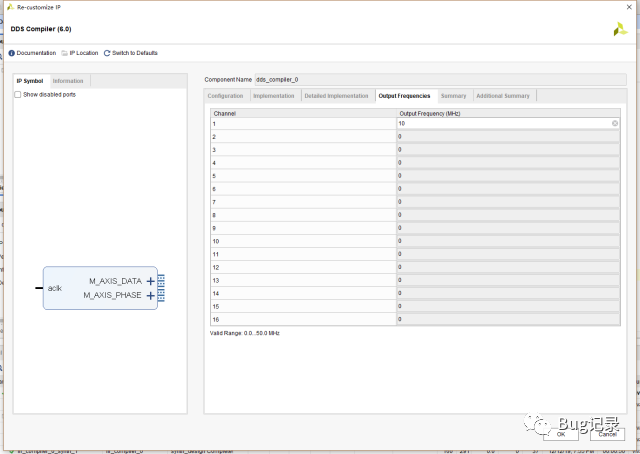

DDS IP核设置

这个部分根据需要的频率进行设置。

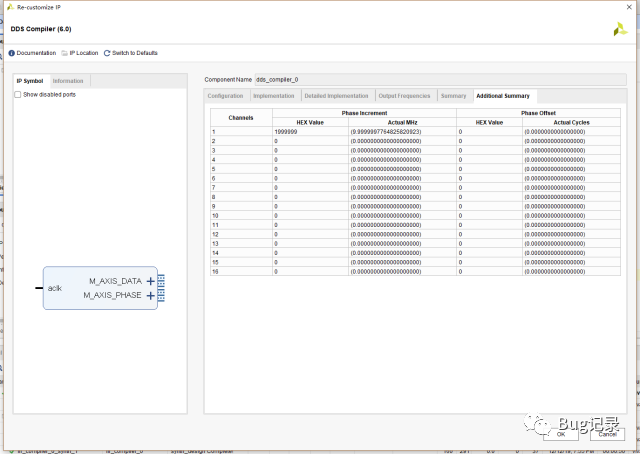

DDS IP核设置

可以看到预想10M,但由于精度的问题,实际输出的频率是9.9999MHz,非常接近了。

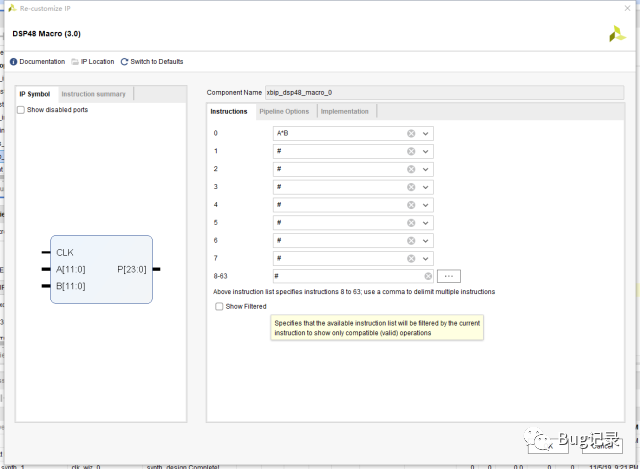

接下来就是DSP IP核的使用,在Vivado中IP Catalog中找到DDS IP核。

DSP IP核

使用最简单的乘法功能,其他通道不选择。

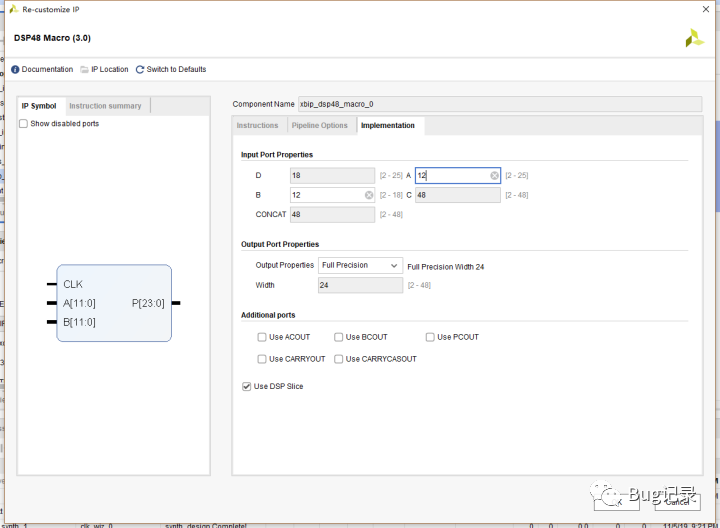

DSP IP核

设定A,B的位数以及输出数据的位宽之后就完成了DSP IP核的设置。

xbip_dsp48_macro_0 dsp_product_inst (

.CLK(clk_50m), // input wire CLK

.A(fir_out[19:8]), // input wire [11 : 0] A

.B(cos_o[13:2]), // input wire [11 : 0] B

.P(out_data) // output wire [23 : 0] P

);

为了平衡性能与面积,所以A,B设置的12位输入,分别对FIR和DDS的正弦波进行了截位

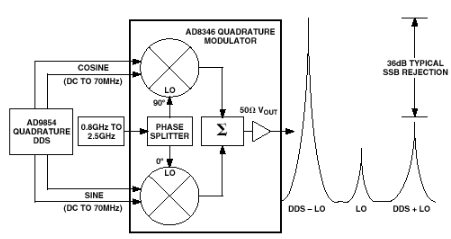

由此,就完成了基带信号的上变频操作;但是,这样的上变频会带来双边带问题,占用了2倍的基带信号带宽。为了解决这个问题,又可以引入IQ调制。IQ调制如何操作以及它的原理等待后续的文章梳理。

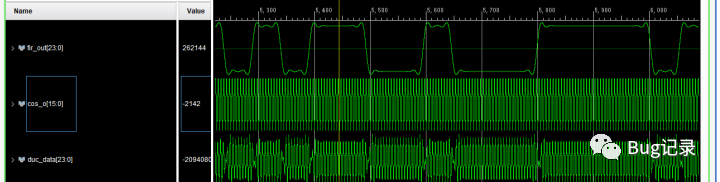

最后,上板测试可以看到如下图所示。

实测图

duc_data是搬移到高频之后的信号,最后可以对duc_data进行截位操作,以适应实际中DAC的位数限制。

-

正弦波

+关注

关注

11文章

642浏览量

55379 -

DDS

+关注

关注

21文章

634浏览量

152649 -

信号处理器

+关注

关注

1文章

254浏览量

25275 -

电磁波

+关注

关注

21文章

1454浏览量

53835 -

FIR滤波

+关注

关注

0文章

6浏览量

9833

发布评论请先 登录

相关推荐

基于数字上变频器的中频调制器

AD9789基带数字上变频频率为什么能到Fdac/16?

有关AD9361的上变频

AD9789基带数字上变频频率为什么能到Fdac/16

多天线多载波数字上下变频的FPGA实现方法有哪些?

PXI 5610实现上变频信号发送

AD9739上变频功能实现原理是什么?

基于QDUC的雷达上变频电路的设计

通信系统中数字上变频威廉希尔官方网站 的研究与设计

基于FPGA的高效灵活数字上变频实现设计

正交DDS信号至800至2500MHz频段的单边带上变频

使用DDS将基带信号上变频

使用DDS将基带信号上变频

评论