1、什么是边沿检测

边沿检测用于检测信号的上升沿或下降沿,通常用于使能信号的捕捉等场景。

2、采用1级触发器的边沿检测电路设计(以下降沿为例)

2.1、设计方法

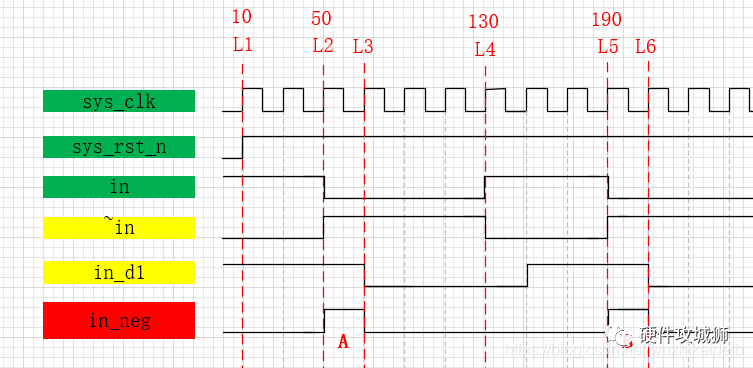

设计波形图如下所示:

各信号说明如下:

sys_clk:基准时钟信号(这里设定为50MHz,周期20ns)

sys_rst_n:低电平有效的复位信号

in:输入信号,需要对其进行下降沿检测

~in:输入信号的反相信号

in_d1:对输入信号寄存一拍

in_neg:得到的下降沿指示信号,该信号为 ind1 && ~in

对上图进行分析:

信号in是我们需要对其进行下降沿检测的信号

信号~in是将信号in反向

信号in_d1是使用寄存器寄存in信号,即对其进行打拍,或者说是同步到系统时钟域下

输入信号开始为高电平,在L2处变为低电平,产生第1个下降沿,在L5出产生第2个下降沿

A处为产生的第1个下降沿指示信号,B处为产生的第2个下降沿指示信号

由此我们可以推导出边沿检测信号产生的一般方法:

将需要检测的信号寄存一拍,同步到系统时钟域下,得到信号 in_d1

将需要检测的信号反向,得到信号 ~in

将信号 in_d1 反向,得到信号 ~in_d1

通过组合逻辑电路可以得到下降沿信号 in_neg:assign in_neg = ~in && in_d1

同样通过组合逻辑电路可以得到上升沿信号 in_pos:assign in_pos = in && ~in_d1

双边沿检测就是将上两条加(或运算)起来就可以了,化简后有:双边沿信号 in_both = in ^ ind1

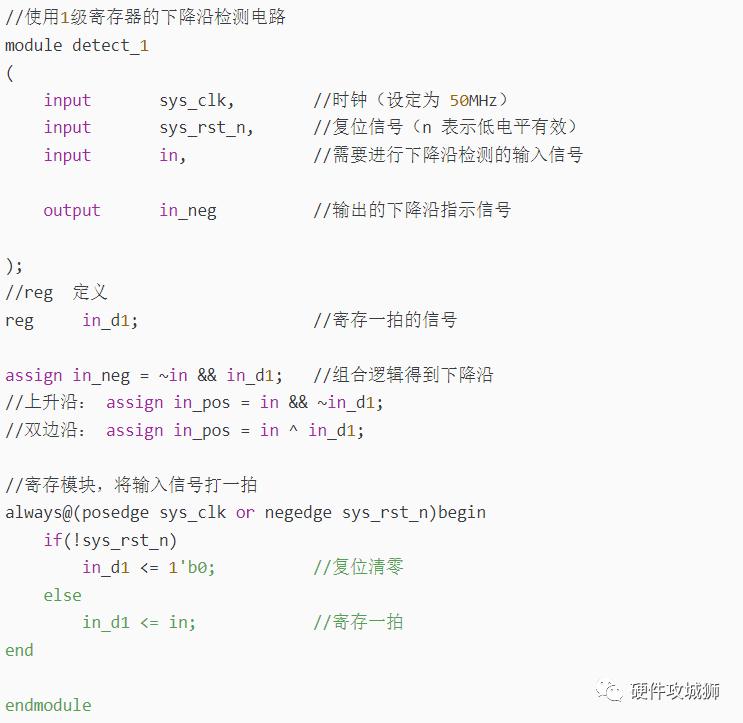

2.2、Verilog实现

根据上文分析不难编写Verilog代码如下:

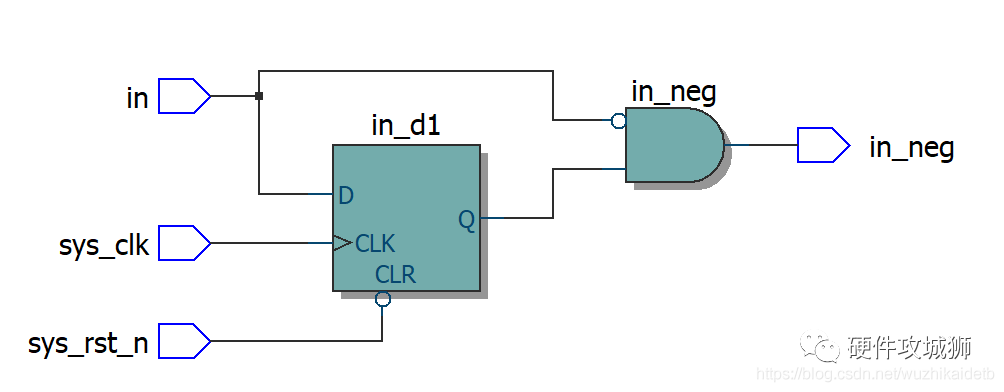

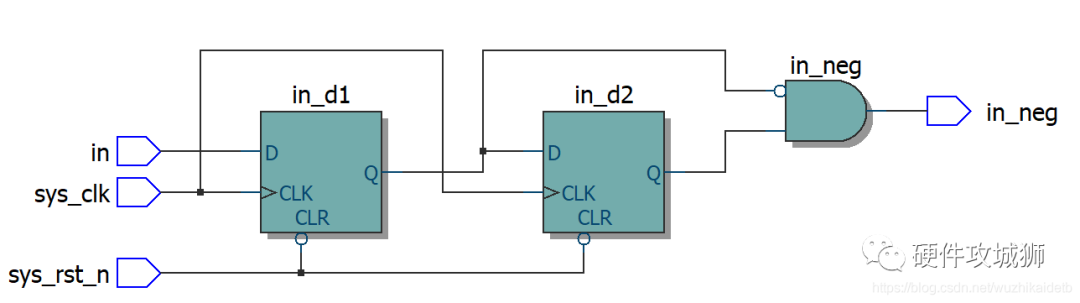

2.3、RTL电路

上图为生成的RTL电路:该电路由一级D触发器+与逻辑门构成。

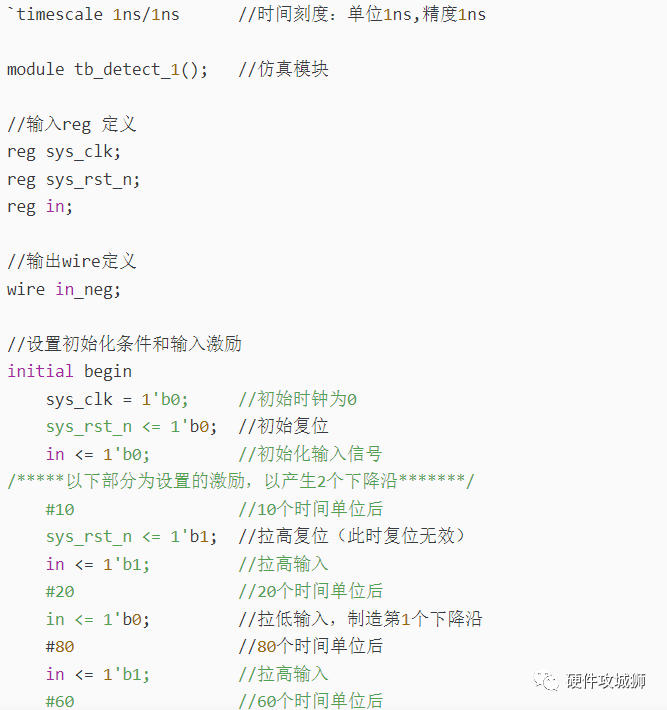

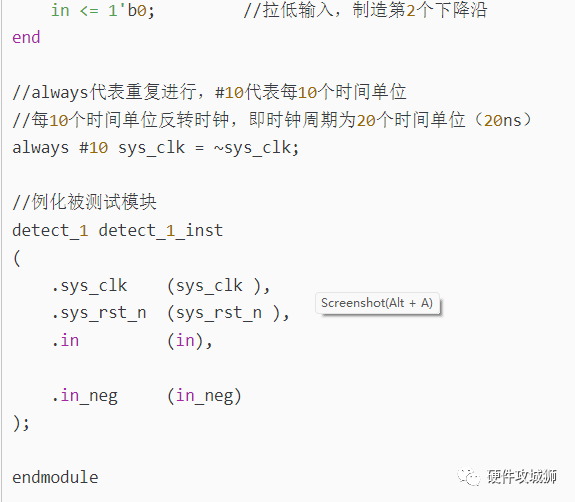

2.4、Testbench

Testbench文件需要例化刚刚设计好的模块,并设置好激励。

2.5、仿真结果

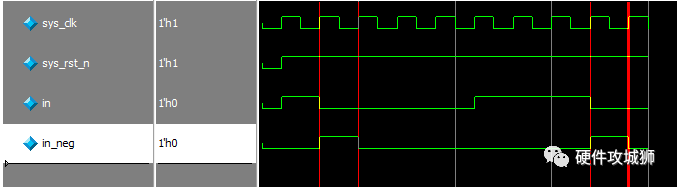

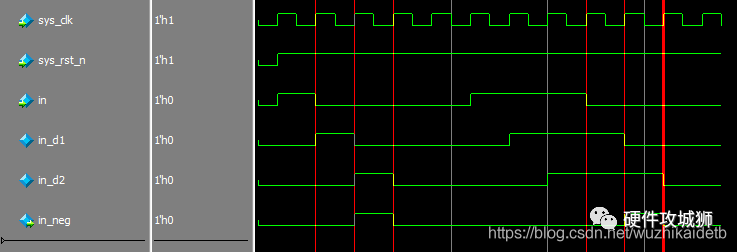

使用ModelSim执行仿真,仿真出来的波形如所示:

从波形图可以看到:

10ns后停止复位

在第1条参考线处输入信号 in 产生了第1个下降沿信号

在第3条参考线处输入信号 in 产生了第2个下降沿信号

在第1条参考线和第2条参考线之间的产生了一个周期的下降沿指示信号 in_neg

在第3条参考线和第4条参考线之间的产生了一个周期的下降沿指示信号 in_neg

3、采用2级触发器的边沿检测电路(以下降沿为例)

3.1、设计方法

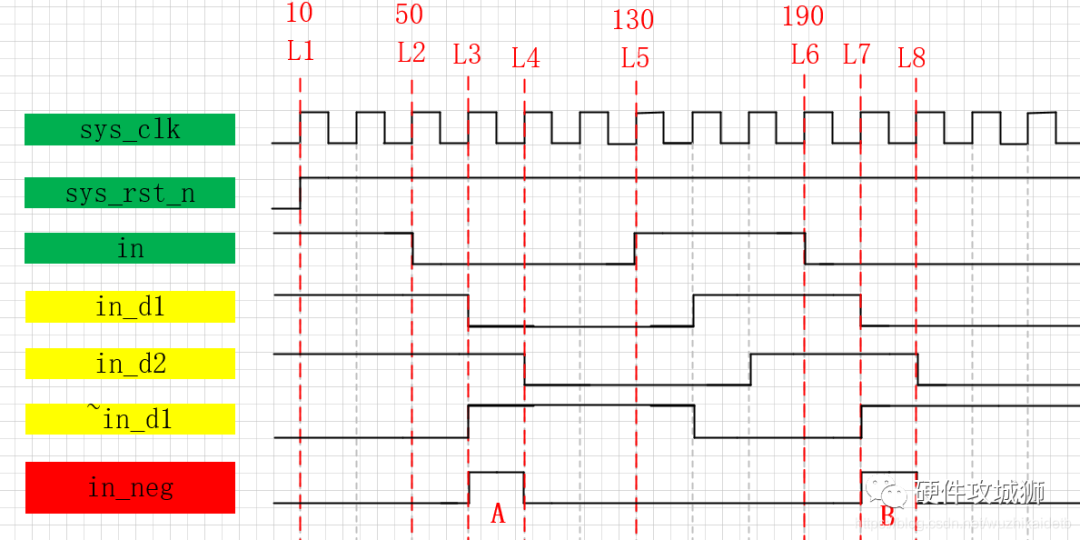

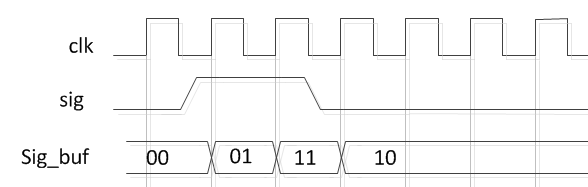

设计波形图如下所示:

各信号说明如下:

sys_clk:基准时钟信号(这里设定为50MHz,周期20ns)

sys_rst_n:低电平有效的复位信号

in:输入信号,需要对其进行下降沿检测

in_d1:对输入信号寄存1拍

in_d2:对输入信号寄存2拍

~in_d1:in_d1信号的反相信号

in_neg:得到的下降沿指示信号,该信号为 ~ind1 && ind2

对上图进行分析:

信号in是我们需要对其进行下降沿检测的信号

信号in_d1是使用寄存器寄存in信号,即对其打1拍

信号in_d2是使用寄存器寄存in_d1信号,即对其打1拍

信号~in_d1是将信号in_d1反向

输入信号开始为高电平,在L2处变为低电平,产生第1个下降沿,在L5出产生第2个下降沿

A处为产生的第1个下降沿指示信号,B处为产生的第2个下降沿指示信号

输出的下降沿指示信号落后下降沿一个时钟周期,这是因为对输入信号进行了寄存以消除亚稳态

由此我们可以推导出边沿检测信号产生的一般方法:

将需要检测的信号分别寄存1拍、2拍,同步到系统时钟域下,得到信号 in_d1、in_d2

将in_d1信号反向,得到信号 ~in_d1

将in_d2信号反向,得到信号 ~in_d2

通过组合逻辑电路可以得到下降沿信号 in_neg:assign in_neg = ~in_d1 && in_d2

同样通过组合逻辑电路可以得到上升沿信号 in_pos:assign in_pos = in_d1 && ~in_d2

双边沿检测就是将上两条加(或运算)起来就可以了,化简后有:双边沿信号 in_both = in_d1 ^ in_d2

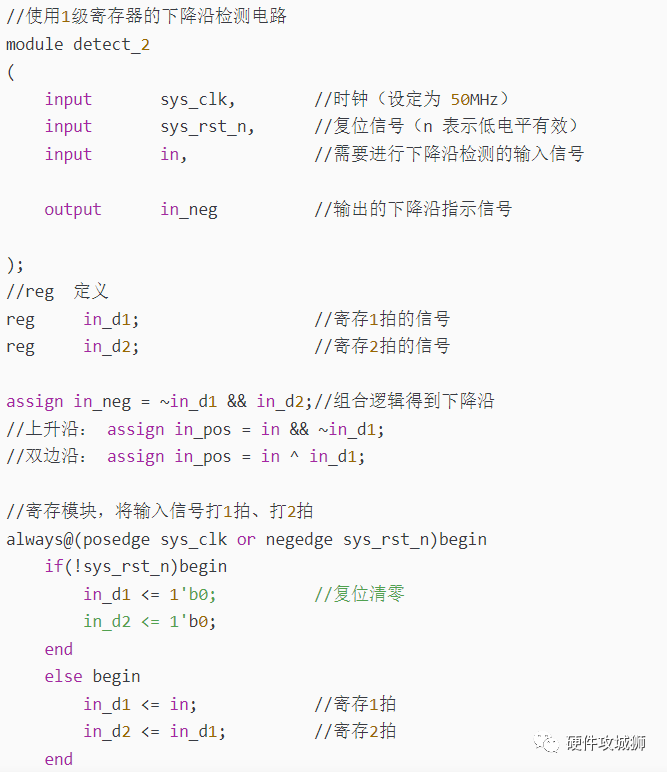

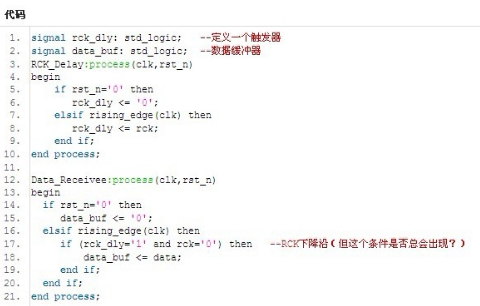

3.2、Verilog实现

根据上文分析不难编写Verilog代码如下:

3.3、RTL电路

上图为生成的RTL电路:该电路由2级D触发器+与逻辑门构成。

3.4、Testbench

Testbench文件同2.4章。

3.5、仿真结果

使用ModelSim执行仿真,仿真出来的波形如所示:

从波形图可以看到:

10ns后停止复位

在第1条参考线处输入信号 in 产生了第1个下降沿信号

在第4条参考线处输入信号 in 产生了第2个下降沿信号

在第2条参考线和第3条参考线之间的产生了一个周期的下降沿指示信号 in_neg

在第5条参考线和第6条参考线之间的产生了一个周期的下降沿指示信号 in_neg

两级寄存器构成的边沿检测电路可以有效的防止亚稳态的产生,产生的使能信号会落后一个时钟周期。

责任编辑:彭菁

-

触发器

+关注

关注

14文章

2000浏览量

61134 -

检测信号

+关注

关注

0文章

6浏览量

6306 -

时钟信号

+关注

关注

4文章

448浏览量

28542

原文标题:4、参考

文章出处:【微信号:mcu168,微信公众号:硬件攻城狮】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA设计中的边沿检测问题

什么是边沿检测

什么是边沿检测

评论