每一代新产品的性能改进通常都伴随着用户必须遵守的实际要求,以便从运算放大器或转换器获得最佳性能。老一代运算放大器通常需要外部补偿来定制响应;闪存A/D速度快,但耗电且输入阻抗低。BiMOS转换器简化了应用问题;典型的高阻抗良性输入结构易于驱动。高速CB运算放大器和基于开关电容的CMOS转换器可最大限度地降低功耗和价格。运算放大器AD8011驱动AD876 A/D的应用显示了新一代IC的优势和实际问题。

高速开关电容A/D架构要求用户在设计接口电路时了解一系列独特的问题。最佳接口取决于应用是只需要低失真和杂散(动态特性)、低噪声,还是同时需要低噪声和低失真。

整个信号链(处理信号的一系列功能元件)必须优化总谐波失真(THD)和无杂散动态范围(SFDR)等规格的系统(例如通信系统)通常涉及频谱分析或处理。输入信号在样本之间以相对较小的增量变化;信号含量限制在奈奎斯特频率<(即采样率的1/2)。

专注于噪声性能的系统可能会牺牲THD和SFDR来增加动态范围(SNR)。虽然失真规格在这些低噪声应用(如基于CCD的成像)中可能并不那么重要,但可能需要宽带宽和快速瞬态响应来确保快速建立。

数据采集系统,如DSO-数字采样示波器-是需要低杂散和失真以及宽动态范围(SNR)的典型应用。除了电压和电流噪声外,相位噪声(例如由孔径抖动产生的相位噪声)也值得关注。这些系统通常处理各种各样的信号,执行频谱信号处理和处理大规模瞬变(通常来自多路复用前端)。

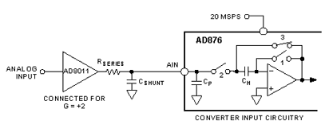

驱动开关电容ADC输入:AD876的输入保持电容必须在每个时钟周期充电至新的输入电压。输入驱动器必须提供的电量取决于上一次转换时存储在保持电容上的电压与采样时钟从高电平(保持模式)转换到低电平(轨道)时施加到A/D的电压之差。此差异越小,所需的增量费用就越少。另一方面,对于转换之间的满量程变化,输入驱动器必须提供较大的电荷增量。图2所示电路由AD8011驱动AD876,说明了性能选项。无论运算放大器本身如何配置,增加一个串联电阻(可能还有一个并联电容)都可以提高运算放大器/转换器对的性能。

为了研究为特定应用选择最佳值电阻和电容时的一些考虑因素,AD8011的增益配置为+2(带宽约为180 MHz),并如图所示连接到AD876输入。

图2.驱动具有开关电容采样保持的采样ADC。

图3a显示了测试信号:顶部迹线是AD8011的interwetten与威廉的赔率体系 输入,这是一个1 V p-p方波。底部迹线是AD876采样时钟。当时钟为低电平时,SHA 跟踪输入;当它变高时,A/D 的 SHA 切换到保持。请注意,AD876每次转换都必须获得输入电压的满量程变化;这种情况对AD8011提出了最严格的要求,因为它必须在每个转换周期提供最大的电荷量。AD8011无法瞬时提供电荷差,因此在A/D采样时钟转换期间,转换器输入端存在瞬变。

图3.输入波形。

图3b显示了输入方波在扩展标度上处于正偏移时的瞬变(上图),具有25 ns跟踪模式时钟脉冲。较小的上升沿保持瞬态并不重要;它发生在下一个样本采集之前很久。当ADC获取满量程电荷变化时,下降沿瞬变约为-114 mV;恢复和建立至0.1%(10位或2 mV)必须在跟踪模式脉冲的持续时间内进行,并且在上升沿之前 - 此处,使用20 Ω电阻时,恢复和建立时间为100 ns。对于20 MSPS采样速率(50%占空比),恢复必须在25 ns以内。较慢的放大器可用于较低的采样率。

图4.转换器和放大器电路的失真和噪声。

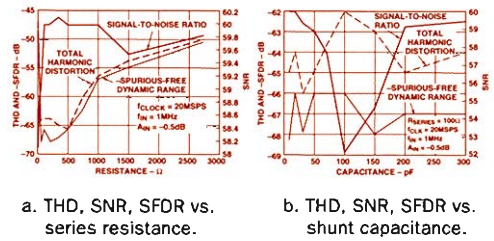

串联电阻器有助于:大多数应用受益于AD8011输出和AD876VIN引脚之间的串联电阻,以将AD8011的输出级与AD876的输入电容隔离开来,并限制运算放大器必须提供的峰值电流。低至33 Ω(图4a)大大降低了THD(从-47dB到-64 dB),并增加了SNR(从58dB增加到60 dB)和SFDR(从48dB增加到68 dB);可以使用高达 500 Ω,而不会因非线性容性负载而增加失真。小串联电阻也改善了建立时间;如果没有它,ADC的容性负载直接施加在放大器的输出端,会导致放大器的响应出现一些峰值,并且建立速度变慢。但是,考虑到ADC的输入电容、杂散和任何增加的电容,增加电阻会通过低通滤波降低带宽。500 Ω 和 20 pF 的频率约为 3 MHz,为 -16 dB。

分流电容限制噪声:AD876的全功率带宽至少为150 MHz,噪声带宽甚至更大。频率>采样速率1/2的宽带输入噪声将被混叠回基带,并将降低数字化信号的SNR。对于噪声敏感型应用,带串联电阻的并联电容(图2)可在AD876输入端滤除高频外部噪声。

图4b显示了使用100 Ω串联电阻和各种分流电容时的噪声和失真。SFDR相对不受影响,保持在66至68 dB范围内。但是,对于50 pF至200 pF范围内的电容,THD大幅增加(从-65至-62 dB),SNR大幅降低(从59降至低至52 dB)。SNR降低是由未完全稳定的保持到跟踪瞬变的毛刺引起的高次谐波混叠引起的;在876b条件下,它们在AD4输出端的基带信号中显示为噪声。

对于更高的并联电容值,SNR会大大提高,但代价是带宽。(例如)200 pF时,整个系统的-3 dB带宽降至约8 MHz,输入信号中的任何快速瞬变在单个转换周期内都可能无法稳定到10位精度。

当使用串联R和并联C来优化系统行为时,考虑应用的目标非常重要。如果动态性能在宽输入频率范围内至关重要,则最好使用20 Ω串联电阻将分流电容保持在100 pF以下。如果要优化噪声性能,请考虑更长的RC时间常数,以及是否可以用瞬态响应换取低噪声。在任何情况下,在AD10采样时钟进行跟踪保持转换之前,输入有时间建立至876位精度,性能最佳。还要记住,AD8011非常安静,可以在早期阶段滤除宽带噪声,而不必担心AD8011噪声会降低SNR。

审核编辑:郭婷

-

CMOS

+关注

关注

58文章

5724浏览量

235684 -

转换器

+关注

关注

27文章

8724浏览量

147414 -

运算放大器

+关注

关注

215文章

4951浏览量

173126

发布评论请先 登录

相关推荐

AD8275 ADC驱动器,具有电平转换功能,可简化信号调理

Linear推出ADC驱动器LT6350

ADC驱动器或差分放大器设计指南

如何针对设计选择合适的差分ADC驱动器

三种不同的ADC驱动器架构和应用分析

ADI-高速差分ADC驱动器设计指南

应用示例—ADC驱动器

应用示例—ADC驱动器

评论