01

市场趋势和测量需求趋势

为了应对网络、服务器和存储速度和容量的快速提高的需求,促进了100GbE,400Gbp和1Tbps的通信系统的开发。而超过30Gbps的速率接口被这些系统所采用。

当处理高于30Gbps速率的信号时,相比传统较低速信号具有更大的挑战。本文描述了如何处理时钟和数据信号的传输差异,进行高速信号的抖动容限测试,以及处理高速传输的差分信号。

02

测试准备

准确的测量要求正确使用测量仪器。此外,也需要正确理解仪器的限制。超过这些限制的测量通常测量的是仪表自身的特性,而非待测件(DUT)的特性。例如,当使用采样示波器进行波形测量时,如果波形内包含由采样示波器带宽范围外的频率分量,那么输入波形的真实特性不会被显示,相反,显示的是采样示波器的特性。

对于抖动容限测试来说也是类似的,如果在测试中抖动超过了仪器中设置抖动容限,仪器的抖动容限而非DUT的抖动容限会被显示在结果中。如果测试仪器内部包含有D-flip-flop,FIFO,或者其他重定时电路或者类似时钟恢复的PLL电路,此类电路会成为抖动容限测试的瓶颈。当进行抖动容限测试时,知道测量仪器的实际测试性能限制非常有必要。

即使在测量系统中的测量仪器有足够的抖动容限,测试结果也许会比DUT实际特性更差,取决于实际设置。最近数据信号速率提升要求严格评估抖动的影响,以保护信号传输质量。由于噪声环境的不利影响(例如来自电源、热量及PLL),测试器件抖动的注入变得愈发复杂和快速,并且总抖动量呈现上升趋势。在这些条件下,抖动容限测试必须考虑过去不会构成大问题的项目的影响,例如测试系统中时钟和数据信号的路径长度差异。

下一节介绍处理时钟和数据路径长度时的注意事项。

03

时钟和数据路径长度的差异

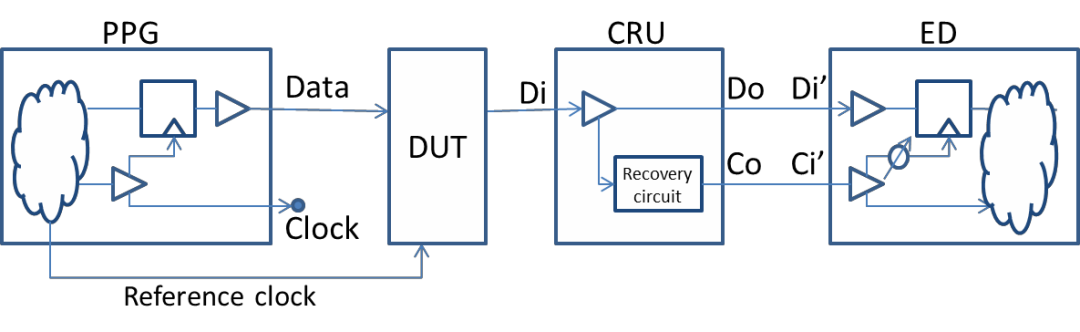

本节描述测量系统中时钟和数据路径长度,以脉冲码型发生器(PPG)通过待测件和时钟恢复单元(CRU)链接至误码检测器(ED)为例。

图 3.1:抖动容限测试系统

DUT的数据输出链接至CRU。CRU将数据信号分为两路:一路通过直接通过,未改变信号后进行输出,另一路连接至时钟恢复电路。CRU输出数据信号,时钟信号从数据信号中恢复。此处,比较了时钟的定时和CRU的数据输出。由于数据经由CRU 被简单分割,数据会通过一个更短的路径。同时,时钟信号基于数据信号恢复,时钟恢复电路本身会有一些延时。因此,相较于数据信号,时钟信号会有更长的路径。

图 3.2:CRUI/OTiming

图3.2展示的并非突发数据输入直到时钟恢复的时间。而展示的是特定数据交叉点和相位对齐时钟边缘,其中Di是 CRU输入数据, Do是CRU 输出数据, Co是CRU恢复的时钟输出。

虽然使用实际CRU无法确定数据边缘定时相位是否对齐,但如果相位对齐,逻辑上我们可以得出结论,即使在比较满的比特率下,图3.2中的Dt和Ct时间也不会改变。图中Dt 是从数据输入到CRU 至输出的数据传输延迟,Ct是从数据输入到CRU至恢复时钟输出的延迟。

虽然我们不能通过观察单个比特率下的Co和Do波形,来确定Dt和Ct的边倾角是否恒定,但是我们可以通过观察多个比特率下的波形来识别Dt和Ct恒定的数据和时钟边缘。无论比特率如何,Dt和Ct之间的关系是恒定的,这种关系被称为“绝对相位对齐”。

图 3.3:CRUI/OTiming(低比特率)

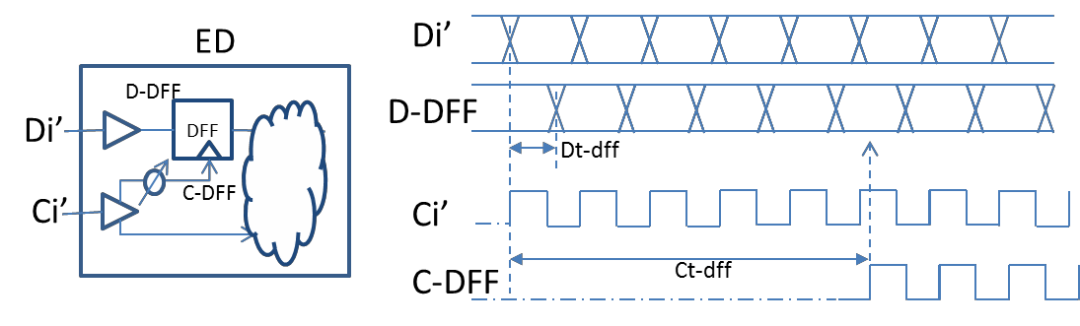

在测试系统中,我们还必须知道在ED中时钟和数据信号的路径长度的差异。为了准确测量数据信号,仪器的设计必须使到第一个D-flip-flop是最短的。时钟信号路径往往比数据信号路径更长,因为在ED端后部的电路生成分频时钟。如图3.4所示,这导致Ct-dff时间比Dt-dff.更长。

图 3.4:ED 中的路径和时序

此外,如果具有D-flip-flop的单元,例如预加重单元,在测试系统的中间被连接,PPG和预加重间数据和时钟信号路径长度必须以相同方式确认。

图3.5: PPG和预加重模块间的连接和时序

例如,在预加重的情况下,PPG 输出半速率时钟至预加重单元,预加重单元加倍后变为全速时钟。在这种情况下,PPG和预加重单元间由于使用倍频半速率时钟的电路延时,使得时钟传输时延(C-emp)比数据传输时延更大(D-demp)。

在这些情况下,为了在这些设备间对齐时钟和数据的相位,用于连接如CRU和ED、PPG和预加重单元的线缆长度,必须考虑到设备内部信号路径的差异以进行调整。由于CRU和ED之间的时钟路径由于(Ct–Dt)+(Ct-dff–Dt-dff)更长,因此数据线缆必须根据时延差来延长(图.3.2和3.4)。相似的,PPG和预加重单元时钟和数据可以通过延长数据路径来对齐(图.3.5)。

如果抖动影响比较小,在ED端时钟和数据信号绝对对齐是没有必要的。如果在ED中第一个D-flip-flop中时钟和数据满足保持时间和设置时间的条件,便可以进行有效测量。错误检测器有自动搜索和其他特性以自动调整数据和时钟关系,所以一般情况下,无需关注仪器内部的数据和时钟的关系。

相似的,如果抖动的影响比较小,用户无需调整Anritsu 预加重单元的相位关系,因为其内部会自动进行时钟和数据相位的调整。

接下来,那抖动影响比较大的情况如何?如上述,我们无需考虑在抖动影响较小时的绝对相位,但是如果抖动影响比较大时,测量系统必须考虑绝对相位。

接下来的例子描述了抖动带来的影响,具体通过比较将10-Hz,10 UI,正弦抖动注入于10-Gbps数据信后数据交叉点的变化来观察。

在50-Ω 传输线缆上,电信号通常以4.75 ns/m 的速度传输。这一位这当使用示波器进行数据信号测量时,每改变线缆长度10cm时,波形位置会位移475 ps。

10-Gbps 数据信号的每个周期都是100-ps 长,所以注入10UI抖动会使交叉点在1000ps内往返。在这种情况下,数据交叉点将移动等效于1000 ps x 2的距离,在使用上述4.75 ns/m 的电信号传输速度进行转换,这个长度相当于约42 cm。

接下来,考虑抖动调制速率。10 Hz抖动调制率意味着以10 Hz速率移动42 cm (即 每100ms)。相似的,10Mhz 的抖动调制率意味着每100 ns移动42 cm距离。换言之,在相同抖动下,更快的抖动调制率会有更大的移动距离。

图 3.6: 1UI 抖动下不同抖动调制率示例

现在,考虑时钟和数据路径不同的情况(即并相位并非完全对称)。

例如,如果时钟线缆是1 m,数据线缆为50 cm,会有50cm 的路径差距。换言之,数据信号会在发送后的2.375 ns后被收到,时钟信号会在发送后4.75 ns后被收到。通常情况下,接收机会考虑到此时钟延迟来调整相位,以优化时钟和数据之间的关系。也就是说,相位的设置将使上升沿靠近两个数据交叉点的中心以保证足够的设置和保持时间。

现在,考虑当抖动注入于同步数据并且同时发送的时钟信号时的变化,只关注由于抖动引起的时钟上升沿和数据交叉点之间关系的变化。即使在存在抖动的情况下,在时钟和数据同事改变的情况下,并且最佳相位关系得到保持,那么错误不会出现。然而,在数据或时钟接收路径包含限制抖动分量带宽的PLL之类的电路,并且抖动调制频率在电路带宽之外,会在接收测产生错误。错误发生的原因是时钟和数据中的抖动量不同,并且时钟和数据之间的相位关系将超过接收电路的设置和保持时间限制。为了描述导致绝对相位误差的机理,该解释假定测量系统中没有带宽限制电路。

由抖动引起的时钟和数据相位关系变化以电信号本身相同速度传输。因此,如果时钟和数据边缘同时开始移动,并且路径长度差距达到50-cm,则数据的变化将在2.375ns内到达接收机,而时钟测的变化是4.75 ns。如果在这2.375 ns内接收侧的时钟和数据相位差变得很大,以至于无法保证设置和保持时间,则信息无法正确传输,引起错误。

注入10-Hz、10UI、正弦抖动会引起时钟和数据在1s 内以100UI 往返移动。在2.375 ns间隔器件,对时钟和数据相位关系的影响应该很小,因为移动仅为475nUI(10UI/10Hzx2(往返)x2.375ns)。同时,注入、10-MHz、10UI、正弦抖动会对时钟和数据相位关系有很大的影响,因为通过相同的计算,移动为475mUI(10UI/10MHzx2(往返)x2.375ns)。

在较大抖动调制速率、抖动调制量以及时钟和数据路径长度的差异时,这种影响更大。这种影响会随着比特率增加而增加,因为在高比特率下更难保证接收机相位裕度。近期在数据传输速度的提升导致了更为严格的抖动容限要求。因此,虽然在之前不考虑数据和时钟的绝对相位,现在构建测量系统时必须纳入考虑范围。

仪器制造商可以指定其时钟和数据相位之间的差异。

04

差分测量时的注意事项

差分高速信号正在变得普及。差分信号的有几点优势。例如,Data和xData可以作为其他信号的阈值电压,同时减少Data和xData共模噪声的影响。此外,相较于单端设备,获得了两倍的电压裕度。然而,速率超过20Gbps信号需要仔细处理,因为在某些条件下,电压和相位裕度比使用单端设备时更差。

下面将讲述如何处理28Gbps差分信号。这类信号正在积极发展中。

图 4.1:差分测量系统

如上所示系统中,当PCB上的DUT通过线缆连接到ED时,从DUT上输出的差分信号通过PCB和线缆并连接到ED。当处理差分信号时,DUT上所有差分路径必须有相同长度。

虽然我们可以通过PCB上的路径减少差分之间的误差,但时使用PCB和测量线缆之间的电缆线路呢?这需要一个非常准确的相位匹配线缆。28-Gbps 信号周期大约为35.7ps。如前节所述,电信号处于50-Ω的传输线缆上传输速度为4.75ns/m,所以周期为35.7ps 的28-Gbps信号的电长度为7.5 mm。换言之,7.5 mm长度的线缆会有1-bit 的延时。当然,在默写条件下,系统不能正确处理差分信号,因为如果线缆长度只有2到3 mm,则偏差约为40%。

图 4.2:差分信号和时延

在图 4.2 所示的恒定高电平和低电平信号下,存在相位裕度小于电压裕度的风险。然而,由于传输线缆带宽和其他因素的限制,实际信号会受到ISI的影响。因此,不能保证在高电平和低电平之间完全变化。

图4.3: 受ISI 和延时影响的差分信号

图4.3 展示了差分信号间存在延时下,尽管使用了差分信号,但单端设备的电压裕度不会加倍。如果向信号中添加失真或者其他噪声,则裕度会进一步降低,当他们作为差分信号处理时,结果会比使用单端设备更糟。

此外,当电缆弯曲或者拉伸时,几乎所有电缆长度都会改变约2到3ps。尽管不怎么需要去担忧这点,但是使用单端设备或低比特率时弯曲电缆会改变使用快速信号(如28Gbps)时的电气长度周期的10%。

图4.4:电缆弯曲引起的电气长度变化

如何在这种情况下使用差分信号?一种解决方案时在相位匹配的线缆的每一端增加一个范围约为50至100 ps的小延迟装置,并将电气长度调整为相等。设备之间的电缆弯曲也必须最小化。

即便如此,完全消除由于电缆弯曲而产生的微小误差仍然是不可能的。在这种情况下,另一种解决方式是使用单端设备进行测量,而不是使用差分信号。

下节介绍如何测量电缆长度。

05

如何测量电缆长度差异

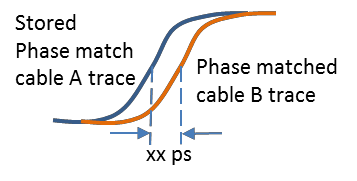

本节介绍两种确定电缆长度是否不同的方法。第一种是使用采样示波器检查脉冲信号波形;第二种是使用TDR。

5.1 使用脉冲波形检查

即使使用两条相位匹配的线缆和具有多个输入的采样示波器,我们仍旧不能通过同时连接两条电缆和测试两个输入来测量电缆长度是否相同,因为示波器输入之间存在内部偏差。尽管几乎所有示波器都有内部调整时延的功能,但是我们只描述一种一次只测量一个输入的方法。

图5.1: PPG和采样示波器组成的测试系统

设置在信号源(如PPG)处测量的比特率设置为1/10或者更低,模式长度设置为1024位,16位为1,所有其他位为0。将要测量的第一根线缆(A) 连接到PPG输出和示波器输入。

图 5.2:图案参数

观察示波器上PPG的输出,以查看0到1之间的一个交叉点,并将此波形保存在示波器上。接下来,断开电缆A并将第二根电缆(B)连接到同一范围输入。如果电缆长度非常相似,则可以看到存储的第一电缆A波形和当前显示的第二根电缆B之间的差异。

图 5.3:存储波形和显示波形之间的差异

尽管可以通过在时间方向上增加分辨率来进行更精确的测量,但是如果电缆之间存在较大的长度差,则在改变电缆后可能不会显示用于比较的边缘。在这种情况下,通过在时间方向上设置一个粗略的分辨率,并在观察两个电缆波形的边缘位置的同时逐渐增加分辨率来过的精确的测量。

5.2 使用TDR检查

这种方法使用TDR测量电缆长度,而不是使用PPG和示波器检查脉冲波形。

将电缆的一端连接到TDR电缆端,并使电缆的另一端保持未连接状态。测量开始时的波形如下图所示。

图 5.4:TDR线缆测试显示

对于未终结50-Ω线缆,显示器上的垂直部分时阻抗变为无穷大的地方。增加时间方向的分辨率,放大出现无限阻抗的点并保存测量结果。连接第二根线缆并进行相同测量。此处请注意,不是直接指示电缆长度的差异,是中间轴上的差异时电缆长度差异的两倍,因为TDR从作用于发送脉冲并测量直到反射返回的时间,这意味着它显示脉冲往返。

06

总结

使用高速信号正变得司空见惯。本文从测量抖动容限和测量差分信号两方面介绍了如何处理传输线长度以精确测量这些信号。这种讨论是一般性;更快比特率的情况仍有待解决。

-

PCB板

+关注

关注

27文章

1448浏览量

51630 -

发生器

+关注

关注

4文章

1368浏览量

61689 -

FIFO存储

+关注

关注

0文章

103浏览量

5970 -

PLL电路

+关注

关注

0文章

92浏览量

6407 -

DUT

+关注

关注

0文章

189浏览量

12376

发布评论请先 登录

相关推荐

如何处理CC2640的协议栈SPI传输数据?

最大数据传输速率与最大时钟频率之间的差异是多少?

如何处理好FPGA设计中跨时钟域间的数据

请问FPGA PLL产生的时钟信号和AD9779A的数据时钟信号的相位关系?

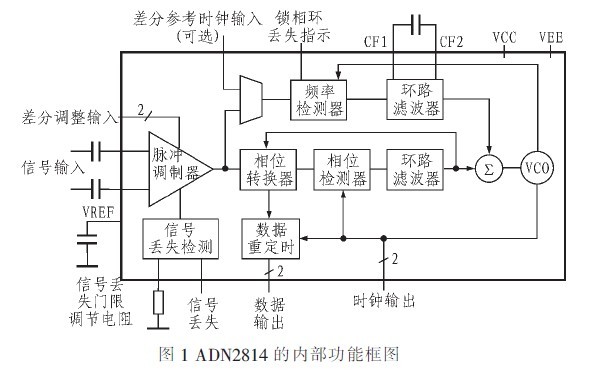

ADN2814时钟和数据恢复IC在光纤通信中的应用

示波器如何处理有噪声的信号?

如何处理时钟和数据信号的传输差异?

如何处理时钟和数据信号的传输差异?

评论