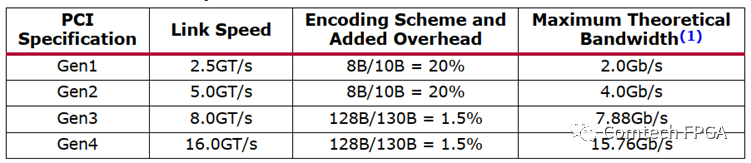

AMD FPGA自带PCIE硬核,实现了PCIE协议,把串行数据转换为并行的用户数据,以UltraScale系列FPGA为例,其支持Gen1.02.03.04.0,1~16 Lanes,如下图所示:

另外当前最新7nm系列器件Versal ACAP可支持到PCIE Gen5.0,单个Lane可达32G的线速率,如下图所示:

1.1 PCIE IP功能介绍

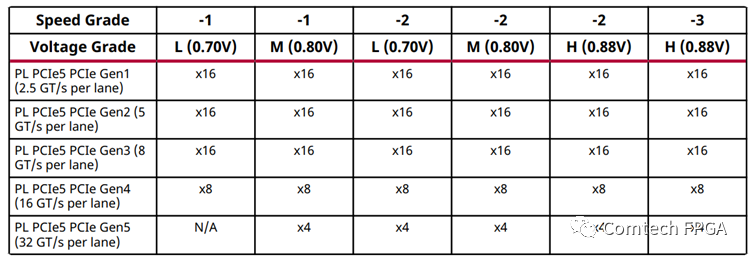

用户接口采用AXI接口实现PCIE TLP报文收发,从而完成PCIE传输事务的收发,最终实现PCIE的各种数据传输模式,系统架构如下图所示:

图左侧为FPGA PCIE IP,实现了PCIE协议,其与用户逻辑的数据交互主要通过AXI CQ,CC,RQ,RC四个接口,可以实现PCIE上行和下行的数据传输。

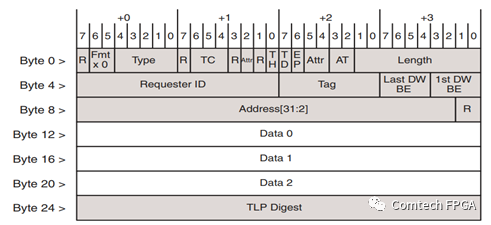

1.2 PCIE协议TLP报文介绍

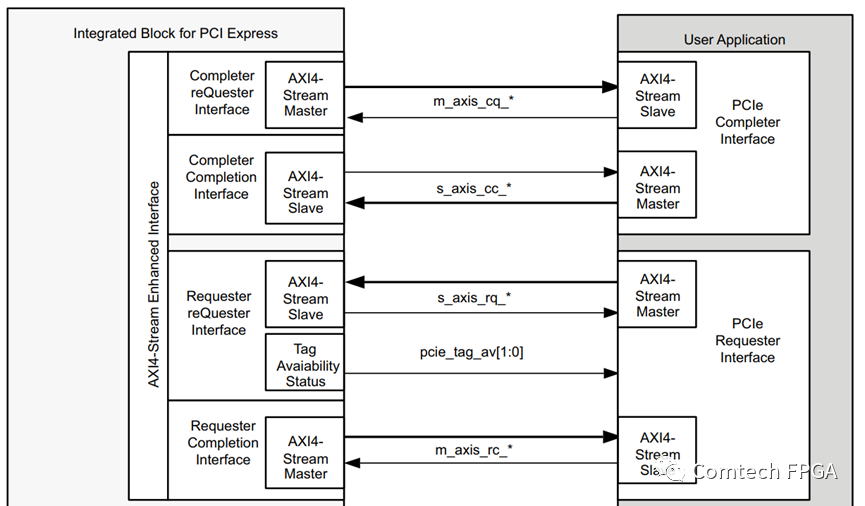

使用PCIE IP用户需要了解PCIE协议,至少了解TLP报文的构造,如下图所示为32位地址写请求TLP报文:

R:保留位,一般填0;

Fmt:报文长度类型,指示当前TLP报文是3DW长度还是4DW长度(此处主要是跟地址位宽相关,PCIE协议可支持32位地址和64位地址);

Type:包类型,指示包括Mrd(读数据)、Mwr(写数据)、Cfg(配置PCIe)、Msg(消息事务)、Cpl(读地址数据请求后返回的数据包);

TC:传输优先级,数值越大表示优先级越高;

Attr:包属性,指示当前包是顺序或者是乱序,cache一致性等;

TH:PCIe V2.1 总线规范引入的一个重要功能。TLP 的发送端可以使用 TPH 信息,通知接收端即将访问数据的特性,以便接收端合理地预读和管理数据,一般很少应用;

TD:指示接收端是否需要做ECRC校验;

EP:指示当前TLP包的有效性;

AT:地址种类,与 PCIe 总线的地址转换相关;

Length:指示TLP长度;

Requester ID:请求者ID,包括PCIe设备的总线号(Bus Number)、设备号(Device Number)和功能号(Function Number),通过该ID可以找到对应的目标设备;

Tag:数据包标签,可以指示当前TLP数据包是属于哪一组数据中分拆的数据块;

Last DW BE:指示最后一个DW中有效的字节,主要是针对在传输数据粒度比较小的情况,比如最小粒度为1字节;

1st DW BE:指示第一个DW中有效的字节。

1.3 PCIE IP逻辑设计

用户在实现PCIE数据传输功能时可通过上图中AXI CQ,CC,RQ,RC四个接口来完成各种PCIE事务的数据收发:

RQ:请求者请求接口,通常是主机向终端设备发送数据传输请求;

RC:请求者完成接口,通常是终端设备向主机发送需要的返回数据;

CQ:完成者请求接口,通常是终端设备向主机发送数据传输请求;

CC:完成者完成接口,通常是主机向终端设备发送需要的返回数据;

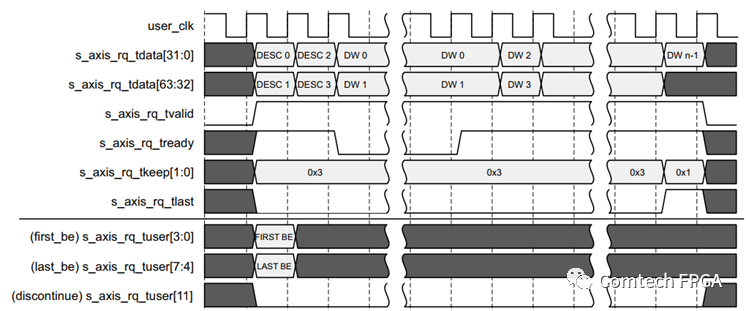

用户需要通过这4个接口构造TLP报文可以实现从主机到终端或者终端到主机的访问请求和相应的数据传输,下面是主机向终端发起写数据请求的时序:

用户在逻辑设计时可以先通过右键IP生成一个example工程,工程里面就有构造TLP报文的代码,用户可以在这个工程代码上修改TLP报文的相关数据来实现具体的数据传输需求。

二、AMD PCIE DMA功能实现

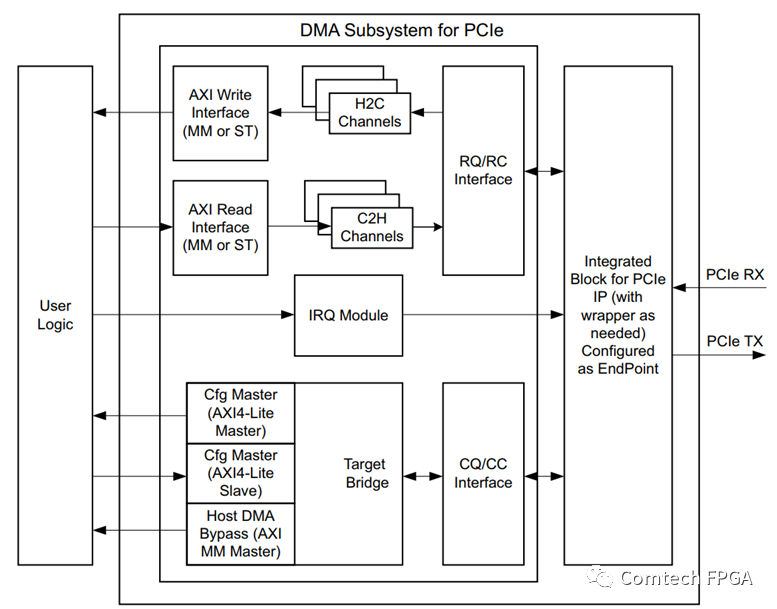

AMD PCIE DMA功能主要是通过XDMAIP来实现,其作用本质上是通过这几个接口实现PCIE DMA传输流程,用户不需要关注PCIE TLP报文的构造细节,只需要通过XDMA的AXI接口完成数据传输即可,如下图所示:

用户只需关注AXI用户接口的逻辑设计,通过该接口就可以实现DMA传输。另外,AXI用户接口包括MM接口和ST两种接口,MM接口是可以直接对接内存,其包括了地址控制,可以直接实现内存读写。

2.1 XDMA AXI-MM接口实现DMA传输

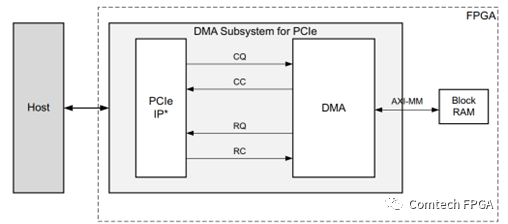

AXI-MM接口的操作相对简单,其与用户逻辑对接的接口为标准的AXI接口,包括了地址信息,可以直接对接内存,最简单的方式就是例化一个AXI接口的RAM直接对接,PC端就可以直接访问该RAM,如下图所示:

AXI-MM接口主要应用场景是直接访问FPGA内存,但对于视频流,采集数据流等场景,特别是需要用到多通道的场景通常采用ST接口会更加方便。 2.2 XDMA ST接口实现DMA传输

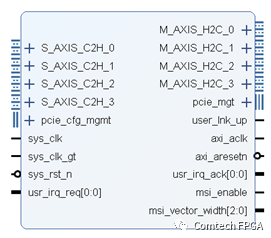

ST(AXI4-Stream)接口是实现数据流传输接口,用于传输连续的数据流,比如视频数据流,特别是在实现多通道DMA的情况下通常会采用该接口,如下图所示:

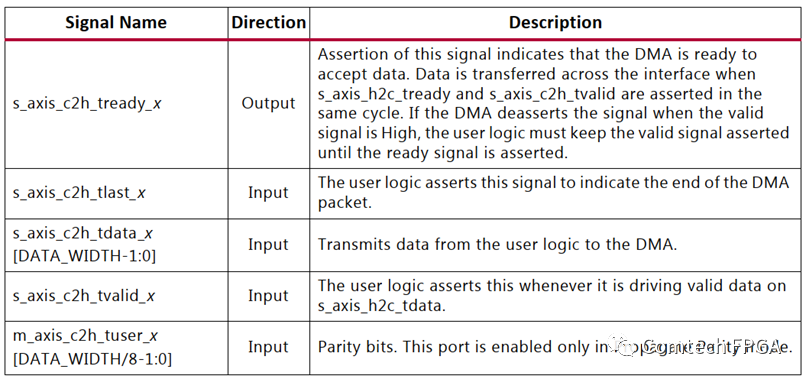

S_AXIS_C2H是终端设备向主机发送数据接口,S_AXIS_H2C是主机向终端设备发送数据接口,均为AXI Stream接口,只实现数据流传输,典型特征是不传输地址,其端口如下图所示:

其时序跟上述PCIE IP的AXI接口类似,所以,通过XDMA的ST接口可以很方便实现数据流传输,只需要跟PC驱动程序配对好地址和长度信息,逻辑设计只需要通过ST接口收发数据。 2.3 DMA逻辑设计方法

逻辑与主机上层软件实现DMA数据传输主要有查询和中断两种方式,以ST接口为例,逻辑可以通过AXI LITE接口实现PC的寄存器访问,PC可以通过查询寄存器来确定是否可以启动DMA下发数据,或者通过发起DMA获取逻辑需要上传的数据,逻辑根据当前数据需要上传或者允许PC下发数据的具体情况来设置寄存器的状态。

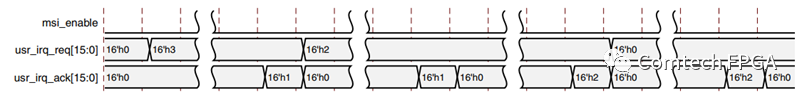

中断模式首先要在例化XDMA IP时要选择一个中断,IP自动生成一个可供用户产生中断的接口,时序如下图所示:

用户产生中断的方法很简单,只需要拉高usr_irq_req,等待usr_irq_ack拉高即可产生中断。需要注意的是当usr_irq_ack拉高时用户不能立刻把usr_irq_req拉低,因为此刻不能确定PC已经响应并完成中断处理,最简单的方式是设置一个清中断寄存器,PC通过向这个寄存器写1来通知逻辑,中断事务已经被处理完成。

另外,PCIE协议支持3种中断:

INTx中断:主要是为了兼容PCI设备,是电平触发中断;

MSI中断:消息中断,PCIE设备通过构造对应的中断消息发送到主机,从而触发中断;

MSI-X中断:是MSI中断的扩展,可以通过中断向量表的方式把中断个数扩展到2048个;

当PC启动DMA下发数据时,XDMA IP会通过H2C接口向逻辑发送数据,逻辑可以通过s_axis_h2c_tready信号来决定是否允许数据下发;当逻辑向PC上传数据时可通过C2H接口向PC传输数据,在发送数据前逻辑需要向PC产生一个中断,PC检测到中断后就会启动DMA上传数据,逻辑侧看到的是s_axis_c2h_tready信号拉高,说明逻辑可以开始通过C2H接口发送数据给PC。所以,整个DMA传输都是由PC发起的,无论是上传还是下发数据,逻辑只是被动完成数据传输。

值得注意的是当使用多通道DMA时每个通道的操作是完全独立的,包括ST接口和中断都是独立的,相关的寄存器用户最好也采用独立的寄存器来实现与PC的交互。

审核编辑:汤梓红

-

FPGA

+关注

关注

1629文章

21729浏览量

603047 -

amd

+关注

关注

25文章

5466浏览量

134109 -

接口

+关注

关注

33文章

8580浏览量

151037 -

PCIe

+关注

关注

15文章

1235浏览量

82596 -

dma

+关注

关注

3文章

561浏览量

100553

原文标题:基于AMD FPGA的PCIE DMA逻辑实现

文章出处:【微信号:Comtech FPGA,微信公众号:Comtech FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

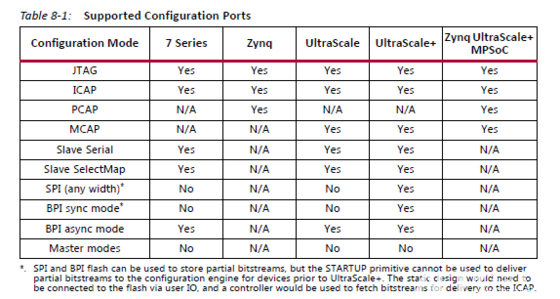

基于PCIE(mcap)的部分可重构实现方案

基于Xilinx V6的PCIE DMA高速传输模块

Xilinx PCIe Master DMA设计

PCIe DMA设计实现

关于PCIE DMA操作的一个疑问

寻求fpga大牛开发一个简单的fpga pcie设备

如何通过PCIe进行FPGA到PC的通信?

如何利用PCIe DMA总线实现一个基于FPGA的PCIe 8位数据采集卡?

基于FPGA的PCIe总线接口的DMA控制器的实现并进行仿真验证

PCIe控制器(FPGA或ASIC),PCIe-AXI-Controller

Xilinx高性能PCIe DMA控制器IP,8个DMA通道

基于AMD FPGA的PCIE DMA逻辑实现

基于AMD FPGA的PCIE DMA逻辑实现

评论