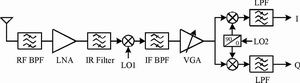

本应用笔记介绍了压控振荡器(VCO)的槽路设计方法,并给出了常用的中频(IF) 130MHz、165MHz、380MHz压控振荡器的设计实例。这些设计减少了为优化设计而进行的重复工作,具体分析可借助一个简单的电子表格实现。

VCO设计

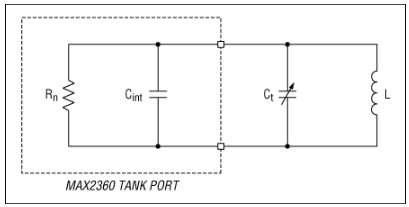

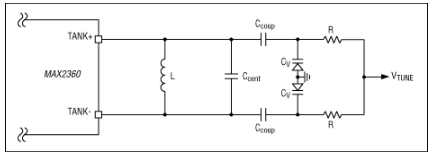

图2表示MAX2360 IF VCO的差分槽路,为便于分析,所给槽路只是一个简单的等效模型。图1表示基本的VCO模型,振荡频率由式1表示:

fosc= 振荡频率

L = 槽路线圈的电感值

Ct = 槽路的总计等效电容

图1. 基本的VCO模型

Rn = MAX2360槽路端口的等效负阻

Cint = MAX2360槽路端口的内部电容

Ct = 槽路的总计等效电容

L = 槽路线圈的电感值

图2. MAX2360槽路

电感L与槽路等效电容和振荡器内部电容的总和产生谐振(Ct + Cint) (参见图1)。Ccoup提供隔直流、并将变容二极管的可变电容耦合至槽路。Ccent用来确定槽路振荡频率标称值的中心。它不是必须的,但为在不同的电感量之间调谐谐振腔提供了便利条件。电阻(R)通过调谐电压(Vtune)为变容二极管提供相反的偏置。应选择足够大的阻值,以保证加载后的槽路Q值不受影响;另外,还要保证电阻值足够小,使4kTBR噪声可以忽略。电阻的噪声电压受Kvco调制后将产生相位噪声。电容CV是槽路内部的可变调谐元件,变容二极管的电容(CV)是反向偏置电压的函数(变容二极管模型参见附录A)。Vtune是来自锁相环(PLL)的调谐电压。

图3在VCO模型中增加了Cstray,寄生电容和寄生电感使所有射频(RF)电路的罪魁祸首,为估算振荡频率必须考虑寄生参数。图3用电容Cstray表示寄生元件,振荡频率可由式2表示:

L = 槽路线圈的电感值

Cint = MAX2360槽路端口的内部电容

Ccent = 用于确定中心振荡频率的槽路电容

Cstray = 电容漂移

Ccoup = 槽路电容,用来将变容二极管耦合至槽路

CV = 变容二极管电容的净变量(包括串联电感)

Cvp = 变容二极管焊盘的电容

图3. Cstray模型

图4表示VCO模型的详细电路,它考虑了焊盘的等效电容,但为简便起见没有考虑串联电感。Cstray定义为:

|

EQN3 |

CL= 电感的电容量

CLP = 电感焊盘的电容量

CDIFF = 平行引线的等效电容

Rn = MAX2360槽路端口的等效负阻

Cint = MAX2360槽路端口的内部电容

LT = 电感槽路引线的串联电感

CDIFF = 平行引线的等效电容

L = 槽路线圈电感

CL = 电感等效电容

CLP = 电感焊盘等效电容

Ccent = 用于确定中心振荡频率的槽路电容

Ccoup = 槽路电容,用来将变容二极管耦合至槽路

Cvar = 变容二极管电容的变化量

Cvp = 变容二极管焊盘电容

LS = 变容二极管串联电感

R = 变容二极管反向偏置电阻的阻值

为简化分析,设计中忽略了电感LT。LT 通常对高频端影响较大,为了用下面的电子表格描述LT所产生的频率偏差的数学模型,可适当增大CDIFF,减小LT以避免产生所不希望的串联谐振。这一点可通过缩短引线实现。

调谐增益

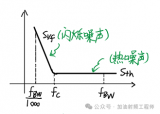

为获得最佳的闭环相位噪声特性应尽可能降低调谐增益(Kvco),环路滤波器的电阻和电阻“R” (图2)会产生宽带噪声,宽带热噪声(

)将按照Kvco调制VCO输出,用单位MHz/V表示。减小Kvco的途径有两条:一是降低压控振荡器的调谐范围;第二种方法是增大所允许的调节电压范围。要在保证足够的VCO调谐频率范围的前提下减小其调谐范围,需要选用容差极小的元器件,后面将对这一点作详细描述。为扩大电压调节范围,需采用电荷泵电路以提供适当的电压范围,这种方式一般需要采用更高的Vcc。MAX2360允许的电压调节范围是:0.5V至Vcc-0.5V。电池供电应用中,电压调节范围受电池电压或稳压器的制约。

免调节设计的基本概念

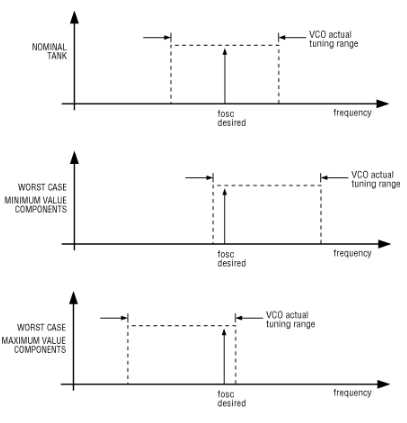

VCO槽路设计中需对实际部件进行误差分析,为了设计一个振荡在固定频率(fosc)的VCO,必须考虑元件误差。在设计调谐增益(Kvco)时必须将这些元件容差考虑进去。元件容差越小、可能产生的调谐增益越小,闭环相位噪声就越低。考虑误差最大的情况,可以用以下三种VCO模型表示:

1. 元件最大值(式5)

2. 标准谐振电路,对应于元件标称值(式2)

3. 元件最小值(式4)

三种VCO模型都必须覆盖所期望的标称频率,图5描述了如何将三种设计统一起来,以便提供可行的设计方案。从式1和图5可以看出:元件最小值对应于振荡频率的高频端偏移,而元件最大值对应于振荡频率的低频端偏移。

图5. 极端情况下的槽路中心频率和标称中心频率

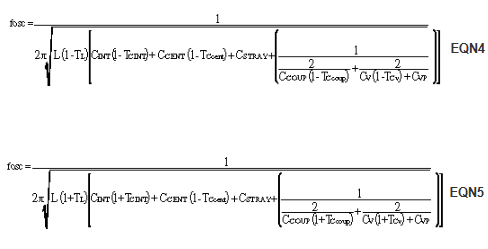

为保证槽路的闭环相位噪声最小,需尽可能减小调谐范围。但要注意在考虑系统最大容差时仍能覆盖标准振荡频率。元件值分别达到最大和最小时,槽路的调谐范围尽量靠近所期望的振荡频率的边沿,考虑到系统容差对式2加以修正,可得最大误差时对应的振荡频率式5:

TL = %电感(L)的容差

TCINT= %电容(CINT)的容差

TCCENT = %电容(C

CENT)的容差

TCCOUP = %电容(CCOUP)的容差

TCV = %变容二极管电容(CV)的容差

式4和式5假设偏差量没有容差。

一般设计过程

步骤1

估算或测量焊点的寄生电容或其它寄生电容:用Boonton 72BD电容计对MAX2360评估板进行测试,测得寄生电容为:CLP = 0.981pF、CVP = 0.78pF、CDIFF = 0.118pF。

步骤2

确定电容Cint:这个参数在MAX2360/MAX2362/MAX2364数据资料的第5页查找到,谐振端口的1/S11随频率变化的典型工作特性给出了几个常用频点时的等效并联RC参数,附录B包含了槽路端口频率在高频端和低频端时Cint与频率的对应关系表。需要牢记的是本振频率为IF频率的两倍。

例如:

如果IF为130MHz,本振工作频率为260MHz。由1/s11图表可得Rn = -1.66kΩ、Cint = 0.31pF。

步骤3

选择电感:最好从几何平均值入手,这是一个需要重复迭代的过程。

上式中电感、电容的单位分别用nH、pF表示(1x10-9 x 1x10-12 = 1x10-21)。如果fosc = 260.76MHz、L = 19.3nH,则槽路总计电容为C = 19.3pF。最初选择容差为2%、电感量为18nH的Coilcraft 0603CS-18NXGBC比较恰当。

如果选择电感具有一定的局限性时,式6.1将是一个很有用的公式。对于一个固定振荡频率fosc,LC的乘积应保持恒定。

|

EQN6.1 |

fosc = 260.76MHz时,LC = 372.5,按照表1采用试凑的方法可以得到:电感取39nH、容差为5%,而槽路总电容为9.48pF。此时,图6中LC乘积为369.72,非常接近理论值372.5。由此可以看出上述关系时的实用性。为保证较低的相位噪声,选用高Q值电感,如:Coilcraft 0603CS系列,如果能够合理控制微带线的容差和Q值,也可选用微带线。

图6. 130.38MHz IF槽路

步骤4

确定锁相环(PLL)的合理范围:该参数表示VCO整个调谐电压(Vtune)的工作范围,对于MAX2360,适当范围为:0.5V至VCC-0.5V,如果VCC = 2.7V,则调谐电压范围为:0.5V至2.2V,电荷泵输出限定这一范围。槽路电压摆幅为1VP-P、电压摆幅的中点为1.6V直流,即使选用较大的Ccoup,变容二极管也不会产生正偏。这是一个需要避免的情况,因为二极管将会影响槽路引脚上的交流信号,产生所不期望的杂散响应、造成闭环PLL的失锁。

步骤5

选择变容二极管,在所规定的调谐电压范围内选择容差较小的变容二极管,并保证串联电阻最小,确认变容二极管的自共振频率高于所期望的工作频率。在规定的工作电压范围内察看CV(2.5V)/CV(0.5V)的比率。如果选择较大的耦合电容Ccoup,最大调谐范围可利用式2计算;如果选择较小的耦合电容Ccoup,将会降低有效的频率调谐范围。选择变容二极管时需给出调谐范围的中点和端点处的容差,可以选择一个特性曲线较陡峭的变容二极管,如Alpha SMV1763-079,进行线性调节。取槽路总电容、并将其用于变容二极管的Cjo。注意,Ccoup会降低变容二极管耦合到槽路的电容。

步骤6

确定耦合电容Ccoup:Ccoup较大时,变容二极管耦合到槽路的电容较大、使调谐范围增大,但会降低槽路加载后的Q值。Ccoup较小时,会提高耦合变容二极管的Q值和加载后的Q值,但它是以减小调谐范围为代价的。通常是在保证调谐范围的前提下尽可能选择小的容量值。选择较小Ccoup的另一个好处是可以降低变容二极管两端的电压摆幅。

步骤7

确定电容Ccent。一般Ccent取2pF,考虑到电容误差也可选用稍微大一点的电容。利用Ccent调整VCO的标准频率。

步骤8

按照制作的电子表格推敲设计参数。

MAX2360在130.38MHz、165MHz和380MHz IF时的VCO槽路设计

下列电子表格给出了MAX2360在几个通用IF频点的设计,请牢记:LO振荡频率应为所期望的IF频率的两倍。

| 浅灰色代表计算值 |

| 深灰色代表用户的输入参数 |

表1. 130.38MHz IF槽路设计

| MAX2360 Tank Design and Tuning Range for 130.38MHz IF Frequency | |||||

| Total Tank Capacitance vs. V tune | |||||

| V tune | Total C |

Ct (Nominal) |

Ct (Low) |

Ct (High) |

|

| 0.5V | Ct high | 10.9296pF | 10.1242pF | 11.6870pF | |

| 1.375V | Ct mid | 9.4815pF | 8.4068pF | 10.4077pF | |

| 2.2V | Ct low | 8.0426pF | 6.9014pF | 9.0135pF | |

| Tank Components | Tolerance | ||||

| Ccoup | 18pF | 0.9pF | 5% | ||

| Ccent | 2.7pF | 0.1pF | 4% | ||

| Cstray | 0.69pF | ||||

| L | 39nH | 5.00% | |||

| Cint | 0.31pF | 10.00% | |||

| Parasitics and Pads (C stray) | |||||

| Due to Q | CL | 0.08pF | |||

| Ind. pad | CLp | 0.981pF | |||

| Due to || | Cdiff | 0.118pF | |||

| Var. pad | Cvp | 0.78pF | |||

| Varactor Specs | |||||

| Alpha SMV1255-003 | |||||

| Cjo | 82pF | Varactor Tolerance | |||

| Vj | 17V | 0.5V | 19.00% | ||

| M | 14 | 1.5V | 29.00% | ||

| Cp | 0pF | 2.5V | 35.00% | ||

| Rs | 1Ω | Reactance | |||

| Ls | 1.7nH | XLs | 2.79 | ||

| Freq | 260.76MHz | ||||

| Nominal Varactor | X c | NetCap | |||

| Cvhigh | 54.64697pF | -11.16897 | 72.80216pF | ||

| Cvmid | 27.60043pF | -22.11379 | 31.57772pF | ||

| Cvlow | 14.92387pF | -40.89758 | 16.01453pF | ||

| Negative Tol Varactor (Low Capacitance) | |||||

| Cvhigh | 44.26404pF | -13.78885 | 55.46841pF | ||

| Cvmid | 19.59631pF | -31.14619 | 21.52083pF | ||

| Cvlow | 9.700518pF | -62.91935 | 10.14983pF | ||

| Positive Tol Varactor (High Capacitance) | |||||

| Cvhigh | 65.02989pF | -9.385688 | 92.47168pF | ||

| Cvmid | 35.60456pF | -17.14248 | 42.51182pF | ||

| Cvlow | 20.14723pF | -30.2945 | 22.18712pF | ||

|

Nominal LO (Nom) Range |

Low Tol IF (High) Range |

Nominal IF (Nom) Range |

High Tol IF (Low) Range |

||

| Flow | 243.77MHz | 129.93MHz | 121.89MHz | 115.03MHz | |

| Fmid | 261.73MHz | 142.59MHz | 130.86MHz | 121.90MHz | |

| Fhigh | 284.18MHz | 157.37MHz | 142.09MHz | 130.98MHz | |

| BW | 40.40MHz | 27.44MHz | 20.20MHz | 15.95MHz | |

| % BW | 15.44% | 19.24% | 15.44% | 13.09% | |

| Nominal IF Frequency | 130.38MHz | ||||

| Design Constraints | |||||

| Conditionfor boldnumber | =IF | > IF | |||

| Delta | 0.45 | -0.48 | 0.60 | ||

| Test | pass | pass | pass | ||

| Raise or lower cent freq by | -0.48 | MHz | |||

| Inc or dec BW | -1.05 | MHz | |||

| Cent adj for min BW | 130.46 | MHz | |||

| K vco | 23.77MHz/V | ||||

图7. 165MHz IF槽路

| 浅灰色代表计算值 |

| 深灰色代表用户的输入参数 |

表2. 165MHz IF槽路设计

| MAX2360 Tank Design and Tuning Range for 165MHz IF Frequency | |||||

| Total Tank Capacitance vs. V tune | |||||

| V tune | Total C |

Ct (Nominal) |

Ct (Low) |

Ct (High) |

|

| 0.5V | Ct high | 10.0836pF | 9.2206pF | 10.8998pF | |

| 1.375V | Ct mid | 8.5232pF | 7.3878pF | 9.5095pF | |

| 2.2V | Ct low | 7.0001pF | 5.8130pF | 8.0193pF | |

| Tank Components | Tolerance | ||||

| Ccoup | 18pF | 0.9pF | 5% | ||

| Ccent | 1.6pF | 0.1pF | 6% | ||

| Cstray | 0.62pF | ||||

| L | 27nH | 5.00% | |||

| Cint | 0.34pF | 10.00% | |||

| Parasitics and Pads (C stray) | |||||

| Due to Q | CL | 0.011pF | |||

| Ind. pad | CLp | 0.981pF | |||

| Due to || | C diff | 0.118pF | |||

| Var. pad | Cvp | 0.78pF | |||

| Varactor Specs | |||||

| Alpha SMV1255-003 | |||||

| Cjo | 82pF | Varactor Tolerance | |||

| Vj | 17V | 0.5V | 19.00% | ||

| M | 14 | 1.5V | 29.00% | ||

| Cp | 0pF | 2.5V | 35.00% | ||

| Rs | 1ohm | Reactance | |||

| Ls | 1.7nH | XLs | 3.52 | ||

| Freq | 330.00MHz | ||||

| Nominal Varactor | Xc | NetCap | |||

| Cvhigh | 54.646968pF | -8.8255163 | 90.986533pF | ||

| Cvmid | 27.600432pF | -17.473919 | 34.574946pF | ||

| Cvlow | 14.923873pF | -32.316524 | 16.750953pF | ||

| Negative Tol Varactor (Low Capacitance) | |||||

| Cvhigh | 44.264044pF | -10.895699 | 65.431921pF | ||

| Cvmid | 19.596307pF | -24.611153 | 22.872103pF | ||

| Cvlow | 9.7005176pF | -49.717729 | 10.440741pF | ||

| Positive Tol Varactor (High Capacitance) | |||||

| Cvhigh | 65.029892pF | -7.4164003 | 123.93257pF | ||

| Cvmid | 35.604558pF | -13.545673 | 48.128632pF | ||

| Cvlow | 20.147229pF | -23.938166 | 23.626152pF | ||

|

Nominal LO (Nom) Range |

Low Tol IF (High) Range |

Nominal IF (Nom) Range |

High Tol IF (Low) Range |

||

| Flow | 305.02MHz | 163.63MHz | 152.51MHz | 143.15MHz | |

| Fmid | 331.77MHz | 182.81MHz | 165.88MHz | 153.26MHz | |

| Fhigh | 366.09MHz | 206.08MHz | 183.04MHz | 166.90MHz | |

| BW | 61.07MHz | 42.45MHz | 30.53MHz | 23.74MHz | |

| % BW | 18.41% | 23.22% | 18.41% | 15.49% | |

| Nominal IF Frequency | 165MHz | ||||

| Design Constraints | |||||

| Conditionfor boldnumber | < IF | = IF | > IF | ||

| Delta | 1.37 | -0.88 | 1.90 | ||

| Test | pass | pass | pass | ||

| Raise or lower cent freq by | -0.88 | MHz | |||

| Inc or dec BW | -3.26 | MHz | |||

| Cent adj for min BW | 165.26 | MHz | |||

| K vco | 35.92MHz/V | ||||

图8. 380MHz IF槽路

| 浅灰色代表计算值 |

| 深灰色代表用户的输入参数 |

表3. 380MHz IF槽路设计

| MAX2360 Tank Design and Tuning Range for 380MHz IF Frequency | |||||

| Total Tank Capacitance vs. V tune | |||||

| V tune | Total C |

Ct (Nominal) |

Ct (Low) |

Ct (High) | |

| 0.5V | Ct high | 6.9389pF | 6.6119pF | 7.2679pF | |

| 1.35V | Ct mid | 6.2439pF | 5.9440pF | 6.5449pF | |

| 2.2V | Ct low | 5.7813pF | 5.5040pF | 6.0593pF | |

| Tank Components | Tolerance | ||||

| Ccoup | 15pF | 0.8pF | 5% | ||

| Ccent | 2.4pF | 0.1pF | 4% | ||

| Cstray | 1.42pF | ||||

| L | 6.8nH | 2.00% | |||

| Cint | 0.43pF | 10.00% | |||

| Parasitics and Pads (C stray) | |||||

| Due to Q | CL | 0.08pF | |||

| Ind. pad | CLp | 0.981pF | |||

| Due to || | Cdiff | 0.85pF | |||

| Var. pad | Cvp | 0.78pF | |||

| Varactor Specs | |||||

| Alpha SMV1255-003 | |||||

| Cjo | 8.2pF | Varactor Tolerance | |||

| Vj | 15V | 0.5V | 7.50% | ||

| M | 9.5 | 1.5V | 9.50% | ||

| Cp | 0.67pF | 2.5V | 11.50% | ||

| Rs | 0.5Ω | Reactance | |||

| Ls | 0.8nH | XLs | 3.82 | ||

| Freq | 760.00MHz | ||||

| Nominal Varactor | X c | Net Cap | |||

| CVhigh | 6.67523pF | -31.37186 | 7.600784pF | ||

| CVmid | 4.286281pF | -48.8569 | 4.649858pF | ||

| CVlow | 2.904398pF | -72.10251 | 3.06689pF | ||

| Negative Tol Varactor (Low Capacitance) | |||||

| CVhigh | 6.174588pF | -33.91552 | 6.958364pF | ||

| CVmid | 3.879084pF | -53.98553 | 4.174483pF | ||

| CVlow | 2.570392pF | -81.47176 | 2.696846pF | ||

| Positive Tol Varactor (High Capacitance) | |||||

| CVhigh | 7.175873pF | -29.18313 | 8.256705pF | ||

| CVmid | 4.693477pF | -44.61818 | 5.132957pF | ||

| CVlow | 3.238404pF | -64.66593 | 3.441726pF | ||

|

Nominal LO (Nom) Range |

Low Tol IF (High) Range |

Nominal IF (Nom) Range |

High Tol IF (Low) Range |

||

| Flow | 732.69MHz | 379.11MHz | 366.35MHz | 354.43MHz | |

| Fmid | 772.40MHz | 399.84MHz | 386.20MHz | 373.50MHz | |

| Fhigh | 802.70MHz | 415.51MHz | 401.35MHz | 388.17MHz | |

| BW | 70.00MHz | 36.41MHz | 35.00MHz | 33.74MHz | |

| % BW | 9.06% | 9.11% | 9.06% | 9.03% | |

| Nominal IF Frequency | 380MHz | ||||

| Design Constraints | |||||

| Conditionfor boldnumber | < IF | = IF | > IF | ||

| Delta | 0.89 | -6.20 | 8.17 | ||

| Test | pass | pass | pass | ||

| Raise or lower cent freq by | -6.20 | MHz | |||

| Inc or dec BW | -9.07 | MHz | |||

| Cent adj for min BW | 383.64 | MHz | |||

| K vco | 41.18MHz/V | ||||

附录A

图9. 变容二极管模型

Alpha应用笔记AN1004对变容二极管模型提供了更多信息。变容二极管电容定义为式7:

|

EQN7 |

| Alpha SMV1255-003 | Alpha SMV1763-079 |

| Cjo = 82 pF | Cjo = 8.2 pF |

| Vj =17 V | Vj =15 V |

| M = 14 | M = 9.5 |

| Cp = 0 | Cp = 0.67 |

| Rs = 1Ω | Rs = 0.5Ω |

| Ls = 1.7 nH | Ls = 0.8 nH |

变容二极管串联电感可以用反向输出的感抗表示,计算新的等效电容CV为:

|

EQN8 |

审核编辑:郭婷

-

二极管

+关注

关注

147文章

9639浏览量

166493 -

振荡器

+关注

关注

28文章

3832浏览量

139090 -

VCO

+关注

关注

12文章

190浏览量

69194

发布评论请先 登录

相关推荐

零中频接收机设计

零中频射频接收机威廉希尔官方网站

什么是零中频威廉希尔官方网站

SAW Filter在零中频接收机中的角色扮演

基于多相滤波的宽带中频正交采样数字零中频接收方案

MAX2360的中频谐振箱设计

射频架构之零中频架构威廉希尔官方网站 解析

为什么窄信道带宽接收机偏向采用低中频而不是零中频架构呢?

MAX2360中频槽路设计

MAX2360中频槽路设计

评论