一. 前言

前面的文章https://mp.weixin.qq.com/s/wC79XEXMAK-3SGX8JkrFKw,完整的介绍了PSRAM的相关内容,比如接口时序等,但是该文章内容较多,需要花费一些时间慢慢阅读。对于一些开发人员可能只是想大概了解一下PSRAM的关键信息点,或者说遇到问题了不知如何查起,想直接看看有没有一些常见的坑,来对照排查自己的问题,本文就是针对此而写。本文重点介绍PSRAM时序中几个关键的点,也是没有调试过PSRAM的开发人员可能会理解错误的点,以及时序的training算法等。每一个知识点都是从工程实践出发,都是真金白银的干货,基本上这一些信息就包括了可能遇到的大部分问题了,先看这篇文章,基本就能避免各种坑了。

注意以下以APS256XXN为例,其他芯片不排除略有差异,但是关键时序不会有差异都是一样的。

二.PSRAM关键知识点

2.1 总线宽度

默认是x8模式,可以通过寄存器修改为x16模式。

但是命令字和地址的发送始终是8位模式的,不过抓包可以看到此时高8位内容会和低8位的内容完全一样。

2.2 地址空间

对于x16模式,因为其单位是x16bits即2B,所以页内偏移地址即列地址,只需要CA[9:0]10位就足够,可以表示2048字节,而x8模式需要CA[10:0]11位表示2048字节,行地址则不管是x8还是x16都是RA[13:0]。

又由于是DDR模式,即双边沿都传输数据,所以数据的最小传输单位是一个CLK,一个CLK就对应两个总线宽度,对于x8模式是2B,对于x16模式就是4B,所以x8和x16模式最小的数据传输大小就是2B和4B,即列地址的bit0 CA[0]必须始终是0。

寄存器操作没有以上限制可以从任意寄存器开始,但是也要注意由于是DDR所以一个CLK,PSRAM会发出连续两个寄存器的值,CLK不停则连续的两个寄存器重复发出。

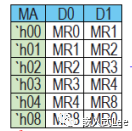

即对应下表

比如读MA0则依次返回MR0和MR1,CLK不停则MR0和MR1重复返回.

2.3 命令地址的锁存

在CE#变为LOW之后,指令字节在CE#拉低后**第一****个** **CLK上升沿被锁存** **,** 注意这里是第一个上升边沿,如果CE#拉低后首先出现的是CLK的下降沿则这个下降沿会略过,也是没问题的。

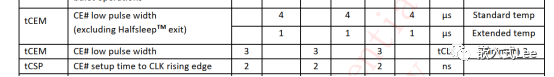

按照时序要求,指令字节需要一直保持到第一个CLK上升沿之后的下降沿,然后保持一个保持时间tHD,但是实际测试可能只需要保持到第一个CLK上升沿并且保持保持时间tHD就就够了。实际应用还是建议完全按照手册要求来,一直保持到下降沿之后的保持时间,这样确保安全。这里还要注意CE#拉低到CLK拉高有一个最小的tCSP时间(2nS)要求,还有CLK上升沿之前数据的最小建立时间tSP。

如下所示

地址在第三、第四、第五和第六CLK边沿(第二CLK上升沿、第二CLK下降沿、第三CLK上升边沿、第三CL下降沿)被锁存,以上边沿计数是从CE#拉低之后的CLK上升沿开始作为第一个CLK边沿计数。

如下是一个实际的应用中抓取到的波形,CE#拉低之后首先出现的是CLK的下降沿,这也是没问题的

2.4 写数据-DM

注意DM和DQS是复用的,都是发送方驱动,但是DQS和DM的含义完全是不一样的。

DQS是读数据时PSRAM驱动,用于表示数据就绪,控制器这边根据DQS的边沿延迟一定时间进行数据采样。

而控制器发送数据,PSRAM并不是通过DM来采样的,DM表示的是数据是否MASK掉,PSRAM是通过CLK的边沿来采样的,CLK的边沿采样再来结合此时DM电平表示对应的字节是否要写入,如果DM为高则MASK掉指定字节不写入。

所以结合DM可以实现单字节的写入。

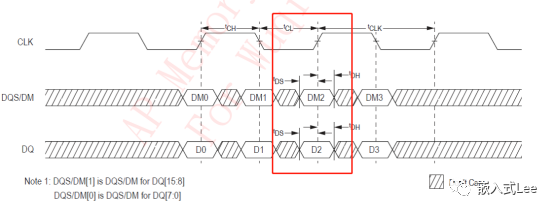

由于写数据时是CLK边沿采样,且DM和数据是同时变化的,要相对CLK的边沿有数据建立时间和保持时间分别是tDS,tDH。

如图所示

2.5 读数据-DQS

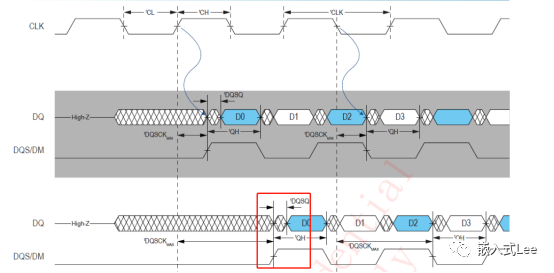

注意读数据不一样不再通过CLK的边沿锁存数据,而是通过DQS来锁存数据了。

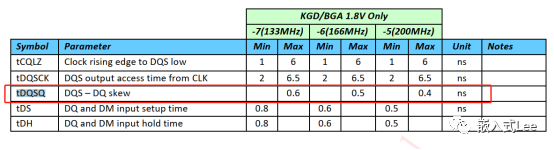

读数据时PSRAM同时更新DQS和总线信号,但是两者信号类型不一样,一个是时钟信号一个是总线数据信号,所以其物理上经过的路径就是不一样的,到达引脚时存在时间差,这个时间差就是tDQSQ,比如对于166MHz这个值就是最大不超过0.5nS,所以接收方需要在DQS的边沿延时该时间之后再采样才能保证采样到正确的数据。大部分读不到数据基本都是接收方这个时间设置不对,正常来说接收方会有一个PHY可以通过寄存器配置该时间,接收training也就是不断调整该时间然后确定一个合适的中间的值。

2.6 x8和x16的存储映射

不管是x8还是x16模式页的大小都是2K,但是x8模式和x16模式数据在页内的放置是不一样的。

X8模式按照字节序列写入页内的0~2047字节

X16模式则1字节写入页内的01022处,另外字节写入页内的10232047处。

所以要注意如果动态切换模式,则读出的数据内容就不一样了。

2.7 读写数据的长度

普通模式读写数据最长由Burst Type决定,不能超过一个PAGE的大小;

写最小长度是一个CLK对应的长度,x8模式就是一个CLK两个边沿2字节,X16模式就是一个CLK两个边沿2x2=4字节;读没有最小长度限制。写数据可以结合DM来MASK写入单字节,而读数据没有MASK。读写数据的开始地址和长度要是2(x8)或者4(x16)字节对齐。

读写数据如果是使能了RXB且使用Linear Burst 读写模式则理论上读写最长字节数没有限制,但是要受限于tCEM即CE拉低的时间限制

对于标准温度最长CE可以拉低4uS,如果算200MHz时钟,4uS有 800个CLK,不考虑命令地址,延迟等时间,800个CLK最多可以传输800x2x2个字节。

如果是扩展温度1uS,算200MHz时钟,4uS有200个CLK,不考虑命令地址,延迟等时间,200个CLK最多可以传输200x2x2个字节。

所以也不多,一般都是一次传输读写256个字节。

2.8 training

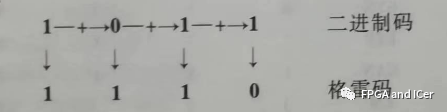

所谓的training就是针对读和写两个关键的时序参数来进行

读即DQS延迟tDQSQ时间之后再进行采样

写即数据在CLK边沿tDS之前建立,都是数据建立时间的概念。

根本原因是因为时钟信号和数据总线信号走的路径不一样,所以出现在引脚上的时刻也不一样(内部逻辑电路是时序逻辑电路都是在时钟的边沿进行数据更新的,理论上数据源是同步的)。

对于发送时,控制器的逻辑电路修改数据是在CLK边沿进行的,但是传播到引脚上时数据较CLK延后了,哪怕不延后数据也最多只能和时钟保持同步,不能满足数据建立时间要求,所以就要人为的在CLK的输出路径上加上延迟,以满足建立时间的要求。

对于接收,同样的道理,数据在出现在引脚上时已经滞后DQS了,这个时间就是tDQSQ,所以不能DQS边沿采样了,需要延迟一段时间采样,所以需要在DQS的输入路径上人为的添加延迟。

这两个延迟是由PHY去控制的,会提供寄存器接口给软件控制,软件就是控制这两个延迟时间来进行training。

所谓的training就是,不断尝试读写,通过判断读是否正确,来判断参数是否合适,得到一个范围的参数,取中间值。修改这两个时序如果能正确读写就认为这个参数可行,然后在所有可行的参数中取中间值,以获得较高的冗余度。读写是否正确一般通过读某个有固定值的寄存器来确定。

具体算法如下:

由于有两个参数,一个决定发送,一个决定接收,由于一次传输比如读寄存器,需要先发送命令地址,然后读,涉及到两个过程,任意一个过程错误都不能读到正确的数据。

所以两个参数都需要遍历尝试,实际就是两层嵌套遍历。

一般可以读内容是固定的寄存器,比如厂商ID对应的寄存器,假设CLK延迟参数可以配置为099,DQS延迟参数可配置为099

那么组合就有100*100次尝试,也可以增加递增间隔以减少尝试次数。

先固定CLK延迟,遍历DQS延迟,记录能读到正确数据的DQS延迟范围

再递增CLK延迟,遍历DQS延迟,记录能读到正确数据的DQS延迟范围

在所有能读到正确数据的DQS延迟范围中选择范围最宽的,取其范围的中间的DQS延迟值作为最终的DQS延迟值。

在所有能读到正确数据的CLK延迟中取中间的CLK延迟值作为最终的CLK延迟值。

三. 实测波形

如下地址有使用逻辑分析抓包的实际PSRAM读写寄存器和数据的波形记录,可以参考。

注意这些记录波形是实际测试过程中抓取的,不是最终的最好状态,不能作为标准波形参考,标准波形需要参考手册。

链接:https://pan.baidu.com/s/1HHGEvwz_NHT_tra4ONe-RQ?pwd=45b9

提取码:45b9

四. 总结

以上分享了PSRAM接口一些关键的知识点,大部分是容易理解错误,且导致问题的点,基本上理解这些点就能解决大部分问题了,作为入门参考也可以先看这篇,先有个大概了解。作为遇到问题不知如何解决时也可以参考这篇文章,基本上能解决大部分问题。

审核编辑:汤梓红

-

嵌入式

+关注

关注

5082文章

19111浏览量

304847 -

接口

+关注

关注

33文章

8580浏览量

151031 -

PSRAM

+关注

关注

0文章

35浏览量

13338 -

时序

+关注

关注

5文章

387浏览量

37319

发布评论请先 登录

相关推荐

PSRAM避坑指南-关键知识点讲解

PSRAM避坑指南-关键知识点讲解

评论