门级仿真(gate levelsimulation)也称之为后仿真,是数字IC设计流程中的一个重要步骤。

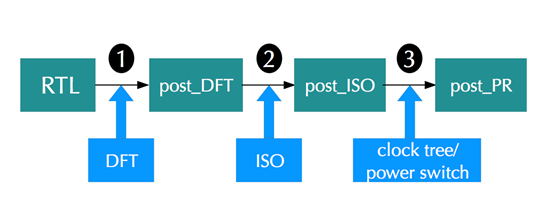

在讲解门级仿真作用之前,我们先简单来看一下数字后端的流程:

在步骤1中,会插入DFT,生成post_DFT的网表netlist;在步骤2中会根据CPF/UPF插入isolation,生成post_ISO的网表;步骤3进行后端PR,会插入clock tree以及power switch等,生成最终的post_PR的网表。

理论上每次生成新的netlist都需要重新跑门级仿真,保证功能级仿真的正确。门级仿真的时间开销很大,尤其对于规模稍大的芯片,跑完一个case经常需要几天的时间。

有人会问,综合之后都会做formal和STA,来保证网表的一致性和timing没有violation。那为什么还要做如此耗时耗力的门级仿真的。下面我们就来罗列一下门级仿真的主要作用和重点。

1 双重保险

不论是在步骤1,2,3中,插入不同的东西之后,都会改变原来的netlist,虽然会做一致性检查,但是还是需要进行功能性的门级仿真,以保证网表的正确性。

2 STA检查不到的timing问题

STA可以检查大多数的timing violation,但是也有力所不及的地方。比如:

(1)异步模块和端口的timingcheck,这一块,有很多公司其实是会做类似CDC的flow来保证异步timing的,但是在门级仿真中能更直观直接的反映出来。

(2)STA中constraint加的不足,这类情况,在analog model的情况中体现的非常明显。

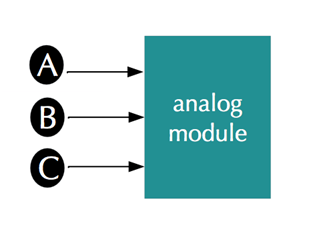

比如下图的这个情况,信号ABC是analogmode的三根输入信号,因为在RTL仿真中,A/B/C三根信号都是同时toggle的,信号进入analog的mode之后,不会出现仿真的问题。但是在后仿中,A/B/C三根信号必然不是同时toggle的,这样的信号,传入ananlogmode中就可能出现仿真的错误。

上面这种问题的解决方案是:

详细了解analogmode的需求,然后写出完善的constraints给做综合和STA。但是这些constraint总归不是100%完善的,很多时候就需要后仿来报错发现。

3 X态传播的debug

这个是门级仿真中最重要的工作之一,就是排除芯片中所有X态传播而造成的功能问题。

有人不是很理解X态的传播,我们先简单解释一下:

if(a==1) b=1;

else b=0;

如上面这段简单的代码,如果a=X态,在RTL仿真中,是不会传播出去的,因为会走else这条通路,从而b=0;但是在门级仿真中,当a=X时,b就会=X,从而X态会一级一级传播下去。

X态的传播,有些是无所谓的,有些就会影响到芯片的正常工作,尤其是在controlpath上的X态传播。而这些都只能依靠门级仿真来发现了。

当然,有很多大公司,在RTL仿真的时候,就会加入X态的interwetten与威廉的赔率体系 仿真,能提前尽早的发现这类问题。

4 验证初始化reset流程的正确性

实际芯片在刚上电的时候,理论上大多数信号都是在不确定态X态的,需要经过reset流程来进行初始化。而只有在门级仿真中,才能更加真实充分的反应reset流程的正确性。

5 power评估

门级仿真中还有一个重要作用就是用来进行power估计,因为netlist尤其是post_PR的网表能更加真实的接近实际的芯片,提供的power评估值就越有参考价值。

一般会创建一个toggle rate最高的case来跑门级仿真,从而生成IR-DROP需要的VCD文件。

6 ISO值的验证

低功耗设计在芯片设计中越来越重要,大多数芯片都会采取低功耗设计,在后端的实现中就需要插入isolation来保持一些信号在掉电状态下的值。而ISO值为0还是为1,是直接参考CPF/UPF文件来实现的。而CPF/UPF文件很多时候是直接通过review得到的。

万一在CPF/UPF中写错了,在门级仿真中就可以抓出类似的bug。

7 Power switch的验证

同样在low power设计中,powerswitchchain也是很重要的一环,而这个只有在post_PR的网表中才会真正插入。

以上只是简单罗列了一下门级仿真的作用,具体的门级仿真的操作细节和注意事项会在后续的文章中慢慢道来。这篇文章比较适合有一定工作经验但刚开始做门级仿真的朋友们,有什么问题,欢迎大家留言一起交流~

审核编辑:汤梓红

-

IC设计

+关注

关注

37文章

1281浏览量

103281 -

芯片设计

+关注

关注

15文章

960浏览量

54508 -

仿真

+关注

关注

50文章

3915浏览量

132671 -

DFT

+关注

关注

2文章

224浏览量

22542 -

数字IC

+关注

关注

1文章

37浏览量

12289

原文标题:数字IC设计流程中为什么要做门级仿真?

文章出处:【微信号:芯司机,微信公众号:芯司机】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

RTL级仿真与门级仿真

仿真软件ModelSim及其应用,ModelSim的仿真流程

芯华章发布国内首台超百亿门大容量硬件仿真系统 完备数字验证全流程工具平台

数字IC设计流程中为什么要做门级仿真?

数字IC设计流程中为什么要做门级仿真?

评论