亚稳态

在异步系统中,由于数据和时钟的关系不是固定的,因此会出现违反建立和保持时间的现象。此时会出现输出介于两个有效态的中间电平并且无法确定停留在中间态的时间,在经过一定的延迟后才能进行正常转换。这种处于中间的状态称为亚稳态。

亚稳态的产生

当违背建立,保持时间时,亚稳态就会出现,在以下情况下,可能出现亚稳态。

- 异步输入信号

- 时序违例

- 信号在不同时钟域下跨时钟域工作

- 竞争冒险

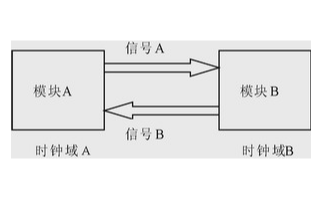

本文主要讲解信号在不同时钟域下的工作,即异步时钟的同步处理。

跨时钟域的信号同步

- 两级同步

- 握手操作

- 异步FIFO或异步双口RAM

控制信号的传输

- 两级同步

-

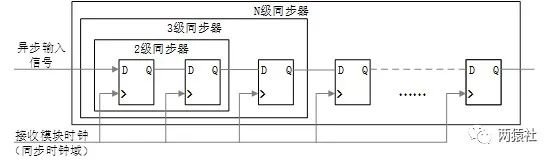

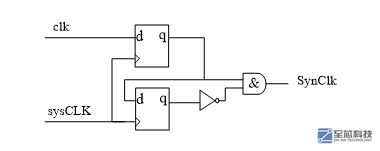

多级同步触发器是单bit数据的常见同步方式。方法是在跨时钟域的信号上加上两级或多级同步触发器。

-

两级同步器可以极大概率避免亚稳态的产生。有两个明显的缺点:

1) 输入信号必须保证宽度大于或等于1个采样时钟周期(输入信号加约束);

2) 不可避免的增加了电路的整体延时(两级同步器为2个采样时钟周期)。

-

多级同步器

两级同步器

两级同步器Verilog表示为:

1always@(posedge dest_clk) begin

2 dest_data1_in <= src_data_out;

3 dest_data2_in <= dest_data1_in;

4end

数据信号的传输

-

握手信号方法

使用握手方式是最古老的和可靠的不同时钟域的数据传输方式。

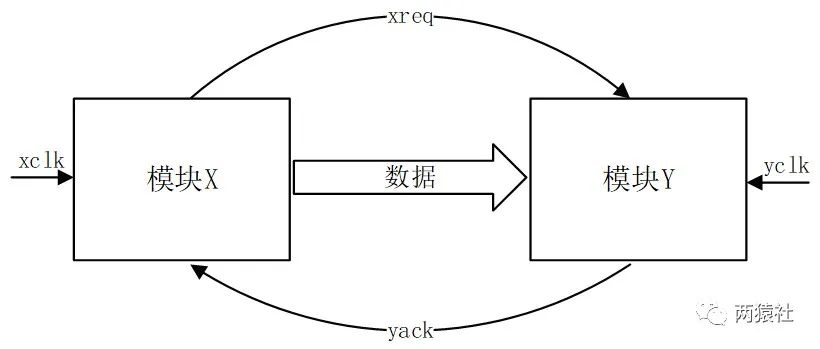

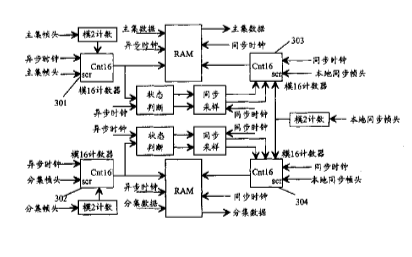

下图是由两个时钟域分割成的两个单独的模块。

跨时钟域模块

使用握手信号xack和yreq,模块X将数据发送给模块Y。下面是使用握手信号传输数据的例子。

1)模块X将数据放到数据总线上并发出xreq(请求)信号,表示有效数据已经放到数据总线上。

2)把xreq信号打两级同步到yclk时钟域。

3)模块Y在接收到xreq同步后的信号后,接收数据总线上的信号。

4)模块Y接收数据的同时发出yack(响应)信号,表示已经接收到了数据。

5)模块X接收到yack后打两级同步到xclk时钟域。

6)模块X在接收到yack同步后的信号后,使xreq无效,表示此次数据传输结束。

7)模块Y在发现xreq无效后,使yack无效。

8)模块X发现yack无效后可以进行下一笔数据传输。

优点 :不论xclk和yclk的频率如何,都可以进行数据传输。缺点 :完成数据传输的延迟比使用异步FIFO传输大得多。

-

RAM

+关注

关注

8文章

1368浏览量

114677 -

触发器

+关注

关注

14文章

2000浏览量

61148 -

FIFO存储

+关注

关注

0文章

103浏览量

5971 -

时钟域

+关注

关注

0文章

52浏览量

9536 -

异步时钟

+关注

关注

0文章

17浏览量

9404

发布评论请先 登录

相关推荐

FPGA异步时钟设计中的同步策略

异步时钟同步疑惑

异步时钟域的亚稳态问题和同步器

同步和异步时钟之间是如何联系_如何正确的约束时钟

多时钟域的同步时序设计和几种处理异步时钟域接口的方法

异步时钟的同步处理

异步时钟的同步处理

评论